一种芯片老化测试方法和测试电路与流程

- 国知局

- 2024-07-31 19:14:44

本发明实施例涉及芯片老化测试技术,尤其涉及一种芯片老化测试方法和测试电路。

背景技术:

1、随着对芯片性能的要求越来越高,更多的存储单元配置并应用到芯片,高达几百兆字节的高密度存储单元被实例化在一颗芯片设计中已经是普遍现象。为保证芯片中的存储单元以及芯片的性能,需对芯片进行老化测试。

2、目前,现有的芯片老化测试方法,在对芯片中的存储单元进行老化测试时,通常只能达到使存储单元在较长时间内反复反转的测试目的,并不能很好地控制存储单元内部的逻辑反转,会损失该部分的测试覆盖,影响测试可靠性。

技术实现思路

1、本发明实施例提供一种芯片老化测试方法和测试电路,以提高测试可靠性。

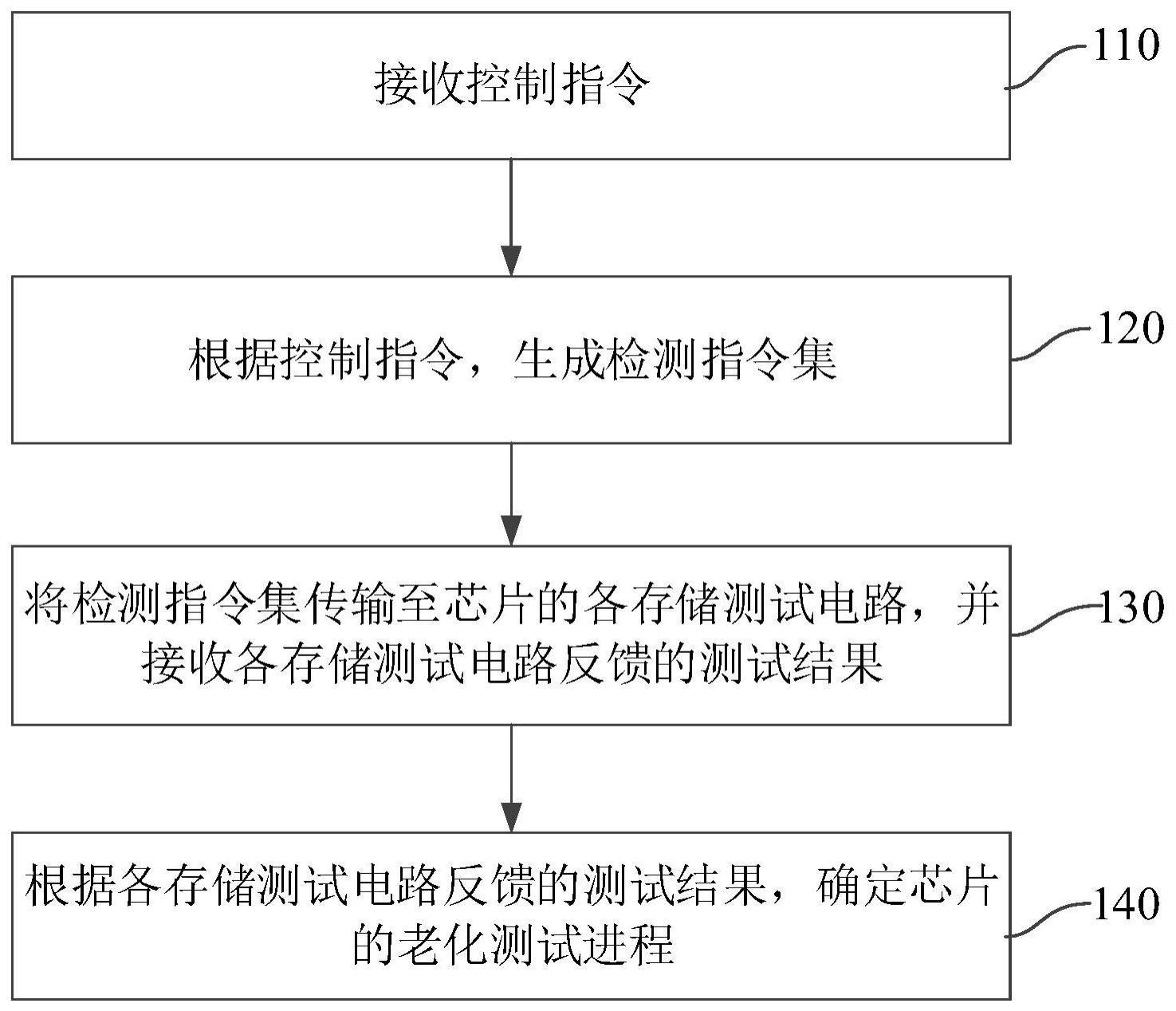

2、本发明实施例提供了一种芯片老化测试方法,包括:

3、接收控制指令;

4、根据控制指令,生成检测指令集;

5、将检测指令集传输至芯片的各存储测试电路,并接收各存储测试电路反馈的测试结果;

6、根据各存储测试电路反馈的测试结果,确定芯片的老化测试进程。

7、可选的,根据各存储测试电路反馈的测试结果,确定芯片的老化测试进程,包括:

8、若存在至少一个存储测试电路反馈的测试结果有错误,则生成修复信息集并根据测试结果确定存在错误的测试结果对应的存储测试电路;

9、将修复信息集传输至存在错误的测试结果对应的存储测试电路。

10、可选的,将修复信息集传输至存在错误的测试结果对应的存储测试电路之后,包括:

11、接收存在错误的测试结果对应的存储测试电路再次反馈的测试结果;

12、若存在至少一个存储测试电路再次反馈的测试结果有错误,则继续将修复信息集传输至再次反馈的有错误的测试结果对应的存储测试电路,直至完成预设次数的修复信息集的传输。

13、可选的,接收存在错误的测试结果对应的存储测试电路再次反馈的测试结果,包括:

14、监测存在错误的测试结果对应的存储测试电路是否完成测试;

15、若存在错误的测试结果对应的存储测试电路完成测试,则接收存在错误的测试结果对应的存储测试电路再次反馈的测试结果。

16、可选的,根据各存储测试电路反馈的测试结果,确定芯片的老化测试进程,包括:

17、若测试结果无误,则停止测试。

18、可选的,接收各存储测试电路反馈的测试结果,包括:

19、监测各存储测试电路是否完成测试;

20、若各存储测试电路均完成测试,则接收各存储测试电路反馈的测试结果。

21、可选的,检测指令集为二进制数据集,测试结果包括二进制数据。

22、第二方面,本发明实施例提供了一种芯片老化测试电路,包括:检测指令集生成模块、修复模块、结果收集模块和测试控制模块;修复模块和结果收集模块均与检测指令集生成模块电连接,检测指令集生成模块、修复模块以及结果收集模块均与测试控制模块电连接;老化测试电路用于通过如第一方面所述的芯片老化测试方法,对芯片进行老化测试。

23、可选的,检测指令集生成模块、修复模块以及结果收集模块均与芯片的各存储测试电路电连接,各存储测试电路与芯片的各存储单元一一对应。

24、可选的,芯片老化测试电路集成在芯片,芯片老化测试电路用于通过各存储测试电路对各存储单元进行老化测试,以对芯片进行老化测试。

25、本发明实施例提供的芯片老化测试方法和测试电路,包括:接收控制指令;根据控制指令,生成检测指令集;将检测指令集传输至芯片的各存储测试电路,并接收各存储测试电路反馈的测试结果;根据各存储测试电路反馈的测试结果,确定芯片的老化测试进程。本发明实施例提供的芯片老化测试方法和测试电路,根据接收的各存储测试电路反馈的测试结果,确定芯片的老化测试进程,如测试结果中的数据相比检测指令集中对应的数据存在未翻转情况,可确定测试结果有错误,则进行预设次数的修复,若修复后测试结果仍有错误则表示存储测试电路对应的存储单元存在问题,芯片有老化趋势,解决了无法覆盖存储单元内部的老化测试问题,从而可提高测试可靠性。

技术特征:1.一种芯片老化测试方法,其特征在于,包括:

2.根据权利要求1所述的芯片老化测试方法,其特征在于,所述根据所述各存储测试电路反馈的测试结果,确定所述芯片的老化测试进程,包括:

3.根据权利要求2所述的芯片老化测试方法,其特征在于,所述将所述修复信息集传输至所述存在错误的测试结果对应的存储测试电路之后,包括:

4.根据权利要求3所述的芯片老化测试方法,其特征在于,所述接收所述存在错误的测试结果对应的存储测试电路再次反馈的测试结果,包括:

5.根据权利要求1所述的芯片老化测试方法,其特征在于,所述根据所述各存储测试电路反馈的测试结果,确定所述芯片的老化测试进程,包括:

6.根据权利要求1所述的芯片老化测试方法,其特征在于,所述接收所述各存储测试电路反馈的测试结果,包括:

7.根据权利要求1所述的芯片老化测试方法,其特征在于,所述检测指令集为二进制数据集,所述测试结果包括二进制数据。

8.一种芯片老化测试电路,其特征在于,包括:检测指令集生成模块、修复模块、结果收集模块和测试控制模块;所述修复模块和所述结果收集模块均与所述检测指令集生成模块电连接,所述检测指令集生成模块、所述修复模块以及所述结果收集模块均与所述测试控制模块电连接;所述老化测试电路用于通过如权利要求1-7任一所述的芯片老化测试方法,对芯片进行老化测试。

9.根据权利要求8所述的芯片老化测试电路,其特征在于,所述检测指令集生成模块、所述修复模块以及所述结果收集模块均与芯片的各存储测试电路电连接,所述各存储测试电路与所述芯片的各存储单元一一对应。

10.根据权利要求9所述的芯片老化测试电路,其特征在于,所述芯片老化测试电路集成在所述芯片,所述芯片老化测试电路用于通过所述各存储测试电路对所述各存储单元进行老化测试,以对所述芯片进行老化测试。

技术总结本发明实施例公开了一种芯片老化测试方法和测试电路。芯片老化测试方法包括:接收控制指令;根据控制指令,生成检测指令集;将检测指令集传输至芯片的各存储测试电路,并接收各存储测试电路反馈的测试结果;根据各存储测试电路反馈的测试结果,确定芯片的老化测试进程。本发明实施例提供的芯片老化测试方法和测试电路,能够提高测试可靠性。技术研发人员:马海英,谭晓慧,张亚林受保护的技术使用者:北京燧原智能科技有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182009.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。