具有三元激活的存储器内计算的制作方法

- 国知局

- 2024-07-31 19:14:33

本申请涉及存储器内计算,并且更具体地,涉及具有三元激活的存储器内计算。

背景技术:

1、与常规的位单元不同,存储器内计算(compute-in-memory;cim)位单元不仅存储位,而且还包括用于将存储位与输入位相乘的逻辑门。cim极大地加快了诸如人工智能的应用的计算时间,因为所产生的乘法不需要从存储器中取回位以传输到算术逻辑单元用于进行后续乘法,而这在经典的冯·诺依曼计算机架构中将被执行。相反,乘法发生在存储器本身。

2、尽管对于诸如人工智能的计算密集型应用,存储器内计算位单元与常规位单元相比是有利的,但是关于容纳(accommodate)与存储器内计算位单元的存储位相乘的输入位的符号(正或负),出现了问题。为了容纳符号,输入位的二进制0值可以被认为表示-1。在这种容纳中,输入位的集合形成输入向量。由于二进制0被映射到-1,因此每个输入向量表示奇数。例如,-7可以由输入向量[-1,-1,-1]表示,而7可以由输入向量[1,1,1]表示。在有符号实现中对输入向量的奇数的这种限制降低了计算精度。此外,利用这种常规的有符号实现,存储器内计算位单元中的电容器的充电和放电可能消耗大量能量。

技术实现思路

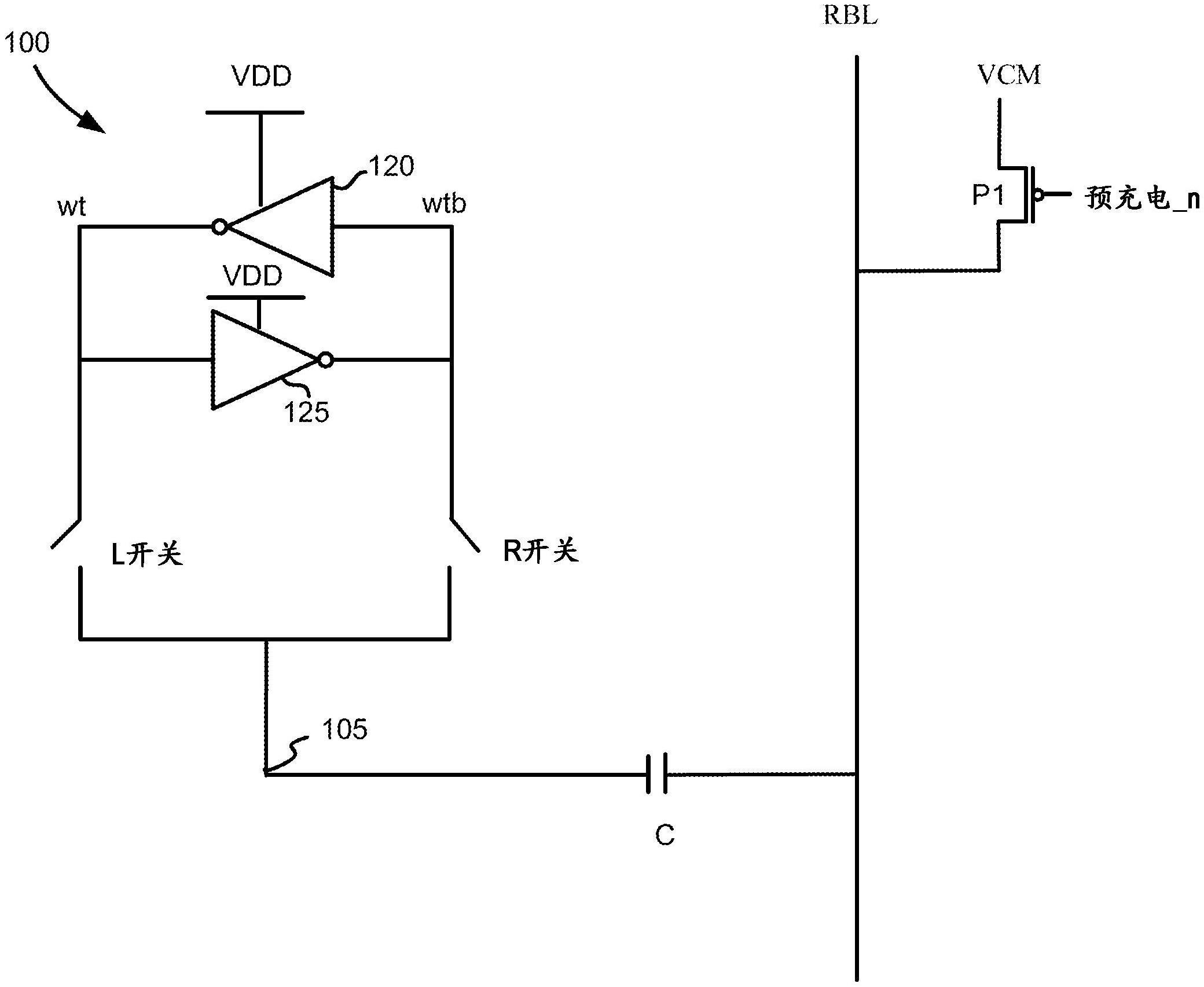

1、提供了一种存储器,该存储器包括:位单元,具有连接到输出节点的开关对;电容器,耦合到输出节点;第一存储元件和多个附加存储元件;以及控制器,控制器被配置为:在存储器的操作的第一阶段期间,从第一存储元件选择第一位,以响应于第一位来控制开关对,并且被配置为:在存储器的操作的第二阶段期间,从多个附加存储元件选择第二位,以响应于第二位来控制开关对。

2、此外,提供了一种控制位单元以将存储位与有符号输入位相乘的方法,方法包括:在操作的第一阶段期间并且响应于有符号输入位的符号具有第一二进制值,闭合耦合在用于存储位的节点与输出节点之间的第一开关,并且断开耦合在用于存储位的补码的节点与输出节点之间的第二开关;在操作的第一阶段期间并且响应于有符号位的符号具有第二二进制值,断开第一开关并且闭合第二开关;在操作的第二阶段期间并且响应于有符号输入位的幅度具有第一二进制值,反转在操作的第一阶段期间建立的第一开关和第二开关的开关状态;以及在操作的第二阶段期间并且响应于有符号输入位的幅度具有第二二进制值,维持在操作的第一阶段期间建立的第一开关和第二开关的开关状态。

3、此外,提供了一种存储器,存储器包括:位单元,被配置为对存储位进行存储,位单元包括耦合在用于存储位的节点与输出节点之间的第一开关以及耦合在用于存储位的补码的节点与输出节点之间的第二开关;电容器,具有连接到输出节点的第一极板;以及控制器,控制器被配置为:在操作的第一阶段中,响应于输入字的符号具有第一二进制值,而断开第二开关并且闭合第一开关,以及响应于输入字的符号位具有第二二进制值,而断开第一开关并且闭合第二开关,以控制第一开关和第二开关的开关状态,其中第二二进制值是第一二进制值的补码。

4、最后,提供了一种用于存储器内计算的操作的方法,方法包括:在操作的第一阶段期间,响应于符号位来控制耦合在位单元与电容器的极板之间的开关对;以及在操作的第二阶段期间,响应于幅度位来控制开关对。

5、通过以下详细描述可以更好地理解这些和其他有利特征。

技术特征:1.一种存储器,包括:

2.根据权利要求1所述的存储器,还包括:

3.根据权利要求1所述的存储器,其中所述第一存储元件被配置为存储符号位,并且所述多个附加存储元件被配置为存储多个幅度位。

4.根据权利要求3所述的存储器,其中所述控制器包括多路复用器,所述多路复用器被配置为:在操作的所述第一阶段期间选择所述第一位,并且在操作的所述第二阶段期间选择所述第二位。

5.根据权利要求1所述的存储器,其中所述控制器还被配置为:在操作的所述第一阶段期间,响应于所述第一位具有第一二进制值,闭合所述开关对中的第一开关并且断开所述开关对中的第二开关,以及响应于所述第一位具有第二二进制值,断开所述第一开关并且闭合所述第二开关,所述第二二进制值是所述第一二进制值的补码。

6.根据权利要求5所述的存储器,其中所述控制器还被配置为:在操作的所述第二阶段期间,响应于所述第二位具有所述第一二进制值,反转所述第一开关和所述第二开关的开关状态,以及响应于所述第二位具有所述第二二进制值,维持所述第一开关和所述第二开关的开关状态。

7.根据权利要求1所述的存储器,其中所述位单元包括第一反相器,所述第一反相器与第二反相器交叉耦合,并且其中所述开关对包括耦合在所述第一反相器的输出节点与所述输出节点之间的第一开关,并且包括耦合在所述第二反相器的输出节点与所述输出节点之间的第二开关。

8.根据权利要求7所述的存储器,其中所述第一开关包括第一传输门,并且其中所述第二开关包括第二传输门。

9.根据权利要求7所述的存储器,其中所述第一开关和所述第二开关是耦合到所述输出节点的仅有开关。

10.根据权利要求7所述的存储器,还包括耦合在所述输出节点与接地之间的第三开关。

11.根据权利要求10所述的存储器,其中所述控制器还被配置为:在操作的所述第一阶段之前的操作的预充电阶段期间,接通所述第三开关,以及在操作的所述第一阶段期间和在操作的所述第二阶段期间关断所述第三开关。

12.根据权利要求10所述的存储器,其中所述第一开关是第一p型金属氧化物半导体(pmos)晶体管,所述第二开关是第二pmos晶体管,并且所述第三开关是n型金属氧化物半导体(nmos)晶体管。

13.根据权利要求7所述的存储器,还包括:耦合在用于共模电压的节点与所述位线之间的第三开关,其中所述控制器还被配置为:在操作的所述第一阶段期间闭合所述第三开关,以及在操作的所述第二阶段期间断开所述第三开关。

14.根据权利要求13所述的存储器,其中所述第三开关是第一pmos晶体管。

15.根据权利要求1所述的存储器,其中所述存储器被合并在蜂窝电话中。

16.一种控制位单元以将存储位与有符号输入位相乘的方法,包括:

17.根据权利要求16所述的方法,其中所述第一二进制值是二进制1值,并且其中所述第二二进制值是二进制0值。

18.根据权利要求16所述的方法,还包括:

19.根据权利要求18所述的方法,还包括:

20.一种存储器,包括:

21.根据权利要求20所述的存储器,还包括:

22.根据权利要求20所述的存储器,还包括:

23.根据权利要求22所述的存储器,其中所述控制器还被配置为:在操作的所述第二阶段期间,响应于所述输入缓冲器中的所述被选择的幅度位具有所述第二二进制值,维持所述第一开关和所述第二开关的所述开关状态。

24.根据权利要求23所述的存储器,其中所述存储器被包括在乘法和累加电路中,所述乘法和累加电路包括多个附加位单元,每个附加位单元包括对应的电容器。

25.根据权利要求24所述的存储器,还包括存储器阵列,所述存储器阵列包括多个列,并且其中所述乘法和累加电路被配置为形成所述多个列中的列。

26.根据权利要求25所述的存储器,还包括:

27.根据权利要求26所述的存储器,其中每个模数转换器是多位模数转换器。

28.一种用于存储器内计算的操作的方法,包括:

29.根据权利要求28所述的方法,其中在操作的所述第一阶段期间控制所述开关对包括:响应于所述符号位具有第一二进制值,闭合所述开关对中的第一开关并且断开所述开关对中的第二开关。

30.根据权利要求29所述的方法,其中在操作的所述第一阶段期间控制所述开关对还包括:响应于所述符号位具有第二二进制值,断开所述第一开关并且闭合所述第二开关,所述第二二进制值是所述第一二进制值的补码。

技术总结提供了一种存储器内计算位单元,该位单元包括用于对存储位进行存储的交叉耦合的反相器对。存储器内计算位单元包括由开关对形成的逻辑门,用于将存储位与输入向量位相乘。控制器在操作的计算阶段期间响应于符号位来控制该开关对,并且在操作的执行阶段期间响应于幅度位来控制该开关对。技术研发人员:S·A·米雷杰,A·斯里瓦斯塔瓦,S·瓦德瓦,R·李,S·莫汉受保护的技术使用者:高通股份有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182001.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表