存储控制器内建自测试的系统的制作方法

- 国知局

- 2024-07-31 19:21:34

本申请涉及存储器,特别涉及一种存储控制器内建自测试的系统。

背景技术:

1、本部分旨在为权利要求书中陈述的本申请的实施方式提供背景或上下文。此处的描述不因为包括在本部分中就承认是已被公开的现有技术。

2、在存储器领域,用户对动态存储器(dram)的访问主要通过内存控制器和物理层接口完成。当用户设计、内存控制、物理层接口调试完毕,准备大规模量产时,经常被良率问题困扰。因为动态存储器系统涉子系统比较复杂,不仅对内存控制器和物理层接口要求较高,而且对印刷电路板(pcb)走线、焊接、内存颗粒良率都有比较高要求。所以客户迫切需要一种能快速准确的自检流程,完成对pcb走线、焊接、内存颗粒良率的检测系统。

3、目前主流的自检系统包括用户自己搭建mbist测试程序,测试机台,pcb探测点等,但是这些方案都包含明显缺点。用户自己搭建的mbist测试程序每次都需要针对新的设计方案重新调整、搭建测试等,费时费力,并且不同软件版本不同芯片型号都要重新调整。测试机台和pcb探测点效率较低,并且以上所述方案可能不能精确定位问题,只能测试出整个系统错误,还要二次定位具体问题。上述方案存在兼容性差,操作复杂,需要额外设备,不能一次精确定位错误类型等问题。

技术实现思路

1、本申请的目的在于提供一种存储控制器内建自测试的系统,内建自测试控制器可以集成到软件开发环境中,当用户希望产生自检程序时根据控制器和物理层接口参数自动匹配生成,快捷方便,不需要额外测试设备。

2、本申请公开了一种存储控制器内建自测试的系统,包括位于印刷电路板上依次耦合的内建自测试控制器、存储控制器、物理层接口和存储颗粒,所述系统执行如下操作:

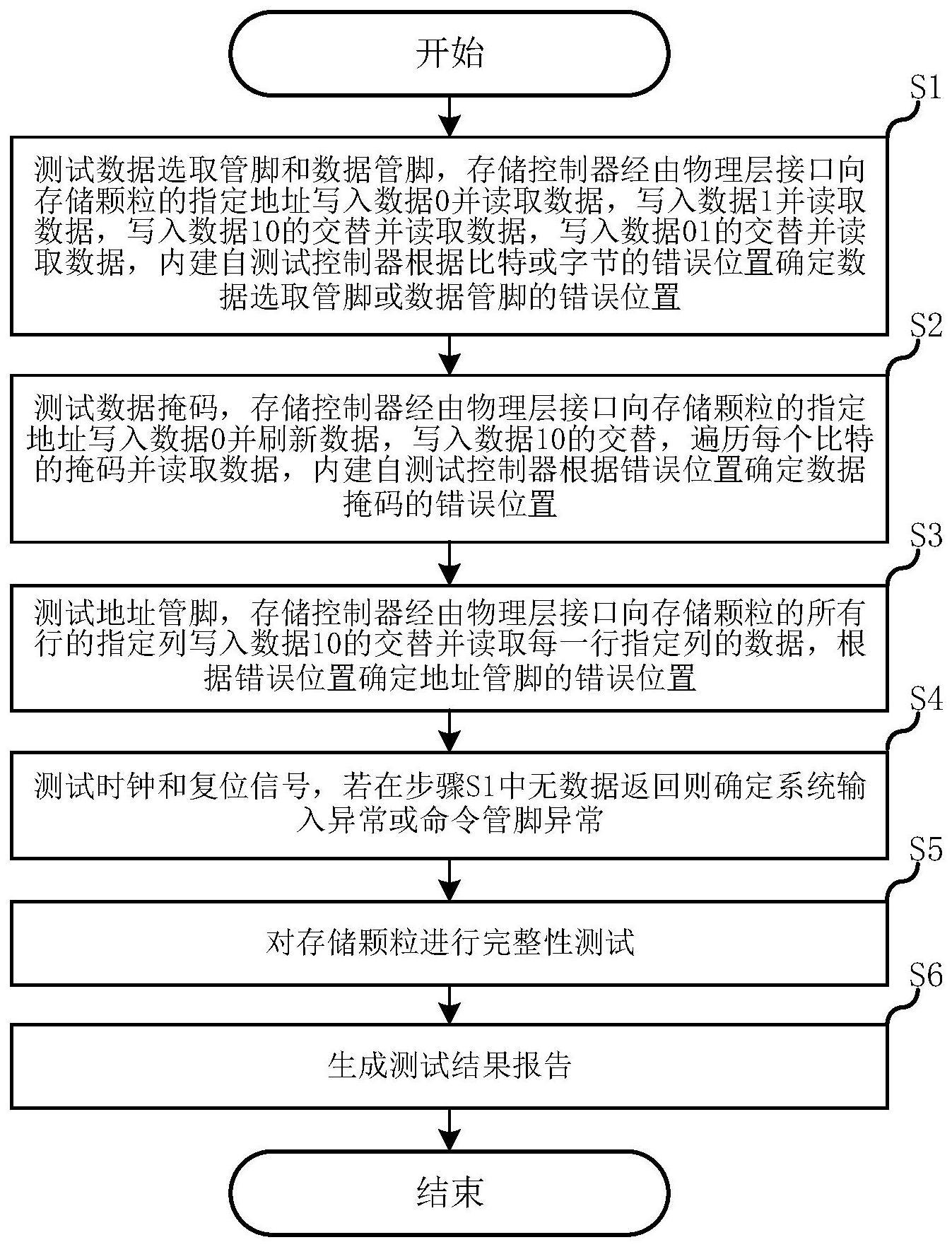

3、步骤s1,测试数据选取管脚和数据管脚,所述存储控制器经由所述物理层接口向所述存储颗粒的指定地址写入数据0并读取数据,写入数据1并读取数据,写入数据10的交替并读取数据,写入数据01的交替并读取数据,所述内建自测试控制器根据比特或字节的错误位置确定数据选取管脚或数据管脚的错误位置;

4、步骤s2,测试数据掩码,所述存储控制器经由所述物理层接口向所述存储颗粒的指定地址写入数据0并刷新数据,写入数据10的交替,遍历每个比特的掩码并读取数据,所述内建自测试控制器根据错误位置确定数据掩码的错误位置;

5、步骤s3,测试地址管脚,所述存储控制器经由所述物理层接口向所述存储颗粒的所有行的指定列写入数据10的交替并读取每一行指定列的数据,根据错误位置确定地址管脚的错误位置;

6、步骤s4,测试时钟和复位信号,若在所述步骤s1中无数据返回则确定系统输入异常或命令管脚异常;

7、步骤s5,对所述存储颗粒进行完整性测试;以及

8、步骤s6,生成测试结果报告。

9、在一个优选例中,在所述步骤s1之前,还包括:

10、使用多块功能正常的印刷电路板运行物理层接口的初始化流程,使用日志打印出各个节点校准的值;

11、计算出所述各个节点校准值的平均值和方差,如果所述方差大于预定义阈值,则对物理层接口进行降速处理;

12、将所述物理层接口调整为fast init模式,将所述各个节点校准值的平均值写入所述物理层接口;以及

13、启动所述物理层接口并启动所述内建自测试控制器。

14、在一个优选例中,在所述步骤s1之前,还包括进行电源诊断,所述电源诊断包括:

15、测试所述物理层接口与所述存储颗粒之间的电源管脚是否存在短路,如静态电流高于阈值,则所述电源管脚存在短路;以及

16、测试所述存储颗粒的电源管脚的接触是否正常,如所述电源管脚异常,对所述印刷电路板进行电压或电流的测试。

17、在一个优选例中,如所述电压的波纹稳定且抖动小于预定值,则所述印刷电路板电压供电正常,如所述电流在正常值范围内,则所述所述印刷电路板电流供电正常。

18、在一个优选例中,在所述步骤s5中,采用漫游算法和/或march c+算法测试所述存储颗粒。

19、在一个优选例中,所述完整性测试包括以下的一项或多项:线固定故障、桥接故障、单元固定故障、开路故障、寻址故障、位丢失、跳变故障、单元耦合故障和数据保持故障。

20、在一个优选例中,所述指定地址为第0组第0块第0行第0列。

21、在一个优选例中,在所述步骤s1中,根据比特或字节的错误位置确定数据选取管脚或数据管脚的错误位置进一步包括:

22、如果比特出现错误,则根据所述比特出现错误的位置确定数据选取管脚的错误位置;以及

23、如果字节出现错误,则根据字节出现错误的位置确定数据管脚的错误位置。

24、在一个优选例中,在所述步骤s6中,所述测试结果报告包括:错误流程类型和颗粒错误地址。

25、在一个优选例中,所述掩码的位宽为数据位宽除以8的值。

26、本申请实施方式中,通过完整的自检流程,多样的测试模式,主流的校验算法,通过对存储控制器的读/写和返回数据校验能快速完成硬件系统自检,并且精确定位错误类型,一次完成自检和错误定位流程,极大简化用户自检操作,加快用户自检速度,实现快速准确的量产测试。

27、本申请的说明书中记载了大量的技术特征,分布在各个技术方案中,如果要罗列出本申请所有可能的技术特征的组合(即技术方案)的话,会使得说明书过于冗长。为了避免这个问题,本申请上述技术实现要素:中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均应该视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a+b+c,在另一个例子中公开了特征a+b+d+e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a+b+c+d的方案因技术不可行而应当不被视为已经记载,而a+b+c+e的方案应当视为已经被记载。

技术特征:1.一种存储控制器内建自测试的系统,其特征在于,包括位于印刷电路板上依次耦合的内建自测试控制器、存储控制器、物理层接口和存储颗粒,所述系统执行如下操作:

2.根据权利要求1所述的系统,其特征在于,在所述步骤s1之前,还包括:

3.根据权利要求1所述的系统,其特征在于,在所述步骤s1之前,还包括进行电源诊断,所述电源诊断包括:

4.根据权利要求3所述的系统,其特征在于,如所述电压的波纹稳定且抖动小于预定值,则所述印刷电路板电压供电正常,如所述电流在正常值范围内,则所述所述印刷电路板电流供电正常。

5.根据权利要求1所述的系统,其特征在于,在所述步骤s5中,采用漫游算法和/或march c+算法测试所述存储颗粒。

6.根据权利要求5所述的系统,其特征在于,所述完整性测试包括以下的一项或多项:线固定故障、桥接故障、单元固定故障、开路故障、寻址故障、位丢失、跳变故障、单元耦合故障和数据保持故障。

7.根据权利要求1所述的系统,其特征在于,所述指定地址为第0组第0块第0行第0列。

8.根据权利要求1所述的系统,其特征在于,在所述步骤s1中,根据比特或字节的错误位置确定数据选取管脚或数据管脚的错误位置进一步包括:

9.根据权利要求1所述的系统,其特征在于,在所述步骤s6中,所述测试结果报告包括:错误流程类型和颗粒错误地址。

10.根据权利要求1所述的系统,其特征在于,所述掩码的位宽为数据位宽除以8的值。

技术总结本申请涉及存储器领域,公开了一种存储控制器内建自测试的系统,包括内建自测试控制器、存储控制器、物理层接口和存储颗粒,执行如下操作:测试数据选取管脚和数据管脚,依次向指定地址写入数据0、1、10的交替、10的交替并读取数据,确定数据选取管脚或数据管脚的错误位置;测试数据掩码,向指定地址写入数据0并刷新数据,写入数据10的交替,遍历掩码并读取数据,确定数据掩码的错误位置;测试地址管脚,向所有行的指定列写入数据10的交替并读取每一行指定列的数据,确定地址管脚的错误位置;测试时钟和复位信号;测试存储颗粒;生成测试结果报告。本申请可以简化用户自检操作,加快自检速度,实现快速准确的量产测试。技术研发人员:汤博先,周成龙受保护的技术使用者:上海安路信息科技股份有限公司技术研发日:技术公布日:2024/1/16本文地址:https://www.jishuxx.com/zhuanli/20240731/182392.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表