存储装置的制作方法

- 国知局

- 2024-07-31 19:28:48

本发明的实施方式涉及一种存储装置。

背景技术:

1、关于如nand(not-and,与非)型闪速存储器那样的存储装置,动作的高速化及可靠性的提高等特性的提高不断推进。

技术实现思路

1、实施方式谋求提高存储装置的特性。

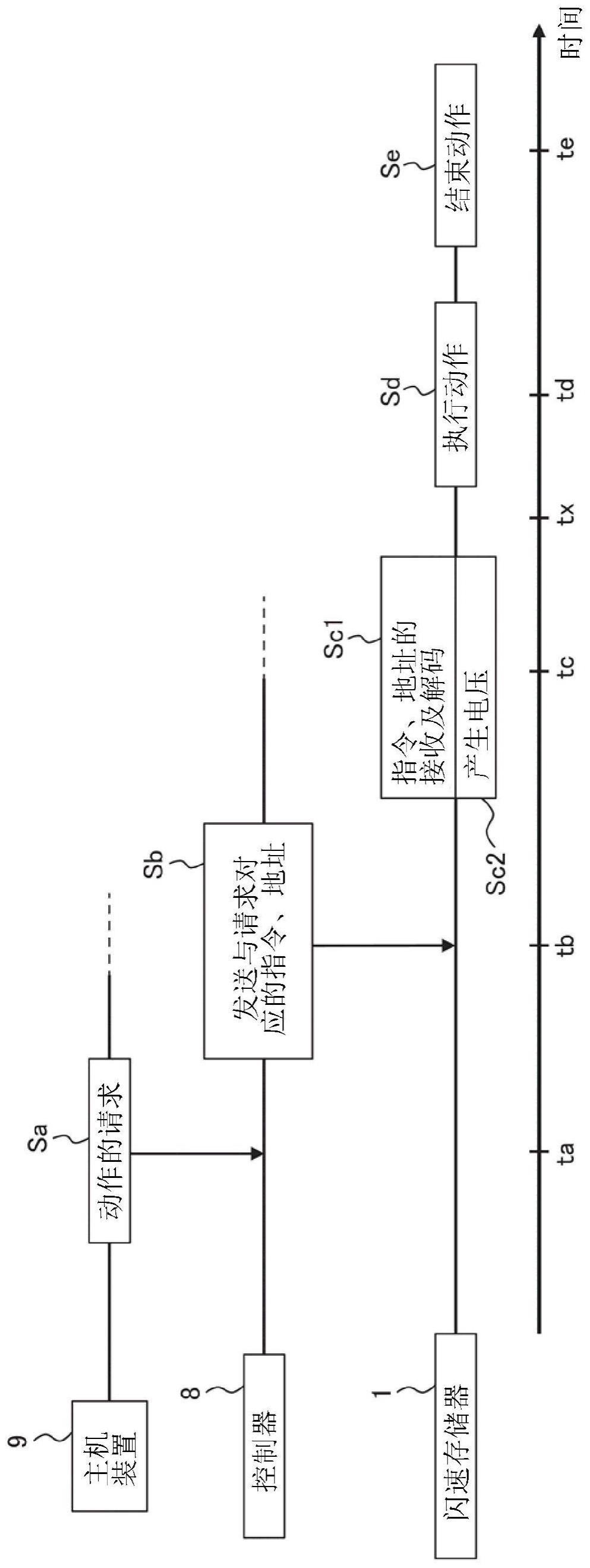

2、实施方式的存储装置具备:存储单元阵列;电压产生电路,产生供给到所述存储单元阵列的1个以上的电压;输入输出电路,接收表示所述存储单元阵列内的区域的地址;及控制电路,控制所述存储单元阵列的动作;且所述电压产生电路是在接收所述地址的过程中,产生所述电压。

技术特征:1.一种存储装置,具备:

2.根据权利要求1所述的存储装置,还具备:

3.根据权利要求2所述的存储装置,其中所述行控制电路使用所述第1信号及所述地址执行计算处理,并基于所述计算处理的结果,控制选择所述存储单元阵列的所述块中与所述地址对应的1个块的第2信号的信号电平。

4.根据权利要求2所述的存储装置,其中在接收到所述地址之后,将所述第1信号的所述信号电平设定在所述第2电平。

5.根据权利要求2所述的存储装置,其中所述行控制电路响应于所述第1信号的所述第2电平,开始供给所述电压。

6.根据权利要求1所述的存储装置,其中:

7.根据权利要求1所述的存储装置,其中:

8.根据权利要求1所述的存储装置,其中:

9.根据权利要求8所述的存储装置,其中:

10.根据权利要求1所述的存储装置,还具备:

11.根据权利要求10所述的存储装置,其中:

12.根据权利要求10所述的存储装置,其中在所述就绪/忙碌信号表示所述就绪状态的第1期间内且在所述就绪/忙碌信号表示所述忙碌状态的第2期间内,所述温度传感器周期性地测定所述温度。

13.根据权利要求1所述的存储装置,还具备:

14.根据权利要求13所述的存储装置,其中:

15.根据权利要求1所述的存储装置,其中在完成所述地址的解码之前,所述控制电路预测性地开始对所述存储单元阵列供给所述电压。

16.根据权利要求1所述的存储装置,其中在与所述地址的解码的完成自我匹配的时序时,所述控制电路开始对所述存储单元阵列供给所述电压。

17.根据权利要求1所述的存储装置,其中所述存储单元阵列具有包含电荷蓄积部的存储单元。

18.根据权利要求1所述的存储装置,其中所述存储装置是随机存取存储器。

19.一种存储装置,具备:

20.根据权利要求19所述的存储装置,其中所述控制电路在所述读出动作中将读出电压供给到所述多条字线中的选择字线,所述非选择电压比所述读出电压高。

21.根据权利要求20所述的存储装置,其中在所述就绪/忙碌信号从所述就绪状态转变为所述忙碌状态之后将所述读出电压供给到所述选择字线。

22.根据权利要求19所述的存储装置,其中在接收所述地址的所有部分之后将所述非选择电压供给到所述多条字线中的每一条。

23.根据权利要求19所述的存储装置,其中在接收所述地址的所有部分之前将所述非选择电压供给到所述多条字线中的每一条。

24.根据权利要求19所述的存储装置,其中在接收所述地址的过程中,在供给所述非选择电压之后将比所述非选择电压低的第1电压供给到所述多条字线中的1条。

25.根据权利要求19所述的存储装置,还具备:

26.根据权利要求19所述的存储装置,还具备:

27.根据权利要求19所述的存储装置,还具备:

28.根据权利要求19所述的存储装置,还具备:

29.根据权利要求19所述的存储装置,其中基于所述第1指令之前接收的第2指令,所述控制电路开始对所述存储单元阵列供给所述电压。

30.根据权利要求19所述的存储装置,其中:

31.根据权利要求19所述的存储装置,其中:

32.根据权利要求31所述的存储装置,其中:

33.根据权利要求19所述的存储装置,还具备:

34.根据权利要求33所述的存储装置,其中:

35.根据权利要求33所述的存储装置,其中在所述就绪/忙碌信号表示所述就绪状态的第1期间内且在所述就绪/忙碌信号表示所述忙碌状态的第2期间内,所述温度传感器周期性地测定所述温度。

36.根据权利要求19所述的存储装置,其中在完成所述地址的解码之前,所述控制电路预测性地开始对所述存储单元阵列供给所述电压。

37.根据权利要求19所述的存储装置,其中所述存储单元阵列具有包含电荷蓄积部的存储单元。

38.根据权利要求19所述的存储装置,其中所述存储装置是nand型闪速存储器。

技术总结本发明的实施方式提高存储装置的特性。本发明的实施方式的存储装置包含:存储单元阵列;电压产生电路,产生供给到存储单元阵列的电压;输入输出电路,接收表示存储单元阵列内的区域的地址;及控制电路,控制存储单元阵列的动作;且电压产生电路在接收地址的过程中产生电压。技术研发人员:菅原昭雄,半田贵也,矶村亮辅,上原一人,佐藤淳一,浅冈典央,山冈雅史,沙納德·布什納克,柴崎谦,熊崎规泰,寺田有里受保护的技术使用者:铠侠股份有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/182681.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表