存储器和存取方法与流程

- 国知局

- 2024-07-31 19:32:45

本技术实施例涉及半导体领域,具体涉及一种存储器和存取方法。

背景技术:

1、近年来,人工智能、边缘计算等新兴应用场景的需求不断增加,对传统存储器的容量、功耗和速率提出了一定挑战,促使新型存储器不断发展。铁电存储器作为一种新型存储器,具有非易失性,读写速度高,低功耗等优势。m个晶体管和n个电容器(m transistor andn capacitors,mtnc)结构的出现极大的提高了铁电存储器的存储密度,但目前其类似动态随机存取存储器(dynamic random access memory like,dram-like)的读取方式,铁电电容器会出现半选电压的扰动(disturb)问题,尤其是单边扰动,严重降低了存储器的数据可靠性,增加了系统功耗。

2、因此,如何降低电容器受到的单边扰动,提高数据存储的可靠性是一个亟待解决的问题。

技术实现思路

1、本技术实施例提供一种存储器和存取方法,能够将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

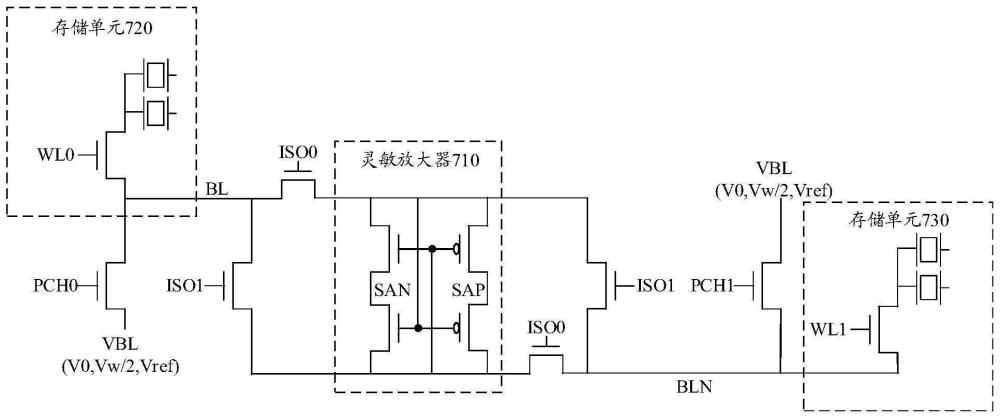

2、第一方面,提供了一种存储器,包括:第一存储单元,所述第一存储单元为选中进行读操作或者写操作的存储单元;灵敏放大器、第一位线和第二位线,所述第一位线连接所述第一存储单元和所述灵敏放大器的第一输出,所述第二位线连接所述灵敏放大器的第二输出;第一隔离器、第二隔离器、第三隔离器和第四隔离器,所述第一隔离器连接所述第一位线和所述灵敏放大器的所述第一输出,所述第二隔离器连接所述第二位线和所述灵敏放大器的所述第二输出,所述第三隔离器连接所述第一位线和所述灵敏放大器的所述第二输出,所述第四隔离器连接所述第二位线和所述灵敏放大器的所述第一输出;控制器,用于在所述第一存储单元的回写完成之前,导通所述第一隔离器和所述第二隔离器,关断所述第三隔离器和所述第四隔离器,在所述第一存储单元的所述回写完成之后,关断所述第一隔离器和所述第二隔离器,导通所述第三隔离器和所述第四隔离器。

3、本技术实施例中的存储器包括第一隔离器、第二隔离器、第三隔离器和第四隔离器,通过这四种隔离器能够在第一存储单元的回写完成后交换第一位线和第二位线的电压,构成互换阶段,从而将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

4、应理解,第一存储单元可以是存储阵列中任一个存储单元。本技术提供的第一存储单元为m个晶体管和n个电容器(m transistor and n capacitors,mtnc)的结构,即第一存储单元包括m个晶体管和n个电容器。其中,m≥1,n≥2。示例性地,该存储器可以是铁电存储器,或者可以是由其他材料构成有单边扰动问题的存储器。

5、应理解,灵敏放大器的第一输出和第二输出包括输出端口。灵敏放大器可以与多个存储单元通过位线连接。

6、应理解,第一位线和第二位线共同连接同一个灵敏放大器,可以看作第二位线与第一位线共用读出电路。

7、可选的,第一位线可以用bl表示,第二位线可以用bln表示。可以在第一位线上布置至少一个第一隔离器,第一隔离器连接第一位线和灵敏放大器的第一输出。可以在第二位线上布置至少一个第二隔离器,第二隔离器连接第二位线和灵敏放大器的第二输出。第三隔离器连接第一位线和灵敏放大器的第二输出,第四隔离器连接第二位线和灵敏放大器的第一输出。示例性地,第一位线和第二位线通过第一导线连接,第三隔离器和第四隔离器位于第一导线上。

8、灵敏放大器用于将bl和bln的电压放大。示例性地,灵敏放大器包括灵敏放大器n场效应管控制(sense-amplifier n-fet control,san)和灵敏放大器p场效应管控制(sense-amplifier p-fet control,sap),san和sap为灵敏放大器工作提供电源。san和sap的电源值决定了灵敏放大器将bl和bln的电压放大至什么电压状态。示例性地,当san和sap分别为0和vw时,灵敏放大器在工作完成后,bl和bln的电压会被拉至0或者vw;当san和sap分别为vw和vw/2时,灵敏放大器工作完成后,bl和bln的电压会被拉至vw或者vw/2,其中vw表示所述第一存储单元的写操作电压。

9、应理解,控制器可以提供控制信号,在第一存储单元的回写完成之前,导通第一隔离器和第二隔离器,关断第三隔离器和第四隔离器,在第一存储单元的回写完成之后,关断第一隔离器和第二隔离器,导通第三隔离器和第四隔离器。

10、可选的,灵敏放大器、第一隔离器、第二隔离器、第三隔离器和第四隔离器可以集成在控制器中,本技术对此不作限定。

11、应理解,导通隔离器指的是令隔离器两端的线路导通,关断隔离器指的是断开隔离器两端的线路。

12、应理解,第一存储单元的回写包括第一存储单元中被选中电容器的回写。

13、本技术实施例在第一存储单元的回写完成之前,第一隔离器和第二隔离器是导通的,第三隔离器和第四隔离器是关断的。在回写完成之后,关断第一隔离器和第二隔离器,导通第三隔离器和第四隔离器,可以使bl和bln的电压互换,构成互换阶段,从而将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

14、结合第一方面,在一种可能的实现方式中,若所述回写完成之前,所述第一位线的电压为第一正电压,所述第二位线的电压为第二正电压,则所述回写完成之后,所述第一位线的电压为所述第二正电压,所述第二位线的电压为所述第一正电压;若所述回写完成之前,所述第一位线的电压为所述第二正电压,所述第二位线的电压为所述第一正电压,则所述回写完成之后,所述第一位线的电压为所述第一正电压,所述第二位线的电压为所述第二正电压。

15、可选的,所述第一正电压=vw/2,所述第二正电压=vw,其中vw表示所述第一存储单元的写操作电压。

16、示例性地,若回写完成之前,第一位线的电压为vw/2,第二位线的电压为vw,则回写完成之后,第一位线的电压为vw,第二位线的电压为vw/2;若回写完成之前,第一位线的电压为vw,第二位线的电压为vw/2,则回写完成之后,第一位线的电压为vw/2,第二位线的电压为vw。

17、本技术实施例中的存储器包括第一隔离器、第二隔离器、第三隔离器和第四隔离器,通过这四种隔离器能够在第一存储单元的回写完成后交换第一位线和第二位线的电压,构成互换阶段,从而将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

18、结合第一方面,在一种可能的实现方式中,所述第一隔离器位于所述第三隔离器和所述灵敏放大器之间,所述第二隔离器位于所述第四隔离器和所述灵敏放大器之间。

19、本技术实施例中的存储器包括第一隔离器、第二隔离器、第三隔离器和第四隔离器,通过这四种隔离器能够在第一存储单元的回写完成后交换第一位线和第二位线的电压,构成互换阶段,从而将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

20、结合第一方面,在一种可能的实现方式中,在所述回写完成之后,所述第一存储单元的浮栅极与所述第一位线的电压相同,所述第一存储单元的多个电容器的第一极板与所述浮栅极连接。

21、应理解,第一存储单元包括多个电容器,每个电容器的第一极板与浮栅极(floating gate,fg)连接,第二极板与板线连接,浮栅极与第一位线连通。在回写完成之后,交换第一位线和第二位线的电压,由于浮栅极与第一位线连通,因此,第一存储单元的浮栅极与第一位线的电压相同。

22、本技术实施例中的存储器包括第一隔离器、第二隔离器、第三隔离器和第四隔离器,通过这四种隔离器能够在第一存储单元的回写完成后交换第一位线和第二位线的电压,构成互换阶段,从而将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

23、结合第一方面,在一种可能的实现方式中,所述第一隔离器和所述第二隔离器包括隔离(isolation,iso)管。

24、结合第一方面,在一种可能的实现方式中,所述第一位线和所述第二位线通过第一导线连接,所述第一隔离器位于所述第一位线上,所述第二隔离器位于所述第二位线上,所述第三隔离器和所述第四隔离器位于所述第一导线上。

25、本技术实施例中的存储器包括第一隔离器、第二隔离器、第三隔离器和第四隔离器,通过这四种隔离器能够在第一存储单元的回写完成后交换第一位线和第二位线的电压,构成互换阶段,从而将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

26、第二方面,提供了一种集成电路,包括第一方面或第一方面中的任意一种可能的实现方式中的存储器。

27、第三方面,提供一种电子设备,包括电路板和第一方面所述的存储器,所述存储器设置于所述电路板上且与所述电路板电连接。

28、第四方面,提供一种存取存储器的方法,所述方法应用于包含有第一存储单元、灵敏放大器、第一位线、第二位线、第一隔离器、第二隔离器、第三隔离器、第四隔离器和控制器的存储器中,所述第一存储单元为选中进行读操作或者写操作的存储单元,所述第一位线连接所述第一存储单元和所述灵敏放大器的第一输出,所述第二位线连接所述灵敏放大器的第二输出,所述第一隔离器连接所述第一位线和所述灵敏放大器的所述第一输出,所述第二隔离器连接所述第二位线和所述灵敏放大器的所述第二输出,所述第三隔离器连接所述第一位线和所述灵敏放大器的所述第二输出,所述第四隔离器连接所述第二位线和所述灵敏放大器的所述第一输出,所述方法包括:所述控制器在所述第一存储单元的回写完成之前,导通所述第一隔离器和所述第二隔离器,关断所述第三隔离器和所述第四隔离器;所述控制器在所述第一存储单元的所述回写完成之后,关断所述第一隔离器和所述第二隔离器,导通所述第三隔离器和所述第四隔离器。

29、应理解,第一存储单元可以是存储阵列中任一个存储单元。本技术提供的第一存储单元为m个晶体管和n个电容器(m transistor and n capacitors,mtnc)的结构,即第一存储单元包括m个晶体管和n个电容器。其中,m≥1,n≥2。示例性地,该存储器可以是铁电存储器,或者可以是由其他材料构成有单边扰动问题的存储器。

30、应理解,灵敏放大器的第一输出和第二输出包括输出端口。

31、应理解,第一位线和第二位线共同连接同一个灵敏放大器,可以看作第二位线与第一位线共用读出电路。

32、可选的,第一位线可以用bl表示,第二位线可以用bln表示。可以在第一位线上布置至少一个第一隔离器,第一隔离器连接第一位线和灵敏放大器的第一输出。可以在第二位线上布置至少一个第二隔离器,第二隔离器连接第二位线和灵敏放大器的第二输出。第三隔离器连接第一位线和灵敏放大器的第二输出,第四隔离器连接第二位线和灵敏放大器的第一输出。示例性地,第一位线和第二位线通过第一导线连接,第三隔离器和第四隔离器布置在第一导线上。

33、应理解,导通隔离器指的是令隔离器两端的线路导通,关断隔离器指的是断开隔离器两端的线路。

34、本技术实施例中的存储器包括第一隔离器、第二隔离器、第三隔离器和第四隔离器,通过这四种隔离器能够在第一存储单元的回写完成后交换第一位线和第二位线的电压,构成互换阶段,从而将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

35、结合第四方面,在一种可能的实现方式中,若所述回写完成之前,所述第一位线的电压为第一正电压,所述第二位线的电压为第二正电压,则所述回写完成之后,所述第一位线的电压为所述第二正电压,所述第二位线的电压为所述第一正电压;若所述回写完成之前,所述第一位线的电压为所述第二正电压,所述第二位线的电压为所述第一正电压,则所述回写完成之后,所述第一位线的电压为所述第一正电压,所述第二位线的电压为所述第二正电压。

36、结合第四方面,在一种可能的实现方式中,所述第一正电压=vw/2,所述第二正电压=vw,其中vw表示所述第一存储单元的写操作电压。

37、本技术实施例中的存储器包括第一隔离器、第二隔离器、第三隔离器和第四隔离器,通过这四种隔离器能够在第一存储单元的回写完成后交换第一位线和第二位线的电压,构成互换阶段,从而将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

38、结合第四方面,在一种可能的实现方式中,在所述回写完成之后,所述第一存储单元的浮栅极与所述第一位线的电压相同,所述第一存储单元的多个电容器的第一极板与所述浮栅极连接。

39、应理解,第一存储单元包括多个电容器,每个电容器的第一极板与浮栅极(floating gate,fg)连接,第二极板与板线连接,浮栅极与第一位线连通。在回写完成之后,交换第一位线和第二位线的电压,由于浮栅极与第一位线连通,因此,第一存储单元的浮栅极与第一位线的电压相同。

40、本技术实施例中的存储器包括第一隔离器、第二隔离器、第三隔离器和第四隔离器,通过这四种隔离器能够在第一存储单元的回写完成后交换第一位线和第二位线的电压,构成互换阶段,从而将存储单元整个访问周期内的单边扰动转换为双边扰动,减少了单边扰动对电容器的影响。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183010.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

存储器阵列的制作方法

下一篇

返回列表