存储芯片的测试大板和测试装置的制作方法

- 国知局

- 2024-07-31 19:40:51

本申请涉及晶圆封装、芯片,尤其涉及一种存储芯片的测试大板和测试装置。

背景技术:

1、目前来说,存储芯片种类繁多,涉及的主控搭配方式多变,常规集成式批量测试装置无法做到同时兼容不同主控方案,一套装置只能针对一个测试方案。而且现有的批量测试装置是集成式,集电源、io接口、芯片、主控于一体,统一供电,为适应庞大的测试需求,需配备大量的不同测试装置。多少种主控与颗粒方案就需要多少套测试大板,测试不同存储芯片时启用相应的测试装置;个别测试接口损坏,选择停止整套测试装置的工作进行修复或更换整套测试装置。会严重导致其它搭配装置闲置率高、利用率低,有个别接口或模块损坏无法维修,甚至会影响整个装置的工作。

2、因此,基于上述原因,本领域技术人员亟需提供一种同时能够满足多种规格的存储芯片进行测试,且在部分线路损坏的情况下,不影响整体测试的测试大板。

技术实现思路

1、本申请的目的是提供一种存储芯片的测试大板和测试装置,通过上述方案实现测试大板同时能够满足多种规格的存储芯片进行测试,且在部分线路损坏的情况下,不影响整体测试。

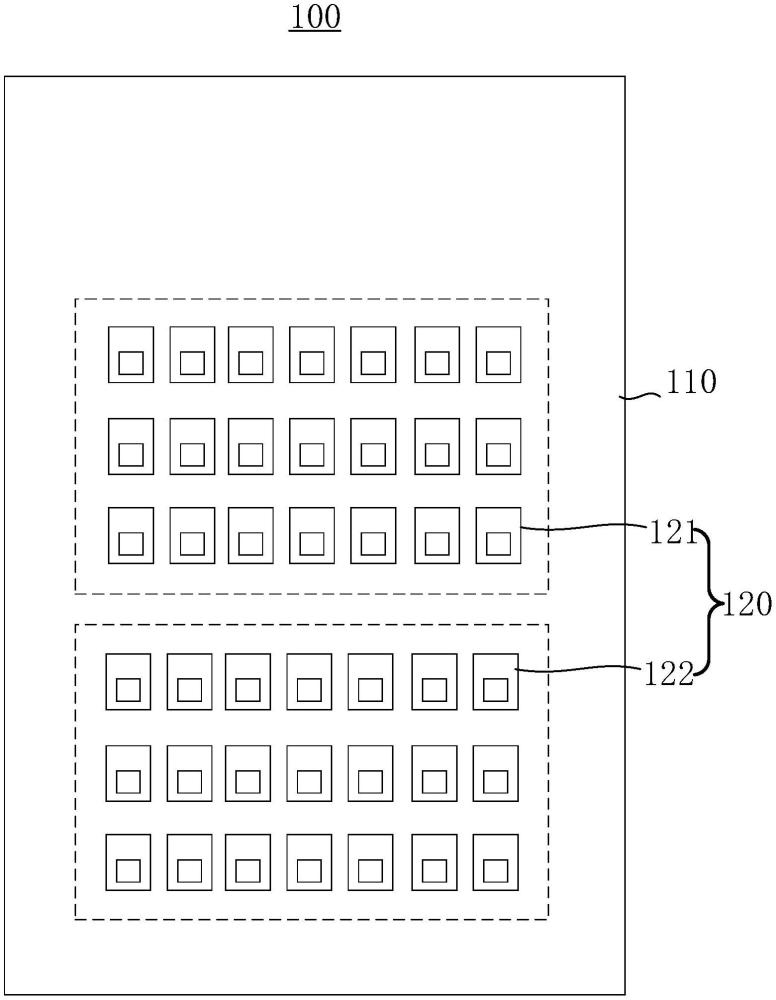

2、本申请公开了一种存储芯片的测试大板,包括:

3、底板,设置有多个测试接口;

4、多个测试小板,对应多个所述测试接口设置;

5、连接器,设置在所述测试小板上,用于连接所述测试接口和所述测试小板之间的电源与通信;以及

6、多个测试座,分别设置在多个所述测试小板背离所述连接器的一侧,与所述测试小板电性连接,所述测试座用于放置所述存储芯片;

7、其中,多个所述测试小板中至少包括两种不同规格的测试小板。

8、可选的,所述测试小板上至少设置有一个测试座;所述测试小板上设置有状态指示灯,所述状态指示灯用于在所述测试接口与所述测试小板之间连通后发光。

9、可选的,所述底板上至少设置有两个分区,每个所述分区分别设置有多个相同规格的测试小板;多个所述测试小板中至少包括多个第一测试小板和多个第二测试小板,所述第一测试小板和所述第二测试小板设置在不同的所述分区;所述第一测试小板用于放置第一存储芯片,所述第二测试小板用于放置第二存储芯片。

10、可选的,所述分区至少包括第一分区和第二分区,所述第一分区内设置有第一标识,所述第二分区内设置有第二标识;所述第一测试小板上设置有第一对位标识,所述第二测试小板上设置有第二对位标识。

11、可选的,所述底板上至少设置有两个分区,每个所述分区内设置有一块所述测试小板,所述测试小板至少设置有两块,两块所述测试小板上分别设置有多个主控芯片和多个测试座,且两块所述测试小板上的主控芯片规格不同。

12、可选的,每个所述分区内设置有一个测试接口,所述测试小板通过所述测试接口连接至所述底板上,一个所述测试小板上的多个所述主控芯片共用电源与通信。

13、可选的,所述测试小板上设置有主控芯片,所述主控芯片与所述测试小板可拆卸连接,所述主控芯片通过所述测试座外接所述存储芯片,并对所述存储芯片进行测试。

14、可选的,所述连接器与所述测试小板可拆卸连接。

15、可选的,所述测试小板至少包括仅设置有一个主控芯片的测试小板和设置有多个主控芯片的测试小板。

16、本申请还公开了一种测试装置,包括上述的存储芯片的测试大板。

17、本申请通过利用连接器,由连接器来实现底板与测试小板之间的通信、电源等,且通过连接器实现更换底板上的测试小板。即通过连接器实现模块化设计,各个测试接口所需电源通过连接器引出,对每个测试小板上的主控芯片与存储芯片实现独立的电源接口、独立io接口,由共同的底板集中供电。其中可通过将多种规格的测试小板设置在一个底板上,来同时对多个不同规格存储芯片同时测试,有效提高了测试大板的利用率,而且在部分电路损坏的情况下,完全不影响其他测试小板的正常运行。实现测试小板与底板灵活搭配、独立测试、快速修复,提高装置利用率的同时降低报废率,降低硬件消耗、减小空间占用、降低成本的效果。

技术特征:1.一种存储芯片的测试大板,其特征在于,包括:

2.根据权利要求1所述的存储芯片的测试大板,其特征在于,所述测试小板上至少设置有一个测试座;

3.根据权利要求1所述的存储芯片的测试大板,其特征在于,所述底板上至少设置有两个分区,每个所述分区分别设置有多个相同规格的测试小板;

4.根据权利要求3所述的存储芯片的测试大板,其特征在于,所述分区至少包括第一分区和第二分区,所述第一分区内设置有第一标识,所述第二分区内设置有第二标识;

5.根据权利要求1所述的存储芯片的测试大板,其特征在于,所述底板上至少设置有两个分区,每个所述分区内设置有一块所述测试小板,所述测试小板至少设置有两块,两块所述测试小板上分别设置有多个主控芯片和多个测试座,且两块所述测试小板上的主控芯片规格不同。

6.根据权利要求5所述的存储芯片的测试大板,其特征在于,每个所述分区内设置有一个测试接口,所述测试小板通过所述测试接口连接至所述底板上,一个所述测试小板上的多个所述主控芯片共用电源与通信。

7.根据权利要求1所述的存储芯片的测试大板,其特征在于,所述测试小板上设置有主控芯片,所述主控芯片与所述测试小板可拆卸连接,所述主控芯片通过所述测试座外接所述存储芯片,并对所述存储芯片进行测试。

8.根据权利要求1所述的存储芯片的测试大板,其特征在于,所述连接器与所述测试小板可拆卸连接。

9.根据权利要求1所述的存储芯片的测试大板,其特征在于,所述测试小板至少包括仅设置有一个主控芯片的测试小板和设置有多个主控芯片的测试小板。

10.一种测试装置,其特征在于,包括权利要求1-9任意一项所述的存储芯片的测试大板。

技术总结本申请公开了一种存储芯片的测试大板和测试装置,测试大板包括底板、多个测试小板、多个连接器和多个测试座,其中,底板设置有多个测试接口;多个测试小板对应多个所述测试接口设置;连接器设置在所述测试小板上,用于连接所述测试接口和所述测试小板之间的电源与通信;以及多个测试座分别设置在多个所述测试小板背离所述连接器的一侧,与所述测试小板电性连接,所述测试座用于放置所述存储芯片;其中,多个所述测试小板中至少包括两种不同规格的测试小板。通过上述方案实现测试大板同时能够满足多种规格的存储芯片进行测试,且在部分线路损坏的情况下,不影响整体测试。技术研发人员:贾艳萍,俞文全,李华星受保护的技术使用者:深圳市时创意电子有限公司技术研发日:20230615技术公布日:2024/2/29本文地址:https://www.jishuxx.com/zhuanli/20240731/183555.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。