数据传输电路及存储器的制作方法

- 国知局

- 2024-07-31 19:44:06

本公开实施例涉及半导体,涉及但不限于一种数据传输电路及存储器。

背景技术:

1、随着手机、平板、个人计算机等电子设备的普及,半导体存储器技术也得到了快速的发展。例如dram(dynamic random access memory,动态随机存取存储器),由于其高密度、低功耗、低价格等优点,已广泛应用于各种电子设备中。

2、存储器的数据输入输出需要复杂的外围电路来实现,例如,数据输出端需要数据传输电路。然而,存储器的外围电路极易在各种情况下发生静电损伤,因此,如何实现存储器外围电路的静电保护是本领域亟待解决的问题之一。

技术实现思路

1、有鉴于此,本公开实施例提供一种数据传输电路及存储器。

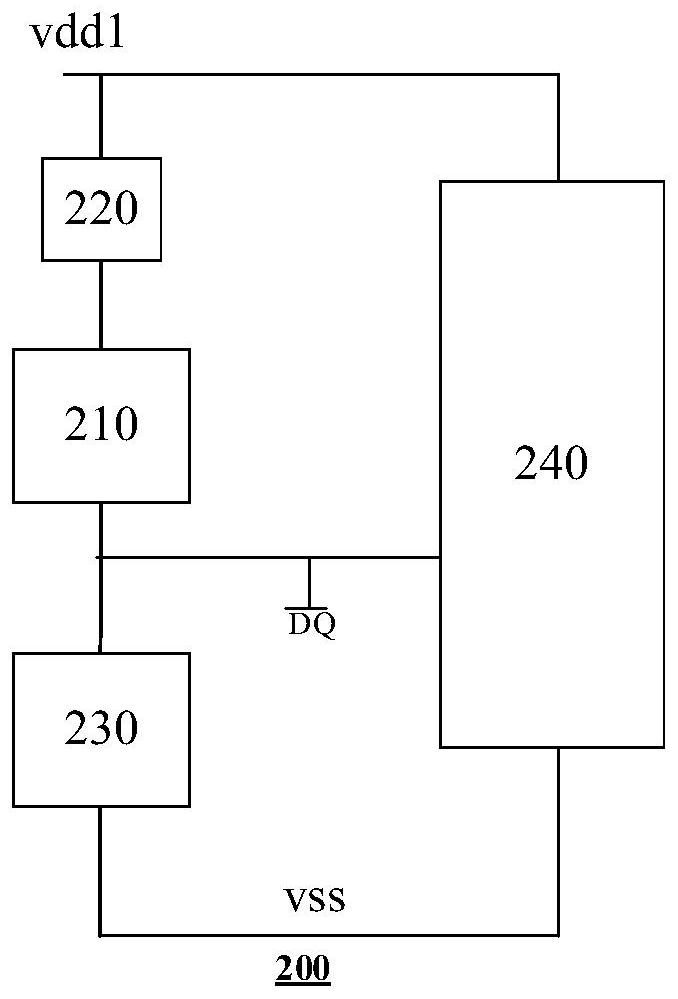

2、第一方面,本公开实施例提供一种数据传输电路,包括:

3、数据传输端,至少用于输出读取的数据;

4、上拉模块,与所述数据传输端连接,用于提供输出第一电平数据时所需的电压信号;

5、第一保护模块,连接在所述第一电源端与所述上拉模块之间,用于防止所述上拉模块中的器件击穿;

6、下拉模块,连接第二电源端和所述数据传输端,用于提供输出第二电平数据时所需的电压信号;

7、静电保护模块,分别连接所述第一电源端、第二电源端和所述数据传输端,用于泄放所述数据传输电路中的静电电荷。

8、在一些实施例中,所述第一保护模块包括:

9、第一n型晶体管;所述第一n型晶体管的衬底端连接在所述第二电源端;所述第一n型晶体管的第一端连接所述第一电源端;所述第一n型晶体管的第二端连接所述上拉模块;

10、其中,第一n型晶体管至少在输出第一电平数据的情况下处于导通状态。

11、在一些实施例中,所述上拉模块包括:

12、第一p型晶体管;所述第一p型晶体管的衬底端连接所述第一p型晶体管的源极;所述第一p型晶体管在输出所述第一电平数据的情况下处于导通状态。

13、在一些实施例中,所述上拉模块还包括:

14、第二n型晶体管,连接在所述第一p型晶体管与所述第二电源端之间;所述第二n型晶体管用于在输出所述第二电平数据的情况下处于导通状态,以关闭所述上拉模块。

15、在一些实施例中,所述上拉模块还包括:

16、第三n型晶体管;所述第三n型晶体管的源极连接第三电源端,漏极连接所述数据传输端,栅极连接所述第一p型晶体管的漏极并连接所述第二n型晶体管的漏极;

17、其中,所述第三n型晶体管基于所述第一p型晶体管以及所述第二n型晶体管的状态导通或截止。

18、在一些实施例中,所述上拉模块还包括:

19、第四n型晶体管,连接在所述第三电源端与所述第三n型晶体管之间;所述第四n型晶体管至少在输出所述第一电平数据的情况下处于导通状态。

20、在一些实施例中,所述下拉模块包括:

21、第五n型晶体管,连接在第二电源端与所述数据传输端之间;所述第五n型晶体管在输出所述第二电平数据的情况下处于导通状态。

22、在一些实施例中,所述下拉模块还包括:

23、第二p型晶体管;所述第二p型晶体管的源极连接所述第一电源端,漏极连接所述第五n型晶体管的栅极。

24、在一些实施例中,所述下拉模块还包括:

25、第六n型晶体管;所述第六n型晶体管的源极连接所述第二电源端,漏极连接所述第二p型晶体管的漏极,并连接所述第五n型晶体管的栅极;所述第五n型晶体管基于所述第二p型晶体管以及所述第六n型晶体管的状态导通或截止。

26、在一些实施例中,所述下拉模块还包括:

27、第二保护模块,连接在所述第二p型晶体管与所述第一电源端之间,用于防止所述下拉模块中的器件击穿。

28、在一些实施例中,所述第二保护模块包括:

29、第七n型晶体管,所述第七n型晶体管的衬底端连接所述第二电源端;

30、其中,第七n型晶体管至少在输出第二电平数据的情况下处于导通状态。

31、在一些实施例中,所述所述下拉模块还包括:

32、电阻,连接在所述第五n型晶体管与所述数据传输端之间。

33、在一些实施例中,所述静电保护模块包括:

34、第一二极管,连接在所述第一电源端与第三电源端之间;

35、第二二极管,连接在所述第二电源端与所述数据传输端之间;

36、第三二极管,连接在第三电源端与所述数据传输端之间。

37、在一些实施例中,所述静电保护模块还包括:

38、第一钳位单元,位于所述第一电源端与所述第二电源端之间,用于限制所述第一电源端与所述第二电源端之间的电压差。

39、在一些实施例中,所述静电保护模块还包括:

40、第二钳位单元,位于所述第三电源端与所述第二电源端之间,用于限制所述第三电源端与所述第二电源端之间的电压差。

41、第二方面,本公开实施例还提供一种存储器,包括:

42、存储单元阵列;

43、与所述存储单元阵列耦接的外围电路;

44、其中,所述外围电路至少包括如上述任一实施例所述的数据传输电路。

45、本公开实施例中的数据传输电路,除了可以利用静电保护模块实现防静电的效果,还利用设置在上拉模块与第一电源端之间的第一保护模块实现了对上拉模块的静电防护。利用本公开实施例提供的电路结构,可以有效提升数据传输电路的静电防护能力,提高cdm测试的等级。

技术特征:1.一种数据传输电路,其特征在于,所述数据传输电路包括:

2.根据权利要求1所述的电路,其特征在于,所述第一保护模块包括:

3.根据权利要求1所述的电路,其特征在于,所述上拉模块包括:

4.根据权利要求3所述的电路,其特征在于,所述上拉模块还包括:

5.根据权利要求4所述的电路,其特征在于,所述上拉模块还包括:

6.根据权利要求5所述的电路,其特征在于,所述上拉模块还包括:

7.根据权利要求1至6任一所述的电路,其特征在于,所述下拉模块包括:

8.根据权利要求7所述的电路,其特征在于,所述下拉模块还包括:

9.根据权利要求8所述的电路,其特征在于,所述下拉模块还包括:

10.根据权利要求8所述的电路,其特征在于,所述下拉模块还包括:

11.根据权利要求10所述的电路,其特征在于,所述第二保护模块包括:

12.根据权利要求7所述的电路,其特征在于,所述所述下拉模块还包括:

13.根据权利要求1所述的电路,其特征在于,所述静电保护模块包括:

14.根据权利要求13所述的电路,其特征在于,所述静电保护模块还包括:

15.根据权利要求13所述的电路,其特征在于,所述静电保护模块还包括:

16.一种存储器,其特征在于,包括:

技术总结本公开实施例公开了一种数据传输电路及存储器。该数据传输电路包括数据传输端,至少用于输出读取的数据;上拉模块,与所述数据传输端连接,用于提供输出第一电平数据时所需的电压信号;第一保护模块,连接在第一电源端与所述上拉模块之间,用于防止所述上拉模块中的器件击穿;下拉模块,连接第二电源端和所述数据传输端,用于提供输出第二电平数据时所需的电压信号;静电保护模块,分别连接所述第一电源端、第二电源端和所述数据传输端,用于泄放所述数据传输电路中的静电电荷。技术研发人员:朱玲受保护的技术使用者:长鑫存储技术有限公司技术研发日:技术公布日:2024/3/11本文地址:https://www.jishuxx.com/zhuanli/20240731/183754.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表