自动化测试结构及ATE设备的制作方法

- 国知局

- 2024-07-31 19:48:39

本发明涉及自动化测试,尤其涉及自动化测试结构及ate设备。

背景技术:

1、目前市场上的nand flash测试设备大多采用专用主控芯片来构建,设计了特定的测试板。由于主控芯片的功能是固定的,因此这些设备不具备可替换功能的能力,导致设备的功能比较单一,不能做到一机多用。

技术实现思路

1、本发明的主要目的在于提供一种自动化测试结构及ate设备,旨在解决现有技术中主控建构的ate设备功能单一,无法多用途使用的缺点的技术问题。

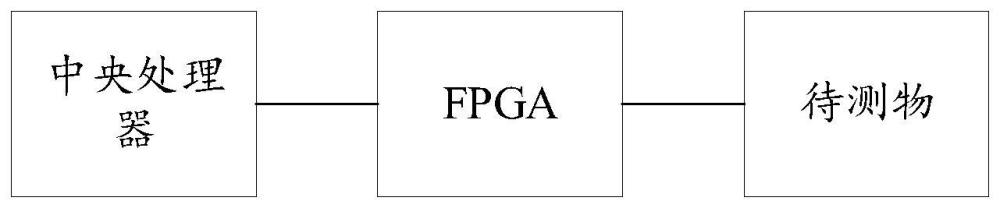

2、为实现上述目的,本发明提供一种自动化测试结构,所述自动化测试结构包括:中央处理器和fpga;

3、其中,所述fpga与所述中央处理器连接,所述fpga还通过待测物接口板与待测物连接;

4、所述中央处理器,用于检测所述待测物,并基于所述待测物的类型输出测试指令至所述fpga;

5、所述fpga,用于在接收到所述测试指令时,基于所述测试指令将主控代码切换至所述待测物对应的主控代码,并基于所述主控代码测试对应的待测物。

6、可选地,所述fpga包括:主控切换模块、芯片测试控制器和存储模块;

7、其中,所述主控切换模块分别与所述中央处理器、所述芯片测试控制器和所述存储模块连接,所述芯片测试控制器通过所述待测物接口板与所述待测物连接;

8、所述存储模块,用于存储不同类型待测物测试对应的主控代码;

9、所述主控切换模块,用于在接收到所述测试指令时,基于所述测试指令调用存储在所述存储模块中的主控代码;

10、所述主控切换模块,还用于基于所述主控代码重新编排所述芯片测试控制器;

11、所述芯片测试控制器,用于在编排完成后,通过所述待测物接口板测试对应的待测物。

12、可选地,所述存储模块包括:nand闪存控制器;

13、所述nand闪存控制器与所述主控切换模块连接;

14、所述nand闪存控制器,用于存储nand闪存测试所需的主控代码。

15、可选地,所述存储模块包括:emmc控制器;

16、所述emmc控制器与所述主控切换模块连接;

17、所述emmc控制器,用于存储emmc测试所需的主控代码。

18、可选地,所述存储模块包括:sd卡控制器;

19、所述sd卡控制器与所述主控切换模块连接;

20、所述sd卡控制器,用于存储sd卡测试所需的主控代码。

21、可选地,所述存储模块包括:spi存储器控制器;

22、所述spi存储器控制器与所述主控切换模块连接;

23、所述spi存储器控制器,用于存储spi存储器测试所需的主控代码。

24、可选地,所述中央处理器还用于检测所述fpga中的状态寄存器,并基于所述fpga中的状态寄存器判断所述待测物对应的主控代码的切换是否完成。

25、此外,为实现上述目的,本发明还提供一种ate设备,所述ate设备包括上述任一项所述的自动化测试结构。

26、本发明公开了一种自动化测试结构,所述结构包括:中央处理器和fpga;其中,所述fpga与所述中央处理器连接,所述fpga还通过待测物接口板与待测物连接;所述中央处理器,用于检测所述待测物,并基于所述待测物的类型输出测试指令至所述fpga;所述fpga,用于在接收到所述测试指令时,基于所述测试指令将主控代码切换至所述待测物对应的主控代码,并基于所述主控代码测试对应的待测物。本发明通过fpga在接收到所述测试指令时,基于所述测试指令将主控代码切换至所述待测物对应的主控代码,并基于所述主控代码测试对应的待测物,有效地解决了传统基于特定导向芯片的测试设备功能单一、无法多用途使用的问题。

技术特征:1.一种自动化测试结构,其特征在于,所述结构包括:中央处理器和fpga;

2.如权利要求1所述的自动化测试结构,其特征在于,所述fpga包括:主控切换模块、芯片测试控制器和存储模块;

3.如权利要求2所述的自动化测试结构,其特征在于,所述存储模块包括:nand闪存控制器;

4.如权利要求2所述的自动化测试结构,其特征在于,所述存储模块包括:emmc控制器;

5.如权利要求2所述的自动化测试结构,其特征在于,所述存储模块包括:sd卡控制器;

6.如权利要求2所述的自动化测试结构,其特征在于,所述存储模块包括:spi存储器控制器;

7.如权利要求1所述的自动化测试结构,其特征在于,所述中央处理器还用于检测所述fpga中的状态寄存器,并基于所述fpga中的状态寄存器判断所述待测物对应的主控代码的切换是否完成。

8.一种ate设备,其特征在于,所述ate设备包括权利要求1至7中任一项所述的自动化测试结构。

技术总结本发明涉及自动化测试技术领域,尤其涉及自动化测试结构及ATE设备,该结构包括:中央处理器和FPGA;其中,FPGA与中央处理器连接,FPGA还通过待测物接口板与待测物连接;中央处理器,用于检测待测物,并基于待测物的类型输出测试指令至FPGA;FPGA,用于在接收到测试指令时,基于测试指令将主控代码切换至待测物对应的主控代码,并基于主控代码测试对应的待测物。本发明通过FPGA在接收到测试指令时,基于测试指令将主控代码切换至待测物对应的主控代码,并基于主控代码测试对应的待测物,有效地解决了传统基于特定导向芯片的测试设备功能单一、无法多用途使用的问题。技术研发人员:郭寂波受保护的技术使用者:芯测通(深圳)半导体有限公司技术研发日:技术公布日:2024/4/17本文地址:https://www.jishuxx.com/zhuanli/20240731/184155.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表