用于存储器内管线处理的具有单或双电阻器存储器元件的分区存储器架构的制作方法

- 国知局

- 2024-07-31 19:50:14

本发明涉及存储器内处理(in-memory processing),更具体地涉及用于存储器内处理的存储器架构的实施例。

背景技术:

1、各种处理应用(例如,图像处理应用、语音处理应用或其他机器学习(ml)或人工智能(ai)处理)采用认知计算,特别是神经网络(nn)(例如,用于识别和分类)。本领域技术人员将认识到,nn是深度学习算法,其中算法中执行的约90%的计算是乘积累加(mac)运算。例如,在用于图像处理的nn中,各种mac运算用于计算输入(也称为激活)(其为感受野(receptive field)中像素的识别强度值)与跟感受野大小相同的滤波器矩阵(也称为核(kernel))的权重的乘积,并进一步计算乘积的和。这些计算被称为点积计算。历史上,软件解决方案(software solution)被用来计算nn。最近,具有硬件实现的nn的处理器,特别是具有存储器实现的nn的处理器已经被开发出来,以提高处理速度。然而,这种存储器实现的nn通常需要大的存储器基元(memory cell)阵列(即,具有大量行和列的存储器基元的阵列)来实现,并且随着这种nn的复杂性增加,阵列的尺寸也增加。不幸的是,阵列尺寸的这种增加会导致局部电压(“ir”)降的增加,从而导致处理错误。

技术实现思路

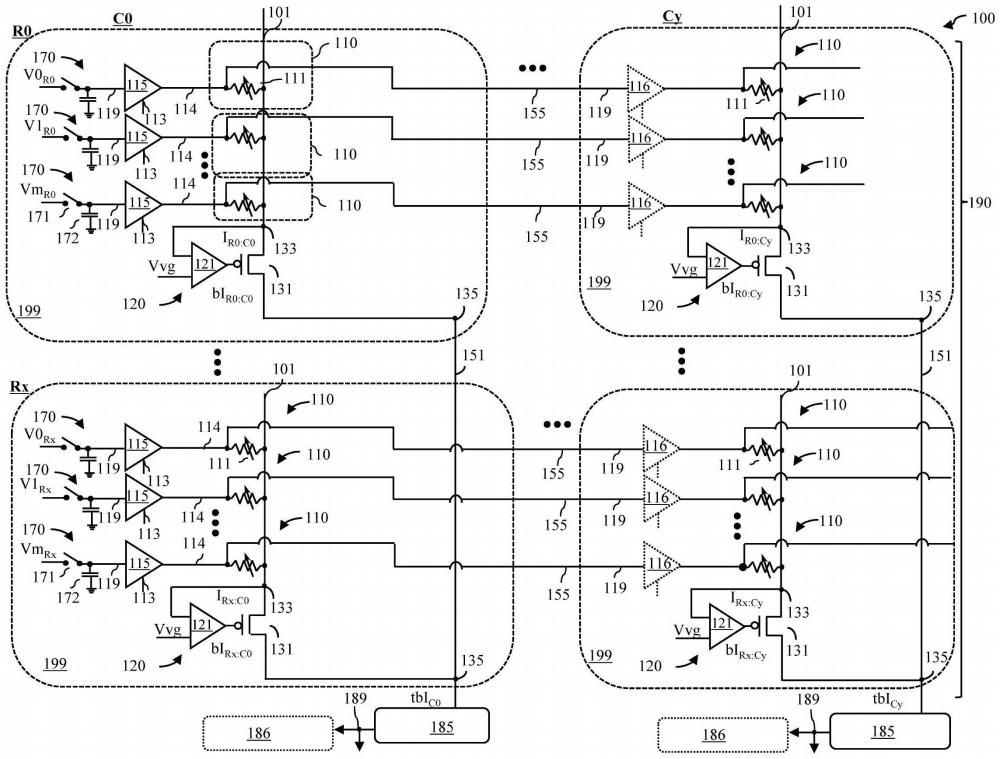

1、一般地,本文公开的结构的实施例可包括按行和列排列的存储体(memory bank)的阵列。存储体可以按行和列排列。每个存储体可以包括输入节点。每个存储体还可以包括位线。每个存储体还可以包括分别连接到输入节点的存储器元件,并且每个存储器元件可以包括连接在对应输入节点和位线之间的可编程电阻器。每个存储体还可以包括连接到位线的反馈缓冲电路。此外,每行存储体可以包括初始存储体(即,该行中的第一个存储体),并且每个初始存储体可以包括连接在输入节点和存储器元件之间的放大器以及连接到输入节点的跟踪和保持器件(th)。

2、本文公开的结构的一些实施例可具体地包括具有单电阻器存储器元件的存储体的阵列。也就是说,该结构可以包括按行和列排列的存储体的阵列。每个存储体可以包括多个输入节点、单个输出节点和单个位线。每个存储体还可以包括分别连接到输入节点的多个存储器元件。具体地,每个存储器元件可以包括单个可编程电阻器,其连接在对应输入节点和位线之间。每个存储体还可以包括反馈缓冲电路,反馈缓冲电路连接到位于位线的一端处的偏置节点并且还连接到输出节点。另外,每行存储体可以包括初始存储体(即,该行中的第一个存储体)和在初始存储体下游的至少一个附加存储体。每个初始存储体可以包括连接在输入节点和存储器元件之间的放大器以及连接到输入节点的th。

3、本文公开的结构的其他实施例可包括具有双电阻器存储器元件的存储体的阵列。也就是说,该结构可以包括按行和列排列的存储体的阵列。每个存储体可以包括多个输入节点、两个输出节点(即,第一输出节点和第二输出节点)和两个位线(即,第一位线和第二位线)。每个存储体还可以包括分别连接到输入节点的多个双电阻器存储器元件。每个双电阻器存储器元件可以包括两个可编程电阻器(即,第一可编程电阻器和第二可编程电阻器)。第一可编程电阻器可以连接在对应输入节点和第一位线之间。第二可编程电阻器可以连接在相同的对应输入节点和第二位线之间。每个存储体还可以包括两个反馈缓冲电路(即,第一反馈缓冲电路和第二反馈缓冲电路)。第一反馈缓冲电路可以连接到位于第一位线的一端处的第一偏置节点并且连接到第一输出节点。第二反馈缓冲电路可以连接到位于第二位线的一端处的第二偏置节点并且连接到第二输出节点。此外,存储体的每一行可以包括初始存储体(即,该行中的第一个存储体)和在该附加存储体下游的至少一个附加存储体。每个初始存储体可以包括连接在输入节点和存储器元件之间的放大器以及连接到输入节点的th。

技术特征:1.一种结构,包括:

2.根据权利要求1所述的结构,

3.根据权利要求2所述的结构,

4.根据权利要求1所述的结构,其中,在每个存储体内,所述反馈缓冲电路将所述位线偏置到虚拟地电压。

5.一种结构,包括:

6.根据权利要求5所述的结构,

7.根据权利要求6所述的结构,其中,每个放大器接收所述存储电压作为输入电压,将虚拟地电压加到所述输入电压,以及输出等于所述输入电压和所述虚拟地电压之和的电平移位输入电压。

8.根据权利要求7所述的结构,还包括:

9.根据权利要求6所述的结构,

10.根据权利要求9所述的结构,还包括分别用于所述列的电流-电压转换器,其中,用于每列的每个电流-电压转换器连接到用于该列的所述列互连线,从用于该列的所述列互连线接收等于来自该列中所述存储体的所述缓冲的存储体特定的输出电流之和的列特定的输出电流,以及基于所述列特定的输出电流来输出列特定的模拟输出电压。

11.根据权利要求10所述的结构,其中,所述列特定的模拟输出电压表示点积计算的解。

12.根据权利要求6所述的结构,其中,在每个存储器元件内,所述可编程电阻器能够编程到多个不同电阻状态中的任何一个,以存储作为编程的电阻状态的函数的权重值。

13.根据权利要求6所述的结构,其中,每个存储器元件的所述可编程电阻器包括电阻式随机存取存储器型电阻器、相变存储器型电阻器和磁隧道结型电阻器中的任何一者。

14.一种结构,包括:

15.根据权利要求14所述的结构,

16.根据权利要求15所述的结构,其中,每个放大器接收所述存储电压作为输入电压,将虚拟地电压加到所述输入电压,以及输出等于所述输入电压和所述虚拟地电压之和的电平移位输入电压。

17.根据权利要求16所述的结构,还包括:

18.根据权利要求14所述的结构,

19.根据权利要求18所述的结构,还包括分别用于所述列的减法器,

20.根据权利要求14所述的结构,其中,在每个双电阻器存储器元件内,所述第一可编程电阻器和所述第二可编程电阻器能够编程到多个不同电阻状态中的任何一个,以存储作为表示正权重值的所述第一可编程电阻器的编程的第一电阻状态和表示负权重值的所述第二可编程电阻器的编程的第二电阻状态的函数的总权重值。

技术总结本公开涉及用于存储器内管线处理的具有单或双电阻器存储器元件的分区存储器架构。用于存储器内管线处理的结构包括存储体阵列。每个存储体包括分别连接在输入节点和位线(例如用于单电阻器存储器元件的单个位线和用于双电阻器存储器元件的第一和第二位线)之间的单或双电阻器存储器元件。反馈缓冲器连接到每个位线和每个存储体中的对应输出节点,列互连线连接同一列中所有存储体的对应输出节点。每行中的初始存储体包括连接在输入节点和存储器元件之间的放大器以及连接到输入节点的跟踪和保持器件TH以便于管线处理。放大器的输出还通过行互连线连接到同一行中下游存储体中的存储器元件。可选地电压缓冲器连接到行互连线并集成到至少一些存储体中。技术研发人员:V·P·戈皮纳特,P·帕瓦朗德受保护的技术使用者:格芯(美国)集成电路科技有限公司技术研发日:技术公布日:2024/4/17本文地址:https://www.jishuxx.com/zhuanli/20240731/184263.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表