具有对原始存储器单元的安全检测的非易失性存储器系统的制作方法

- 国知局

- 2024-07-31 20:02:26

本文中所描述的主题的实施例大体上涉及电子存储器系统,且更具体地,涉及被配置成安全地检查存储器单元是否曾被写入数据的存储器系统。

背景技术:

1、许多装置使用非易失性存储器(nvm)来存储即使装置断电也必须由装置保存的信息。例如,智能卡系统在小型嵌入式集成电路(例如,嵌入在口袋大小的卡中)使用非易失性存储器来存储标识信息。该信息可以是私有的、专有的或秘密的,从而使智能卡能够实施支付、数据存储或认证功能等高级功能。必须保护此类秘密数据免经未授权的存取;智能卡、受信任平台模块和类似装置可以使用嵌入式nvm,以避免需要使用外部/外围设备来存取存储器。

2、但是,对装置的电气测试需要在nvm生产出来后进行的测试程序中通过测试硬件存取所述nvm。大多数情况下,已生产出但未经测试的存储器内容是未知的;因此,读取存储器内容以区分已测试装置和未经测试装置只能通过将特定数据模式写入存储器的特定位置来完成,这预计在生产过程中不会偶然出现。因而,测试完成后必须禁用测试存取,以避免潜在的安全威胁。

3、某些类型的nvm(例如电阻式随机存取存储器(rram))会经历“形成”过程,所述过程包括通过电气方式制备存储器单元以使得有数据写入到所述存储器单元。“形成”是生产后即刻开始的测试程序的一部分。在形成之前,存储器单元表现出不同的特性,例如极高的电阻,所述特性在形成过程之后消失。有利地,以电气方式测量这些特性可将预形成的或“原始”的存储器单元与保存或被制备成保存数据的存储器单元区分开。

4、可在形成存储器单元之前进行包括“原始”检查的测试程序;因此,检查将在启动过程期间或在测试接口可供使用之前进行。如果检查的时间已知或可合理地进行猜测,则检查可能容易受到攻击(例如,黑客的攻击)。当nvm实际上被写入秘密数据时,适时的攻击可能会欺骗测试接口将nvm状况读取为“原始”状态。需要有技术来保护“原始存储器”检查免受这种方式的攻击。

技术实现思路

1、根据本发明的第一方面,提供一种系统,包括:

2、测试电路,所述测试电路被配置成耦合到存储器装置中的非易失性存储器单元的多个阵列中的第一阵列和第二阵列,每个存储器单元具有已形成状态或未形成状态,其中:

3、在所述已形成状态中,所述存储器单元已经历用于将数据存储于所述存储器单元中的写入操作;并且

4、在所述未形成状态中,所述存储器单元从未经历写入操作;

5、所述测试电路包括:

6、偏置电路系统,所述偏置电路系统被配置成使所述第一阵列的第一存储器单元经历一个或多个偏置条件;以及

7、感测放大器,所述感测放大器电连接到所述偏置电路系统,并且被配置成产生对应于所述第一存储器单元在所述一个或多个偏置条件下测得的电学特性的值;以及

8、处理器,所述处理器被配置成执行包括以下步骤的原始存储器检查:

9、使得所述测试电路向所述第一存储器单元施加第一偏置条件;

10、从所述测试电路获取对应于所述第一存储器单元在所述第一偏置条件下测得的所述电学特性的所述值作为第一值;

11、基于所述第一值确定所述第一存储器单元的所述状态,其中所述第一值高于阈值指示所述状态已形成,所述第一值低于所述阈值指示所述状态未形成;

12、当所述第一存储器单元的所述状态已形成时,执行与所述存储器装置未通过所述原始存储器检查相关联的一个或多个未通过模式动作;并且

13、当所述第一存储器单元的所述状态未形成时,执行验证动作以确认所述测试电路工作正常。

14、在一个或多个实施例中,为了将所述测试电路耦合到所述第一阵列和所述第二阵列,所述感测放大器被配置成电连接到所述第一阵列的活动位线和所述第二阵列的参考位线以将所述位线作为所述感测放大器的输入,所述活动位线连接到所述第一存储器单元;

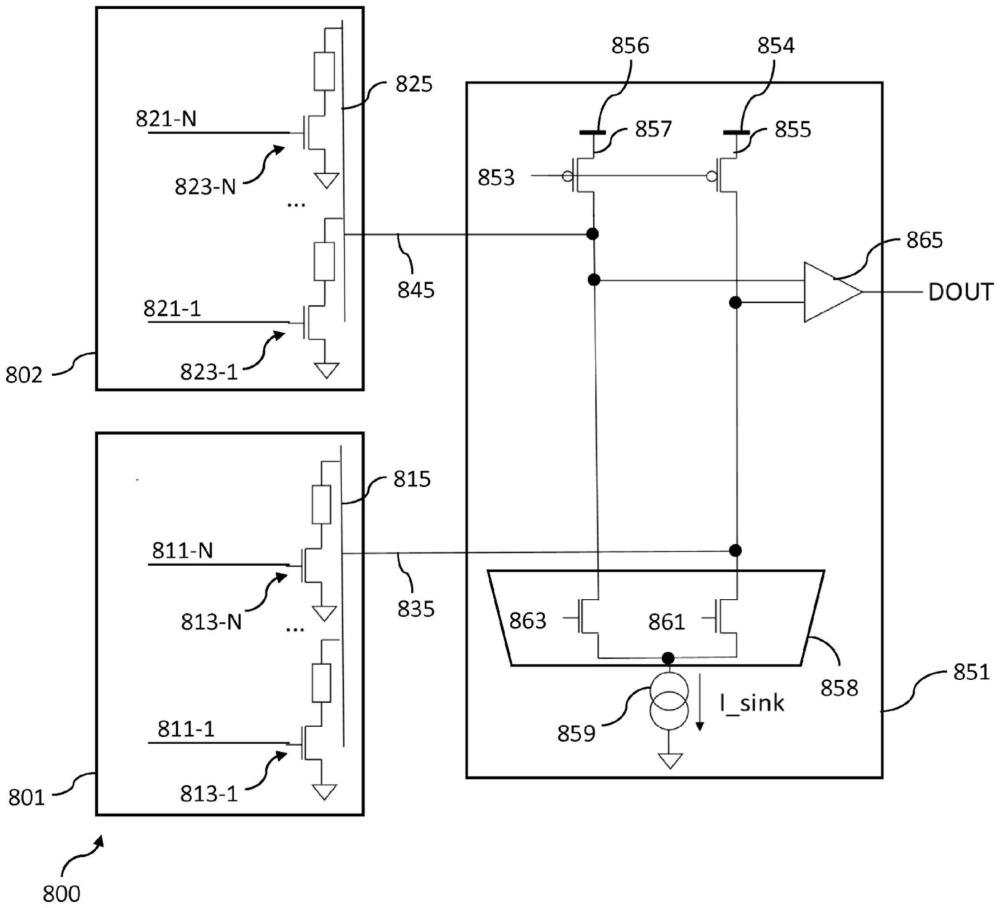

15、所述偏置电路系统包括:

16、电气组件,所述电气组件能用于向所述活动位线和所述参考位线施加电压;以及

17、电流阱,所述电流阱以可切换方式连接到所述参考位线;并且

18、使得所述测试电路向所述第一存储器单元施加所述第一偏置条件包括以下步骤:

19、使得所述电气组件向连接到所述第一存储器单元的所述活动位线和连接到所述第二阵列的所述参考位线施加所述电压;并且

20、并行地,使得所述电流阱给连接到所述第二阵列的所述参考位线充电,并且使得所述第一阵列的第一字线激活,所述第一字线连接到所述第一存储器单元,所述感测放大器响应性地比较所述活动位线与所述参考位线的对应放电率以产生所述值;

21、其中在所述活动位线比所述参考位线更快地放电的情况下所述值指示所述第一存储器单元已形成,在所述参考位线比所述活动位线更快地放电的情况下所述值指示所述第一存储器单元未形成。

22、在一个或多个实施例中,所述处理器另外被配置成执行包括以下步骤的安全检查:

23、使得所述测试电路向所述第一存储器单元施加第二偏置条件,所述第二偏置条件被配置成产生期望值作为对应于所述第一存储器单元在所述第二偏置条件下测得的所述电学特性的所述值,所述期望值与所述第一存储器单元处于所述已形成状态相关联;

24、从所述测试电路获取对应于所述第一存储器单元在所述第二偏置条件下测得的所述电学特性的所述值作为第二值;

25、确定所述第二值是否是所述期望值;

26、响应于确定所述第二值是所述期望值,产生指示所述第一存储器单元包括原始存储器单元的检查信号;以及

27、响应于确定所述第二值不是所述期望值,执行所述未通过模式动作中的一个或多个。

28、在一个或多个实施例中,所述感测放大器被配置成在所述感测放大器的第一输入处电连接到所述第一阵列的活动位线且在所述感测放大器的第二输入处电连接到所述第二阵列的参考位线;

29、所述感测放大器另外被配置成在任何所述偏置条件下,响应性地比较所述第一输入和所述第二输入上的对应电导率以产生所述值;

30、使得所述测试电路向所述第一存储器单元施加所述第一偏置条件包括并行地进行以下步骤:

31、激活所述第一阵列的选定字线,所述选定字线连接到所述第一存储器单元;以及

32、使得所述测试电路将负载连接到所述参考位线;并且

33、使得所述测试电路向所述第一存储器单元施加所述第二偏置条件包括并行地进行以下步骤:

34、激活所述第一阵列的选定字线,所述选定字线连接到所述第一存储器单元;以及

35、使得所述测试电路将所述负载连接到所述活动位线。

36、在一个或多个实施例中,所述处理器另外被配置成:

37、在所述存储器装置的启动过程期间执行所述原始存储器检查和所述安全检查;

38、循序地执行所述原始存储器检查和所述安全检查作为安全原始存储器检查;

39、对所述第一存储器单元执行预定重复次数的所述安全原始存储器检查;并且

40、针对所述预定重复次数中的每次重复,随机地确定所述安全原始存储器检查内的所述原始存储器检查和所述安全检查的序列。

41、根据本发明的第二方面,提供一种系统,包括:

42、用于包括非易失性存储器单元的第一阵列的存储器装置的测试电路,所述第一阵列中的每个存储器单元处于与所述存储器单元已经历用于测试数据或将数据存储在所述存储器单元中的写入操作相关联的第一状态或与所述存储器单元从未经历写入操作相关联的第二状态;以及

43、处理器,所述处理器被配置成执行对所述存储器装置的原始存储器检查,所述原始存储器检查包括以下步骤:

44、使得所述测试电路向非易失性存储器单元的所述第一阵列中的第一存储器单元施加第一偏置条件;

45、从所述测试电路获取对应于所述第一存储器单元在所述第一偏置条件下测得的电学特性的第一值;

46、基于所述第一值确定所述第一存储器单元处于所述第一状态还是所述第二状态;

47、响应于确定所述第一存储器单元处于所述第一状态,产生指示所述存储器装置未通过所述原始存储器检查的原始检查信号;以及

48、响应于确定所述第一存储器单元处于所述第二状态,进行以下步骤:

49、产生指示所述第一存储器单元通过所述原始存储器检查的所述原始检查信号;以及

50、执行验证动作以确认所述测试电路工作正常。

51、在一个或多个实施例中,确定所述第一存储器单元处于所述第一状态还是所述第二状态包括:

52、将所述第一值与阈值进行比较,所述阈值被选择来基于所述非易失性存储器单元的所述电学特性区分处于所述第一状态的非易失性存储器单元与处于所述第二状态的非易失性存储器单元;

53、响应于确定所述第一值不满足所述阈值,确定所述第一存储器单元处于所述第一状态;以及

54、响应于确定所述第一值满足所述阈值,确定所述第一存储器单元处于所述第二状态。

55、在一个或多个实施例中,所述非易失性存储器单元包括电阻式随机存取存储器单元,并且所述电学特性包括所述存储器单元的电阻。

56、在一个或多个实施例中,所述电学特性包括所述存储器单元的电导率,并且所述阈值在零与二微安之间,包括零和二微安。

57、在一个或多个实施例中,所述处理器另外被配置成执行对所述存储器装置的安全检查,所述安全检查包括以下步骤:

58、使得所述测试电路向所述第一存储器单元施加第二偏置条件;

59、从所述测试电路获取对应于所述第一存储器单元在所述第二偏置条件下测得的所述电学特性的第二值;

60、确定所述第二值是否匹配与施加所述第二偏置条件相关联的期望值;

61、响应于确定所述第二值匹配所述期望值,产生指示通过所述安全检查的安全检查信号;以及

62、响应于确定所述第二值不匹配所述期望值,产生指示未通过所述安全检查的所述安全检查信号。

63、在一个或多个实施例中,所述验证动作包括执行所述安全检查。

64、在一个或多个实施例中,所述处理器被配置成执行所述原始存储器检查和所述安全检查作为对所述第一存储器单元的一对测试,并且其中所述验证动作包括确定通过对所述第一存储器单元的所述安全检查。

65、在一个或多个实施例中,所述存储器装置另外包括非易失性存储器单元的第二阵列,并且所述测试电路被配置成电连接到所述第一阵列的活动位线且电连接到所述第二阵列的参考位线,所述活动位线连接到所述第一存储器单元,并且其中所述测试电路包括:

66、偏置电路系统,所述偏置电路系统电连接到所述活动位线和所述参考位线且能在所述活动位线与所述参考位线之间切换,且被配置成使所述第一存储器单元经历所述第一偏置条件和所述第二偏置条件;以及

67、感测放大器,所述感测放大器电连接到所述偏置电路系统,并且被配置成产生对应于所述第一存储器单元在所述第一偏置条件和所述第二偏置条件中的任一者下测得的所述电学特性的值。

68、在一个或多个实施例中,所述处理器被配置成操作所述偏置电路系统以可切换地将所述活动位线和所述参考位线中的任一者连接到一个或多个电压源并连接到一个或多个电流阱;

69、使得所述测试电路向所述第一存储器单元施加所述第一偏置条件包括以下步骤:

70、使得所述偏置电路系统在没有连接负载的情况下给所述存储器装置的所述第一阵列的所述活动位线和所述第二阵列的所述参考位线预充电;以及

71、并行地,激活所述第一阵列的第一字线且连接电流阱以给所述参考位线充电;以及

72、使得所述测试电路向所述第一存储器单元施加所述第二偏置条件包括以下步骤:

73、使得所述偏置电路系统在没有连接负载的情况下给所述第一阵列的所述活动位线和所述第二阵列的所述参考位线预充电;以及

74、并行地,激活所述第一阵列的所述第一字线且连接所述电流阱以给所述活动位线充电。

75、在一个或多个实施例中,所述处理器被配置成操作所述偏置电路系统以向所述参考位线施加参考电流并且可切换地向所述活动位线和所述参考位线中的任一者施加偏移电流;

76、使得所述测试电路向所述第一存储器单元施加所述第一偏置条件包括使得所述偏置电路系统向所述活动位线施加所述偏移电流以产生所述第一偏置条件的正的净电流;并且

77、使得所述测试电路向所述第一存储器单元施加所述第二偏置条件包括使得所述偏置电路系统向所述参考位线施加所述偏移电流以产生所述第二偏置条件的几乎负的净电流。

78、根据本发明的第三方面,提供一种方法,包括:

79、使用测试电路向非易失性存储器单元的第一阵列中的第一存储器单元施加第一偏置条件;

80、从所述测试电路获取对应于所述第一存储器单元的电学特性的第一值;

81、将所述第一值与和所述电学特性相关联的阈值进行比较以确定所述第一存储器单元是已被写入数据的已形成存储器单元或从未被写入数据的未形成存储器单元中的一者;

82、响应于确定所述第一存储器单元是已形成存储器单元,产生指示包括所述第一阵列的存储器管芯不是原始存储器管芯的原始存储器检查信号;以及

83、响应于确定所述第一存储器单元是未形成存储器单元,产生用以指示所述第一存储器单元通过原始存储器检查的所述原始存储器检查信号。

84、在一个或多个实施例中,所述方法另外包括:

85、使用所述测试电路向所述第一存储器单元施加第二偏置条件;

86、从所述测试电路获取对应于所述第一存储器单元的所述电学特性的第二值;

87、将所述第二值与和所述第二偏置条件相关联的期望值进行比较;

88、响应于确定所述第二值匹配所述期望值,产生指示通过安全检查的安全检查信号;以及

89、响应于确定所述第二值不匹配所述期望值,产生用以指示未通过所述安全检查的所述安全检查信号。

90、在一个或多个实施例中,所述方法另外包括循序地执行所述原始存储器检查和所述安全检查作为对所述第一存储器单元的安全原始检查。

91、在一个或多个实施例中,所述方法另外包括随机地确定所述原始存储器检查和所述安全检查的序列。

92、在一个或多个实施例中,所述方法另外包括执行预定重复次数的对所述第一存储器单元的所述安全原始检查。

93、本发明的这些和其它方面将根据下文中所描述的实施例显而易见,且参考这些实施例予以阐明。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185174.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表