无需供电情况下存储器向测试设备中的插入的自主检测的制作方法

- 国知局

- 2024-07-31 20:08:54

本发明涉及无需供电的情况下,存储器向测试设备的插入的自主检测。

背景技术:

1、以下描述包括在理解本发明时可能有用的信息。不承认本文提供的任何信息是现有技术或与当前要求保护的发明相关,或者明确或隐含引用的任何出版物是现有技术。

2、计算机系统利用易失性和非易失性存储器来存储和检索数据。易失性存储器用于存储和检索持续时间较短的数据,并且作为临时存储,并且仅在电源未断开时保留数据。一旦电源被关闭,易失性存储器就丢失其数据。另一方面,非易失性存储器用于存储和检索持续时间较长的数据,并且作为永久存储,并且即使在电源被关闭之后也会保留其数据。

3、与传统的硬盘驱动器(hdd)器件或固态驱动器(ssd)器件相比,将数据存储和检索到易失性存储器中的主要目的是缩短访问时间。一般而言,易失性存储器访问时间比传统hdd或ssd器件快至少一个量级。将数据存储和检索到非易失性存储器中的主要目的是在不正常断电后有助于访问,或者允许其他计算机系统访问相同的数据。

4、由于对较高速度的持续需求,大多数计算机系统当前利用大量易失性存储器来临时存储数据,以及大量非易失性存储器来存储和检索较长时间段(如秒、分钟、小时、天、月或甚至年)的数据。

5、为了提供稳定、可靠、安全和确定性操作的计算机系统,它必须利用可依赖的、稳定的和可操作的一个或更多个易失性和/或非易失性存储器产品。为了确保这些合格,计算机系统的制造商或它们的供应商必须利用测试每个单独的易失性和非易失性存储器部件的成功的、可依赖的和可靠的测试环境。

6、易失性和非易失性存储器可以由通过特定光刻工艺制造的半导体晶圆的单独的芯片组装而成。一般来说,基于这些晶圆和它们的芯片的电压(dc电平)和定时(ac电平)参数的单独规范,对测试这些晶圆和它们的芯片进行了适当的电操作和功能测试。一旦在晶圆内识别出一个或更多个良好的已知芯片,则随后对这些芯片进行封装工艺。

7、封装体可以涉及一个或更多个芯片。例如,单个芯片部件被称为单片部件,而半导体公司还通常生产具有双芯片、四芯片和八芯片以及甚至更高的组合的封装体。

8、如在本文中所使用的,术语“存储器产品”包括包含易失性和/或非易失性存储器封装体的一个或更多个子系统的存储器模块两者、以及还有包括存储器封装体的所有器件。然后将这些产品放入计算系统中,以提供易失性和/或非易失性存储器容量。

9、鉴于现代存储器封装体的复杂性,需要对单独的易失性和非易失性封装体进行稳定性测试。许多公司提供通用的半导体测试设备,半导体测试设备利用定制的专用集成电路(asic)或现场可编程门阵列(fpga)来构建它们的测试仪产品。设计并微调这些测试仪,以对特定产品、电压、频率和温度进行ac和dc电平测试。一般来说,这些测试仪可以仅进行易失性存储器测试或仅进行非易失性存储器测试。这些测试仪还被设计为使用固定的功能测试模式进行操作,以对照现有行业标准进行测试。

10、关于存储器测试器件的另外的信息可以在于2022年11月10日提交的美国专利申请序列号17/985037中找到,其全部公开内容通过引用并入本文。在该参考文献中的术语的定义或使用与在本文中所提供的该术语的定义不一致或相反的情况下,则认为在本文中所提供的该术语的定义或使用是受控的。

11、在安装到完全组装的系统或子系统中之后,顾客然后针对其自身的一系列软件应用测试存储器产品以用于系统电平验证。无论是安装在印刷电路板(pcb)模块中或是在其他地方,安装不良存储产品的下游成本都很高,因此,测试设备的高可靠性,并且在测试仪的使用寿命内产生准确的测试结果是非常重要的。

12、一般来说,用于适当测试任何易失性和非易失性存储器测试仪中的易失性和非易失性存储器器件、封装体或模块的重要部件是封装测试插槽或pcb面板电平插槽。易失性和非易失性存储器封装体被插入封装测试插槽中,以进行适当的测试,并且易失性和非易失性存储器模块pcb被塞入pcb面板电平插槽中,以进行适当的测试。

13、因为机械引脚在插入和弹出过程中受到应力,所以封装测试插槽和pcb面板电平插槽都具有有限的使用寿命。因此,存在对用于检测封装测试插槽或pcb面板电平插槽的插入数量的装置、系统和方法的需求。

14、一种可能性是使用简单的固件(fw)或软件过程,结合微控制器、有限状态机(fsm)或微处理器,以在测试仪通电时检测插入和弹出。但该方案无法在在测试仪断电时检测插入和弹出。

15、所需要的是用于自主地检测易失性和非易失性存储器测试器件的插入或弹出而无需接通测试仪电源的装置、系统和方法。

技术实现思路

1、本发明的主题提供了在不必对该测试仪器件通电的情况下,自主检测存储器器件封装体或模块的插入和/或弹出的装置、系统、以及方法。

2、一般概念是跟踪存储器产品插入到存储器测试器件的存储器产品接收部件中的次数,并且然后在达到或超过插入阈值次数时触发该存储器产品接收部件的替换。

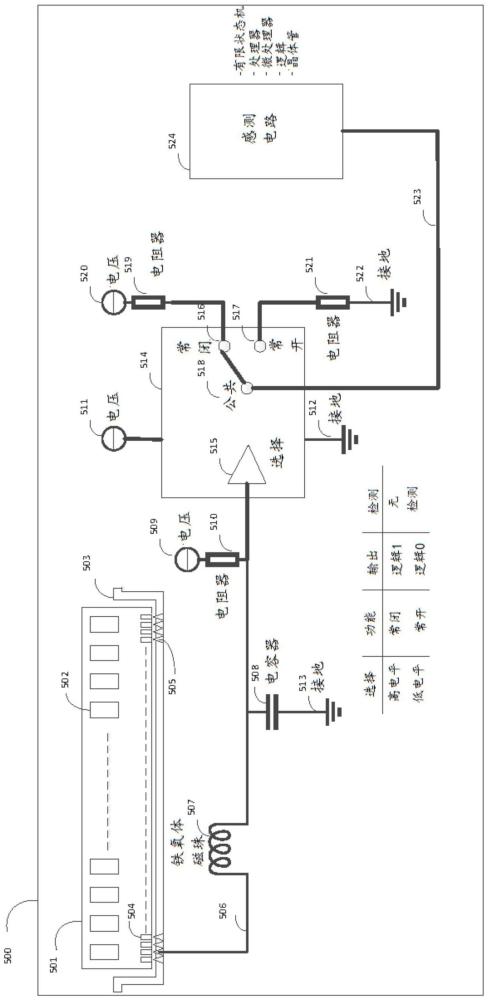

3、在本发明的优选实施例中,自主自检电路使用单刀单掷(spst)开关来将自检状态从常闭(nc)状态改变到常开(no)或从no状态改变到nc状态。用于执行该检测的引脚可以是接地(gnd或vss)引脚,以将测试仪器件的检测电路拉到接地逻辑电平。当电路检测到接地信号进入其选择引脚输入时,电路将从no位置切换到nc位置或从nc位置切换到no位置,并且因此将在测试仪器件中没有接通任何电源的情况下,检测插入到插槽中的存储器模块。

4、预期的检测电路可以是模拟的、数字的或模拟/数字组合电路。还考虑了有限状态机(fsm)电路、微控制器电路、微处理器电路、和专用集成电路(asic)电路、以及现场可编程门阵列(fpga)电路。

技术特征:1.一种存储器测试装置,包括:

2.根据权利要求1所述的存储器测试装置,其中,所述插槽阵列具有用于易失性存储器产品和非易失性存储器产品两者的插槽。

3.根据权利要求1所述的存储器测试装置,其中,所述开关在常开位置与常闭位置之间切换引脚。

4.根据权利要求1所述的存储器测试设备,还包括感测电路,所述感测电路被配置为跟踪所述存储器产品接收部件相对于所建立的阈值的使用。

5.根据权利要求4所述的存储器测试设备,其中,所述感测电路包括有限状态机fsm。

6.根据权利要求4所述的存储器测试装置,其中,所述感测电路包括处理器。

7.根据权利要求6所述的存储器测试装置,其中,所述处理器包括微处理器。

8.根据权利要求4所述的存储器测试装置,其中,所述感测电路包括纯数字逻辑电路。

9.根据权利要求4所述的存储器测试装置,其中,所述感测电路包括模拟晶体管电路。

10.一种减少存储器产品测试故障的方法,包括:

11.根据权利要求10所述的方法,还包括:即使在所述存储器测试仪断电时,所述一个或更多个存储器产品被插入到所述存储器产品接收部件中的情况下,也使用所述存储器测试仪来增加所述计数。

技术总结一种用于减少存储器产品测试故障的装置、系统和方法,包括存储器测试仪,该存储器测试仪跟踪存储器产品被插入到该存储器测试仪的存储器产品接收部件中的频率,并且当计数达到或超过阈值时,使用该信息来触发替换存储器产品接收部件。该电子器件可以被布置成即使在存储器测试仪断电时,存储器产品被插入存储器产品接收部件中,也增加该计数。技术研发人员:迈克·侯赛因·阿米迪受保护的技术使用者:睿进记忆体有限公司技术研发日:技术公布日:2024/6/30本文地址:https://www.jishuxx.com/zhuanli/20240731/185310.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表