内存检测方法及其检测系统与流程

- 国知局

- 2024-07-31 20:09:20

本申请涉及内存检测领域,特别是一种在较长观察时间下进行的内存检测方法及其检测系统。

背景技术:

1、当今半导体的外部信号通信速度和复杂性不断提高,因此,在电路板设计和保持信号完整性带来越来越多的挑战。另外,较新的信号校准方案增加了更多的复杂性。因而一旦系统出现故障,找到相关的根本原因变得越来越难。

2、目前中央处理器(central processing unit,cpu)与dram模块之间的信号传输速度大幅提高,目前已超过1ghz。因此,在主板设计时需特别设计以提高信号传输的完整性,并且,还需要在系统启动时采用合适的校准方案。举例来说,在主板启动过程中执行一个启动序列,以校准不同dram组件数据信号的运行时间差。如果启动序列不成功,cpu只会发出“无法启动 ”警告,但不会提供进一步的调试信息。

3、另一个常见问题则是cpu在长时间运行应用程序后产生挂起状态,此时用户可能看到黑屏或是计算机系统和屏幕冻结。然而,常发生的情况是,大部份的情况下dram组件皆能正常使用,但会产生偶发性的故障,而其他厂牌的dram组件却运行良好,反之亦然。造成这种故障的原因可能是用户的电路板设计不佳、信号完整性问题或用户控制器执行了非法信号,造成某些厂牌的dram组件产生故障,某些厂牌的dram则不会。

4、调试这些问题需要进行大量探测,很容易耗费数周时间,且仍无法确定根本原因。

技术实现思路

1、为解决上述技术问题,本发明提供了解决此类应用故障调试的方法。

2、本发明提供一种内存检测方法,包括下列步骤:

3、提供第一内存及第二内存,所述第一内存和所述第二内存由不同的厂商制造;

4、拆卸所述第一内存上的一个第一记忆芯片,使所述第一内存上形成测试位置,其中所述第一内存包括多个第一记忆芯片;

5、将所述第二内存上的一个第二记忆芯片装设在所述测试位置;

6、将所述第一内存设置在测试装置中驱动所述第一内存,使所述第一内存上未拆卸的第一记忆芯片产生第一信号,并使所述第一内存上的所述第二记忆芯片产生第二信号;和

7、比较所述第一信号和所述第二信号之间的差异电平,当该差异电平大于预设值时产生触发信号,以判断内存的检测结果。

8、优选地,将所述第一记忆芯片产生的第一信号和所述第二记忆芯片产生的第二信号输入差分放大器,所述差分放大器产生比较信号,其中差分放大器连接到第一记忆芯片和第二记忆芯片。

9、优选地,将所述比较信号输入低通滤波器,所述低通滤波器依据所述比较信号大于预设值的部分产生触发信号,其中差分放大器的输出端与低通滤波器的输入端相连接。

10、优选地,将所述触发信号输入阈值产生器,所述阈值产生器依据所述触发信号大于设定阈值的部分产生最终输出触发信号,其中低通滤波器的输出端与阈值产生器的输入端相连接。

11、优选地,当所述触发信号大于设定阈值,所述阈值产生器产生最终输出触发信号。

12、优选地,还包括以控制装置在第一信号及第二信号经过预设周期后,控制低通滤波器的输出端接地。

13、优选地,还包括以控制装置以地址信号或指令信号驱动第一记忆芯片及第二记忆芯片。

14、优选地,第一信号是驱动第一记忆芯片中的多个第一记忆单元后所产生的,第二信号是驱动第二记忆芯片中的多个第二记忆单元后所产生的。

15、优选地,第一信号及第二信号为时钟信号或命令信号。

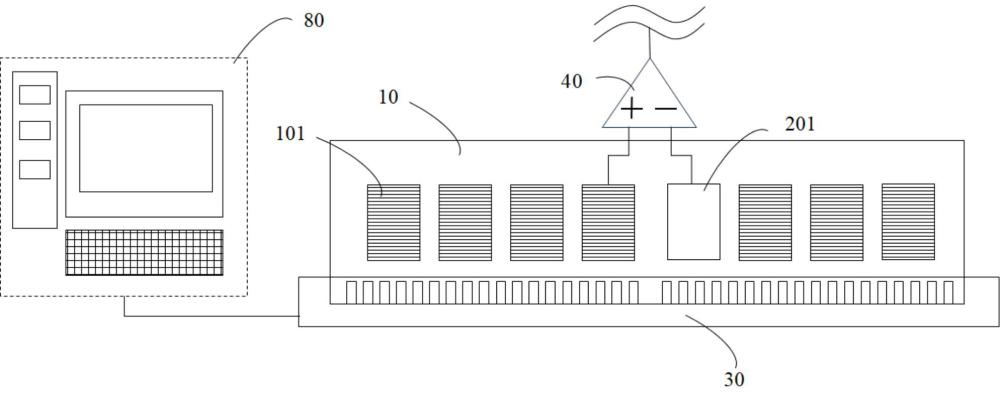

16、基于上述目的,本发明再提供一种内存检测系统,包括测试装置、差分放大器、低通滤波器以及阈值产生器。第一记忆芯片和第二记忆芯片设置在测试装置上,测试装置驱动第一记忆芯片和所述第二记忆芯片;差分放大器与第一记忆芯片和第二记忆芯片相连接;低通滤波器与差分放大器的输出端相连接;阈值产生器与低通滤波器的输出端相连接。

17、优选地,所述第一记忆芯片和所述第二记忆芯片之间的距离小于15毫米。

18、优选地,所述差分放大器的放大倍率为1至1000。

19、优选地,所述第一记忆芯片产生的第一信号和所述第二记忆芯片产生的第二信号输入所述差分放大器,所述差分放大器产生比较信号。

20、优选地,所述比较信号输入所述低通滤波器,所述低通滤波器依据所述比较信号大于预设值的部分产生触发信号。

21、优选地,所述触发信号输入所述阈值产生器,所述阈值产生器依据所述触发信号大于设定阈值的部分产生最终输出触发信号。

22、优选地,所述阈值产生器的输出端与示波器相连接,所述示波器接收所述第一记忆芯片或所述第二记忆芯片中的至少一个的地址信号、命令信号和/或数据信号中的至少一个。

23、优选地,第一记忆芯片和第二记忆芯片焊接或连接到印刷电路板或基板上,测试装置包括印刷电路板或基板。

24、优选地,差分放大器设置在印刷电路板或基板上。

25、综上,本发明的检测方法及系统在输出触发信号出现时,可以停止示波器的追踪,或是在有需要的,可以持续长时间追踪,观察这些异常的产生是否有重现性,以便进行故障根源调查。并且,可在一定时间内,例如24小时,或长时间,例如数天,有效地进行故障探测,另外本发明可以推广到其他基于闪存、现场可编程逻辑门阵列(field programmable gatearray,fpga)等的半导体系统。

26、为让本揭示的上述内容能更明显易懂,下文特举优选实施例,并配合所附图式,作详细说明如下。

技术特征:1.一种内存检测方法,其特征在于,包括:

2.根据权利要求1所述的内存检测方法,其特征在于,还包括将所述第一记忆芯片产生的第一信号和所述第二记忆芯片产生的第二信号输入差分放大器,所述差分放大器产生比较信号,其中所述差分放大器连接到所述第一记忆芯片和所述第二记忆芯片。

3.根据权利要求2所述的内存检测方法,其特征在于,还包括将所述比较信号输入低通滤波器,所述低通滤波器依据所述比较信号大于预设值的部分产生触发信号,其中所述差分放大器的输出端与低通滤波器的输入端相连接。

4.根据权利要求3所述的内存检测方法,其特征在于,还包括将所述触发信号输入阈值产生器,所述阈值产生器依据所述触发信号大于设定阈值的部分产生最终输出触发信号,其中所述低通滤波器的输出端与阈值产生器的输入端相连接。

5.根据权利要求4所述的内存检测方法,其特征在于,还包括当所述触发信号大于设定阈值,所述阈值产生器产生最终输出触发信号。

6.根据权利要求3所述的内存检测方法,其特征在于,还包括以控制装置在所述第一信号和所述第二信号经过预设周期后,控制所述低通滤波器的输出端接地。

7.根据权利要求1所述的内存检测方法,其特征在于,还包括以控制装置以地址信号或指令信号驱动所述第一记忆芯片和所述第二记忆芯片。

8.根据权利要求1所述的内存检测方法,其特征在于,所述第一信号是驱动所述第一记忆芯片中的多个第一记忆单元后所产生的,所述第二信号是驱动所述第二记忆芯片中的多个第二记忆单元后所产生的。

9.根据权利要求1所述的内存检测方法,其特征在于,所述第一信号和所述第二信号为时钟信号或命令信号。

10.一种内存检测系统,其特征在于,包括:

11.根据权利要求10所述的内存检测系统,其特征在于,所述第一记忆芯片和所述第二记忆芯片之间的距离小于15毫米。

12.根据权利要求10所述的内存检测系统,其特征在于,所述差分放大器的放大倍率为1至1000。

13.根据权利要求10所述的内存检测系统,其特征在于,所述第一记忆芯片产生的第一信号和所述第二记忆芯片产生的第二信号输入所述差分放大器,所述差分放大器产生比较信号。

14.根据权利要求13所述的内存检测系统,其特征在于,所述比较信号输入所述低通滤波器,所述低通滤波器依据所述比较信号大于预设值的部分产生触发信号。

15.根据权利要求14所述的内存检测系统,其特征在于,所述触发信号输入所述阈值产生器,所述阈值产生器依据所述触发信号大于设定阈值的部分产生最终输出触发信号。

16.根据权利要求10所述的内存检测系统,其特征在于,所述阈值产生器的输出端与示波器相连接,所述示波器接收所述第一记忆芯片或所述第二记忆芯片中的至少一个的地址信号、命令信号和/或数据信号中的至少一个。

17.根据权利要求10所述的内存检测系统,其特征在于,所述第一记忆芯片和所述第二记忆芯片焊接或连接到印刷电路板或基板上,所述测试装置包括所述印刷电路板或所述基板。

18.根据权利要求17所述的内存检测系统,其特征在于,所述差分放大器设置在所述印刷电路板或所述基板上。

技术总结一种内存检测方法及其检测系统,内存检测方法包括:提供第一内存及第二内存;拆卸第一内存上的一个第一记忆芯片;将第二内存上的一个第二记忆芯片装设在测试位置;将第一内存设置在测试装置中驱动第一内存,使第一内存的第一记忆芯片产生第一信号,并使第一内存上的所述第二记忆芯片产生第二信号;和比较第一信号和第二信号,并产生触发信号。内存检测系统,包括测试装置、差分放大器、低通滤波器以及阈值产生器。第一记忆芯片和第二记忆芯片设置在测试装置上,差分放大器与第一记忆芯片和第二记忆芯片相连接,低通滤波器与差分放大器的输出端相连接。阈值产生器与低通滤波器的输出端相连接。技术研发人员:濮必得,殷和国受保护的技术使用者:芯梦达半导体科技(济南)有限公司技术研发日:技术公布日:2024/7/4本文地址:https://www.jishuxx.com/zhuanli/20240731/185350.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表