一种多段式阻抗优化方法、内存模块及装置与流程

- 国知局

- 2024-07-31 19:55:03

本发明涉及阻抗优化,更为具体的,涉及一种多段式阻抗优化方法、内存模块及装置。

背景技术:

1、内存模块的运行速度越来越高,ddr5内存模块的运行速度可达6400mhz,讯号上升的速度较快,当讯号经过不连续的地方(例如:金手指位置至讯号线),就会出现阻抗值波动,产生讯号反射,影响信号完整性。本领域人员亟待解决这一技术问题。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供一种多段式阻抗优化方法、内存模块及装置,降低了阻抗波动影响,提高了信号完整性。

2、本发明的目的是通过以下方案实现的:

3、一种多段式阻抗优化方法,包括以下步骤:

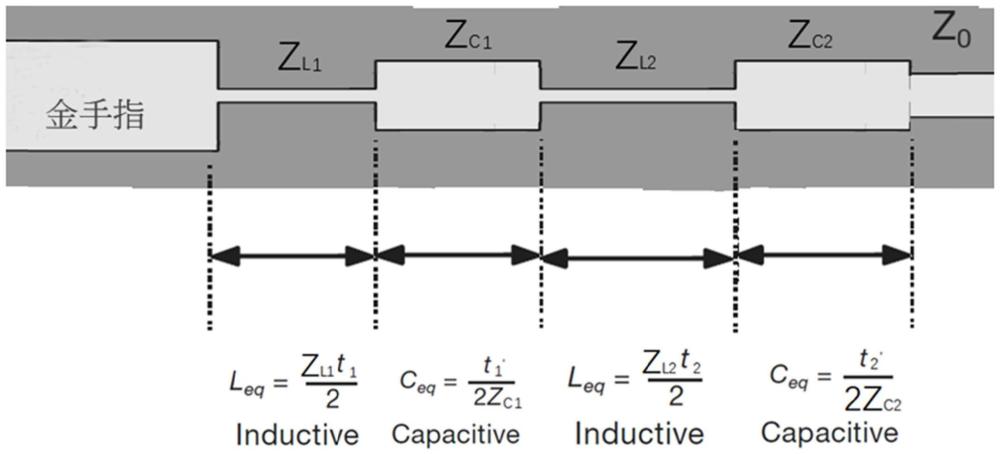

4、在阻抗不连续的地方,通过调配线宽来降低阻抗波动的情况。

5、进一步地,所述阻抗不连续的地方包括存在阻抗不连续的任何位置。

6、进一步地,所述阻抗不连续的位置包括金手指与讯号线的位置。

7、进一步地,所述调配线宽通过单段式优化调配实现。

8、进一步地,所述调配线宽通过多段式的优化调配实现。

9、进一步地,所述通过调配线宽来降低阻抗波动的情况,包括子步骤:

10、当金手指阻抗值低于目标值,在最接近的位置,收窄讯号线宽来拉回目标值,并通过多段式阻抗优化降低阻抗波动的情况;

11、当金手指阻抗值高于目标值,在最接近的位置,加宽讯号线宽来拉回目标值,并通过多段式阻抗优化降低阻抗波动的情况。

12、一种内存模块,涉及金手指与讯号线的位置,利用如上所述的多段式阻抗优化方法来降低金手指与讯号线的位置阻抗波动,从而提高讯号完整性。

13、进一步地,所述内存模块包括ddr5内存模块。

14、一种电子装置,包括如上所述的内存模块。

15、本发明的有益效果包括:

16、本发明降低了阻抗波动影响,提高了信号完整性。

技术特征:1.一种多段式阻抗优化方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的多段式阻抗优化方法,其特征在于,所述阻抗不连续的地方包括存在阻抗不连续的任何位置。

3.根据权利要求1所述的多段式阻抗优化方法,其特征在于,所述阻抗不连续的位置包括金手指与讯号线的位置。

4.根据权利要求1所述的多段式阻抗优化方法,其特征在于,所述调配线宽通过单段式优化调配实现。

5.根据权利要求1所述的多段式阻抗优化方法,其特征在于,所述调配线宽通过多段式的优化调配实现。

6.根据权利要求5所述的多段式阻抗优化方法,其特征在于,所述通过调配线宽来降低阻抗波动的情况,包括子步骤:

7.一种内存模块,涉及金手指与讯号线的位置,其特征在于,利用权利要求3所述的多段式阻抗优化方法来降低金手指与讯号线的位置阻抗波动,从而提高讯号完整性。

8.根据权利要求7所述的内存模块,其特征在于,所述内存模块包括ddr5内存模块。

9.一种电子装置,其特征在于,包括如权利要求7所述的内存模块。

10.一种电子装置,其特征在于,包括如权利要求8所述的内存模块。

技术总结本发明公开了一种多段式阻抗优化方法、内存模块及装置,属于阻抗优化技术领域,包括步骤:当金手指阻抗值低于目标值,在最接近的位置,收窄讯号线宽来拉回目标值,并通过多段式阻抗优化降低阻抗波动的情况;当金手指阻抗值高于目标值,在最接近的位置,加宽讯号线宽来拉回目标值,并通过多段式阻抗优化降低阻抗波动的情况。本发明降低了阻抗波动影响,提高了信号完整性。技术研发人员:余志新,杨志忠受保护的技术使用者:成都芯金邦科技有限公司技术研发日:技术公布日:2024/5/16本文地址:https://www.jishuxx.com/zhuanli/20240731/184690.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表