非易失性存储器的锁存型感测放大器的制作方法

- 国知局

- 2024-07-31 19:55:02

本发明涉及一种感测放大器,且特别涉及一种非易失性存储器的锁存型感测放大器。

背景技术:

1、众所周知,非易失性存储器内的存储器胞阵列(memory cell array)中包括多个存储器胞(memory cell)。而存储器胞中包括一存储元件(storage device)。举例来说,存储元件可为浮动栅晶体管(floating gate transistor)或者电阻式元件(resistiveelement)。以下简单说明之。

2、一般来说,浮动栅晶体管中的浮动栅极(floating gate)可以存储热载子(hotcarrier),而根据热载子存储量的多寡即可决定存储器胞的存储状态。举例来说,在非易失性存储器的编程周期(program cycle),控制注入浮动栅极的热载子数量,即可改变浮动栅晶体管的临限电压(threshold voltage),并进而改变存储器胞的存储状态。而在读取动作(read action)时,提供一读取电压(read voltage)至浮动栅晶体管,便可以产生存储器胞电流(cell current),或称为读取电流(read current)。而根据存储器胞电流的大小,即可判断存储器胞的存储状态为第一存储状态或者第二存储状态。以n型浮动栅晶体管为例,在读取动作时,如果浮动栅极存储热载子,则存储器胞产生的存储器胞电流非常小(几乎为零),可视为第一存储状态。反之,如果浮动栅极未存储热载子时,则存储器胞产生的存储器胞电流较大,可视为第二存储状态。

3、再者,电阻式元件可以在高低电阻值之间切换。根据电阻值的大小即可决定该电阻式元件的存储状态。举例来说,在非易失性存储器的编程周期(program cycle)时,提供各种偏压用以控制电阻式元件的电阻值。而在读取动作(read action)时,提供一读取电压(read voltage)至电阻式元件,便可以产生存储器胞电流(cell current),或称为读取电流(read current)。而根据存储器胞电流的大小,即可判断存储器胞的存储状态为第一存储状态或者第二存储状态。当然,在非易失性存储器中更需要提供一感测电路(sensingcircuit),用来接收存储器胞产生的存储器胞电流,并判断存储器胞的存储状态。

技术实现思路

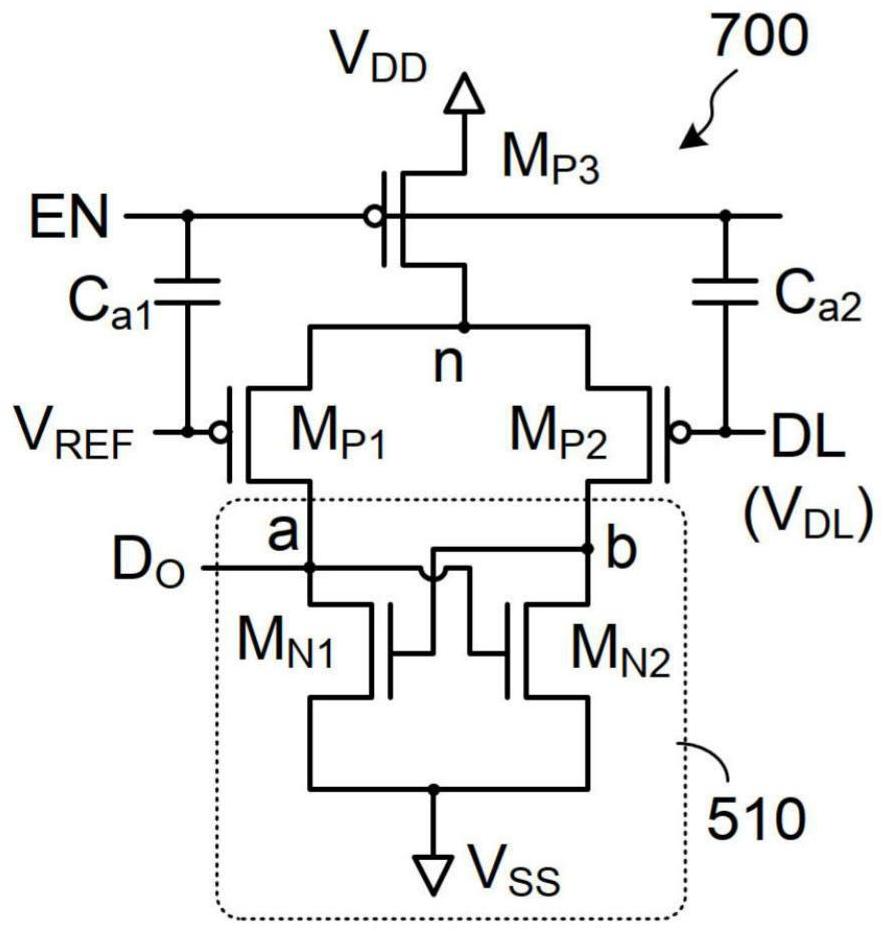

1、本发明涉及一种运用于非易失性存储器的锁存型感测放大器,该非易失性存储器中的一选定存储器胞连接至一数据线,该锁存型感测放大器包括非易失性存储器,包括:一第一晶体管,该第一晶体管的一第一漏/源端连接至一第一节点,该第一晶体管的一第二漏/源端连接至一第二节点,该第一晶体管的一栅极端接收一参考电压,该第一晶体管的该栅极端为该锁存型感测放大器的一第一输入端;一第二晶体管,该第二晶体管的一第一漏/源端连接至该第一节点,该第二晶体管的一第二漏/源端连接至一第三节点,该第二晶体管的一栅极端连接至该数据线,该第二晶体管的该栅极端为该锁存型感测放大器的一第二输入端;一第三晶体管,该第三晶体管的一第一漏/源端接收一第一电源电压,该第三晶体管的一第二漏/源端连接至该第一节点,该第三晶体管的一栅极端接收一致能信号;一锁存元件,连接至该第二节点与该第三节点;一第一电容器,该第一电容器的一第一端连接至该第三晶体管的该栅极端,该第一电容器的一第二端连接至该第一晶体管的该栅极端;以及,一第二电容器,该第二电容器的一第一端连接至该第三晶体管的该栅极端,该第二电容器的一第二端连接至该第二晶体管的该栅极端。

2、为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,并配合附图,作详细说明如下:

技术特征:1.一种运用于非易失性存储器的锁存型感测放大器,该非易失性存储器中的选定存储器胞连接至数据线,该锁存型感测放大器包括:

2.如权利要求1所述的锁存型感测放大器,其中读取周期包括充电相位与感测相位;在该充电相位切换至该感测相位时,该致能信号动作;根据该第一节点上的电压变化,第一耦合电压耦合至该感测放大器的该第一输入端,第二耦合电压耦合至该感测放大器的该第二输入端;根据该致能信号的变化,第三耦合电压耦合至该感测放大器的该第一输入端,第四耦合电压耦合至该感测放大器的该第二输入端;以及,该第一耦合电压与该第三耦合电压可以互相抵销,且该第二耦合电压与该第四耦合电压可以互相抵销。

3.如权利要求1所述的锁存型感测放大器,其中该锁存元件包括:

4.如权利要求3所述的锁存型感测放大器,其中该第一晶体管、该第二晶体管与该第三晶体管为p型晶体管,该第四晶体管与该第五晶体管为n型晶体管,该第一电源电压大于该第二电源电压。

5.如权利要求3所述的锁存型感测放大器,其中该第一晶体管、该第二晶体管与该第三晶体管为n型晶体管,该第四晶体管与该第五晶体管为p型晶体管,该第一电源电压小于该第二电源电压。

6.如权利要求1所述的锁存型感测放大器,其中该锁存元件包括:

7.如权利要求6所述的锁存型感测放大器,其中该第一晶体管、该第二晶体管、该第三晶体管、该第四晶体管与该第五晶体管为p型晶体管,该第六晶体管与该第七晶体管为n型晶体管,该第一电源电压大于该第二电源电压。

8.如权利要求6所述的锁存型感测放大器,其中该第一晶体管、该第二晶体管、该第三晶体管、该第四晶体管与该第五晶体管为n型晶体管,该第六晶体管与该第七晶体管为p型晶体管,该第一电源电压小于该第二电源电压。

9.如权利要求1所述的锁存型感测放大器,还包括辅助电路,连接在该数据线;其中,读取周期包括重置相位;以及,在该重置相位时,该辅助电路控制该数据线维持在初始电压。

10.如权利要求9所述的锁存型感测放大器,其中该辅助电路包括第四晶体管,该第四晶体管的第一漏/源端连接至该数据线,该第四晶体管的第二漏/源端接收接地电压,该第四晶体管的栅极端接收重置信号;在该重置相位时,该重置信号动作,该第四晶体管开启,该数据线被放电至该接地电压,该接地电压等于该初始电压。

11.如权利要求1所述的锁存型感测放大器,还包括辅助电路,连接在该数据线;其中,读取周期包括预充电相位与重置相位;在该预充电相位时,该辅助电路控制该数据线维持在该第一电源电压;以及,在该预充电相位之后的该重置相位时,该辅助电路控制该数据线维持在初始电压。

12.如权利要求11所述的锁存型感测放大器,其中该辅助电路包括第四晶体管与第五晶体管,该第四晶体管的第一漏/源端连接至该数据线,该第四晶体管的第二漏/源端接收接地电压,该第四晶体管的栅极端接收重置信号,该第五晶体管的第一漏/源端连接至该数据线,该第五晶体管的第二漏/源端接收该第一电源电压,该第五晶体管的栅极端接收预充电信号;在该预充电相位时,该预充电信号动作,该第五晶体管开启,该数据线被预充电至该第一电源电压;以及,在该重置相位时,该重置信号动作,该第四晶体管开启,该数据线被放电至该接地电压,该接地电压等于该初始电压。

技术总结一种非易失性存储器的锁存型感测放大器。该锁存型感测放大器包括:三个晶体管、一个锁存元件与二个电容器。第一晶体管的二个漏/源端连接至第一节点与第二节点,第一晶体管的栅极端接收参考电压。第二晶体管的二个漏/源端连接至第一节点与第三节点,第二晶体管的栅极端连接至数据线。第三晶体管的二个漏/源端连接至第一电源电压与第一节点,第三晶体管的栅极端接收致能信号。锁存元件连接至第二节点与第三节点。第一电容器连接至第三晶体管的栅极端与第一晶体管的栅极端之间。第二电容器连接至第三晶体管的栅极端与第二晶体管的栅极端之间。技术研发人员:彭新展受保护的技术使用者:力旺电子股份有限公司技术研发日:技术公布日:2024/5/16本文地址:https://www.jishuxx.com/zhuanli/20240731/184689.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表