包含独立且同时可操作的存储器晶体管块的布置的存储器装置的制作方法

- 国知局

- 2024-07-31 20:12:24

本发明涉及高容量和高带宽存储器系统,并且具体地,涉及一种包含独立且同时可操作的存储器晶体管块的布置的存储器装置,以及一种具有用于高带宽存取的多沟道配置的存储器系统。

背景技术:

1、在例如2016年8月26日提交并于2018年11月6日发布的题为“三维阵列中的电容耦合的非易失性薄膜晶体管nor串(capacitive-coupled non-volatile thin-filmtransistor nor strings in three-dimensional arrays)”的美国专利10,121,553(“'553专利”)中已公开了高密度存储器阵列,例如3维nor存储器串阵列(“3d nor存储器阵列”)。'553专利公开出于所有目的以全文引用的方式并入本文。在'553专利中,存储或存储器晶体管被组织为形成于半导体衬底的平面表面上方的3维nor存储器串阵列。除了提供高存储器密度和容量外,这些3d nor存储器阵列还可以被操作以提供与具有低得多的电路密度和显著更高功率耗散的例如动态随机存取存储器(“dram”)等常规存储器电路相竞争的具有高度期望速度的存储器电路。

2、此外,'553专利中的存储器电路有时被称为“准易失性存储器”或“qv存储器”。与非易失性存储器(nvm)的存储器单元类似,qv存储器的存储器单元各自将数据位作为电荷存储在电荷存储材料(例如,ono)中。由于其电荷存储层的性质,典型的qv存储器单元具有比dram单元长得多的数据保持时间,并且因此需要比dram存储器单元更低的刷新速率。例如,典型的dram系统被设计为每64毫秒刷新一次;然而,具有相当有效存取性能的qv存储器可以每10分钟刷新一次。降低的刷新速率为qv存储器提供了更低的功率需求、降低的散热和更高的存储器可用性的巨大优势,从而提供了更好的主机性能。

技术实现思路

1、基本上如下文例如结合至少一个附图所示和/或所描述,如权利要求中更完整地阐述的,本公开公开了一种包含独立且同时可操作的存储器晶体管块的布置的存储器装置,并公开了具有用于高带宽存取的多沟道配置的存储器系统。

2、在一个实施例中,一种存储器装置包含形成于半导体衬底上的多个存储器电路块,其中每个块包含形成于半导体衬底的平面表面上方的物理隔离的存储晶体管阵列(“存储器阵列”),和在存储器阵列下方形成于半导体衬底之上或之中的模块化控制电路。存储器阵列包含以存储晶体管的多个存储器页组织的三维存储晶体管阵列,其中每个存储晶体管由字线和位线存取。模块化控制电路与存储器阵列通信以对存储晶体管的一个或多个存储器页执行存储器操作。每个块可配置为由相关联模块化控制电路单独寻址和独立操作,以响应于为块标示的存储器存取命令,以存储器阵列中的存储晶体管的存储器页为单位执行存储器操作。两个或更多个随机寻址的存储器电路块可配置为同时执行重叠存储器操作。

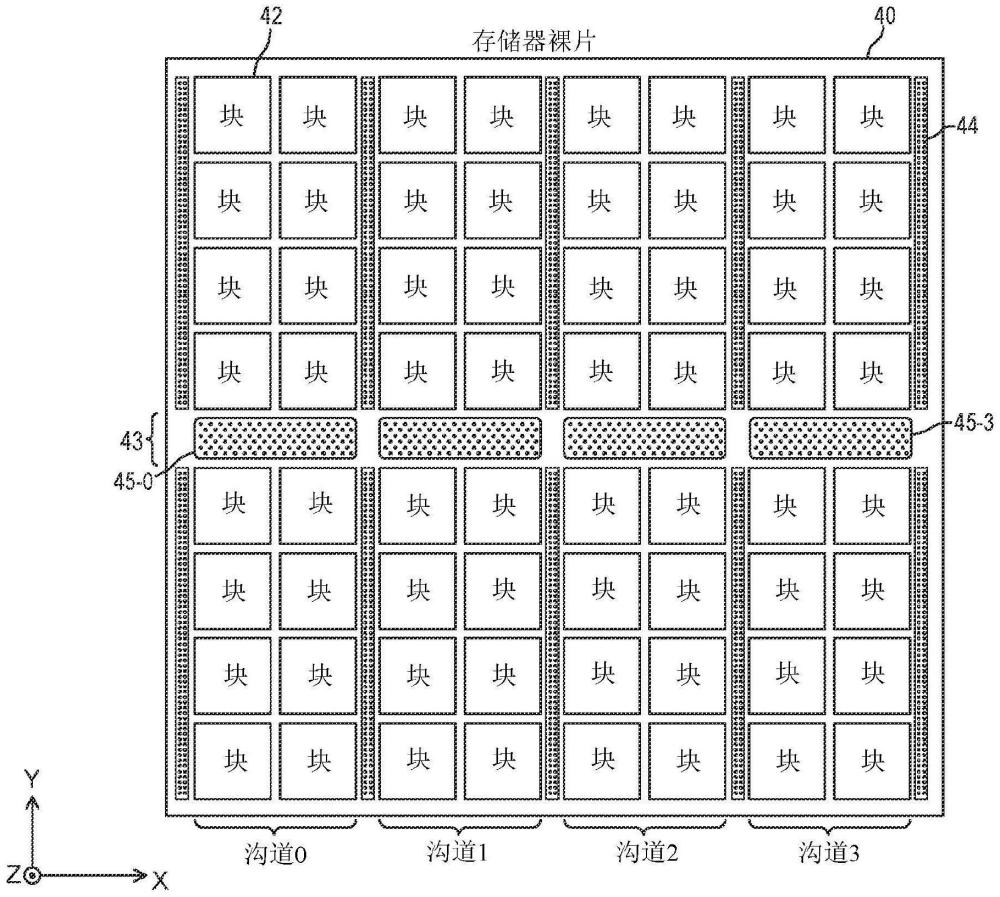

3、在其它实施例中,一种存储器模块包含多个半导体存储器裸片,每个半导体存储器裸片包含被划分为多个分区的三维存储晶体管阵列。跨多个半导体存储器裸片的对应分区形成存储器沟道,并且跨多个半导体存储器裸片的多个分区形成第一数量的独立可存取存储器沟道。所述存储器模块还包含存储器控制器裸片,所述存储器控制器裸片包含用于存取和操作多个半导体存储器裸片的存储器控制电路系统。半导体存储器裸片通过互连结构集连接到存储器控制器裸片。存储器控制电路系统包含第一数量的沟道控制器,其中每个沟道控制器被耦合以操作存储器沟道中的一者,以独立于其它存储器沟道并且与对其它存储器沟道的存储晶体管执行的存储器操作并行地对与相应存储器沟道相关联的存储晶体管执行存储器操作。

4、在一些实施例中,一种存储器模块包含多个半导体存储器裸片,每个半导体存储器裸片包含多个存储器阵列,每个存储器阵列包含三维存储晶体管阵列。半导体存储器裸片包含提供存储器模块的标示存储器容量的第一数量的半导体存储器裸片和提供冗余存储器容量的至少一个备用半导体存储器裸片。所述存储器模块还包含存储器控制器裸片,所述存储器控制器裸片包含用于存取和操作半导体存储器裸片以执行存储器操作的存储器控制电路系统。半导体存储器裸片通过互连结构集连接到存储器控制器裸片。存储器控制器从主机处理器接收对存储器操作的传入请求,所述传入请求寻址到跨越第一数量的半导体存储器裸片并且不包含至少一个备用半导体存储器裸片的第一存储器地址空间。

5、从以下描述和附图将更充分地了解本发明的这些和其它优点、方面和新颖特征,以及其所示实施例的细节。

技术特征:1.一种存储器装置,其包括:

2.根据权利要求1所述的存储器装置,其中所述多个存储器电路块形成于半导体衬底上,其中每个块包含形成于所述半导体衬底的平面表面上方的所述物理隔离的存储晶体管阵列,和在所述存储器阵列下方形成于所述半导体衬底之上或之中的所述模块化控制电路。

3.根据权利要求1所述的存储器装置,其中所述多个存储器电路块包括形成于第一半导体裸片上的多个物理隔离的存储晶体管阵列以及形成于第二半导体裸片上的用于所述存储晶体管阵列的对应模块化控制电路,所述第一半导体裸片电连接且机械连接到所述第二半导体裸片,使得每个存储器阵列和相关联模块化控制电路形成所述存储器装置中的块。

4.根据权利要求1所述的存储器装置,其中所述多个存储器电路块包括多个物理隔离的存储晶体管阵列,且所述模块化控制电路的电路系统的至少一部分形成于第一半导体裸片上且用于所述存储晶体管阵列的其余对应模块化控制电路形成于第二半导体裸片上,所述第一半导体裸片电连接且机械连接到所述第二半导体裸片,使得具有所述电路系统的一部分的每个存储器阵列以及相关联模块化控制电路形成所述存储器装置中的块。

5.根据权利要求1所述的存储器装置,其中每个存储器存取命令是基于存储器数据的存取单元,所述存取单元为存储器页,且块的模块化控制电路响应于为所述块标示的每个存储器存取命令而对存储晶体管的存储器页执行存储器操作。

6.根据权利要求5所述的存储器装置,其中存储器数据的存取单元包括512位,且存储晶体管的存储器页包括512个存储晶体管。

7.根据权利要求1所述的存储器装置,其中每个块中的每个物理隔离的存储器阵列包括以所述三维阵列布置的存储晶体管和将所述存储晶体管连接到所述模块化控制电路的一个或多个阶梯结构。

8.根据权利要求7所述的存储器装置,其中每个块中的每个物理隔离的存储器阵列包括随机可存取的存储晶体管的三维nor存储器串阵列,所述一个或多个阶梯结构将所述nor存储器串的位线连接到所述模块化控制电路。

9.根据权利要求8所述的存储器装置,其中在每个存储器阵列中,每个字线激活第一数量的存储器页,且所述模块化控制电路响应于存储器存取命令而选择与存储晶体管的第一存储器页相关联的位线以执行存储器操作。

10.根据权利要求1所述的存储器装置,其中所述多个存储器电路块中的每一个包括准易失性存储器电路。

11.根据权利要求10所述的存储器装置,其中以10分钟或更长的间隔刷新每个存储器阵列中的所述准易失性存储器电路的所述存储晶体管。

12.根据权利要求10所述的存储器装置,其中每个存储器阵列中的所述存储晶体管各自包括可通过直接隧穿技术编程的存储材料。

13.根据权利要求10所述的存储器装置,其中每个存储器阵列中的所述存储晶体管各自包括铁电存储晶体管。

14.根据权利要求8所述的存储器装置,其中所述三维nor存储器串阵列在第一方向上平行布置且在第二方向上堆叠成多层,每个nor存储器串包含共享公共源极线和公共漏极线的多个存储晶体管,其中每个nor存储器串层沿着第三方向延伸,所述nor存储器串阵列还包括:

15.根据权利要求1所述的存储器装置,其中每个模块化控制电路在所述第一和第三方向上具有与其相关联存储器阵列相同的尺寸。

16.根据权利要求1所述的存储器装置,其中所述多个块的所述模块化控制电路与形成于单独的半导体衬底上的存储器控制器集成电路交互,块中的每个模块化控制电路接收被标示给所述块的存储器存取命令以及与所述命令相关联的存储器地址,所述存储器地址标示所述存储器阵列中的一个存储器页,用于执行由所述存储器存取命令指定的存储器操作。

17.根据权利要求16所述的存储器装置,其中每个存储器存取命令指定包括读取、写入和刷新操作的存储器操作,所述存储器存取命令向写入数据提供写入操作命令。

18.根据权利要求16所述的存储器装置,其中每个块中的每个物理隔离的存储器阵列包括随机可存取的存储晶体管的三维nor存储器串阵列,所述一个或多个阶梯结构将所述nor存储器串的位线连接到所述模块化控制电路,并且所述多个块中的每个模块化控制电路是用于每个块的复制完整控制电路。

19.根据权利要求18所述的存储器装置,其中每个模块化控制电路包括:

20.根据权利要求19所述的存储器装置,其中响应于与存储器存取命令相关联的所述存储器地址,所述标示块的所述模块化控制电路通过所述字线驱动电路选择所述存储器阵列中的所述字线中的一者以激活所述第一数量的存储器页,并且所述模块化控制电路还从激活的所述第一数量的存储器页中选择一个存储器页的位线以执行由所述相关联存储器存取命令指示的所述存储器操作。

21.根据权利要求19所述的存储器装置,其中块中的每个模块化控制电路还包括块逻辑电路,所述块逻辑电路包括处理器单元,所述处理器单元用于对存储器存取命令进行解码且在所述块的所述存储器阵列处执行存储器操作序列以执行由所述存储器存取命令指定的所述存储器操作,其中所述块逻辑电路生成控制信号以执行每个存储器存取命令的所述存储器操作序列且控制用于执行所述存储器操作序列的定时序列。

22.根据权利要求19所述的存储器装置,其中块中的每个模块化控制电路还包括感测放大器电路,所述感测放大器电路到所述位线驱动电路的所选位线,以响应于所述存储器存取命令感测或驱动所述所选位线,所述感测放大器电路包含第二数量的感测放大器,所述第二数量等于与所述存储器存取命令相关联的存储器数据的存取单元中的数据位的数量,存取单元等于存储器页。

23.根据权利要求22所述的存储器装置,其中块中的每个模块化控制电路还包括多个数据锁存器,用于响应于读取操作而存储从所述存储器阵列检索的读取数据,以及用于响应于写入操作而存储将要存储在所述存储器阵列中的写入数据。

24.一种存储器模块,其包括:

25.根据权利要求24所述的存储器模块,其中所述多个半导体存储器裸片被形成为一个堆叠在另一个之上,并且所述半导体存储器裸片的所述堆叠被形成为堆叠在所述存储器控制器裸片上,且所述互连结构集将多个堆叠的半导体存储器裸片电连接到所述存储器控制器裸片。

26.根据权利要求25所述的存储器模块,其中所述多个堆叠的半导体存储器裸片通过第二互连结构集连接在一起。

27.根据权利要求26所述的存储器模块,其中所述互连结构集包括硅通孔(tsv)、混合键合、铜螺柱或中介层中的一者,并且所述第二互连结构集包括硅通孔(tsv)。

28.根据权利要求27所述的存储器模块,其中所述互连结构集包括第一数量的硅通孔(tsv)集,每个tsv集将跨所述多个半导体存储器裸片的相应分区连接到所述存储器控制器裸片上的相应沟道控制器。

29.根据权利要求24所述的存储器模块,其中每个半导体存储器裸片包括形成于半导体衬底上的准易失性存储晶体管的存储器阵列,所述存储器阵列被组织为形成于所述半导体衬底上方的二维块阵列,每个块中的存储晶体管以三维nor存储器串阵列布置。

30.根据权利要求29所述的存储器模块,其中所述三维存储晶体管阵列的每个分区包括所述存储器阵列的所述块的一部分。

31.根据权利要求24所述的存储器模块,其中每个沟道控制器通过存储器接口与相应存储器沟道通信,所述存储器接口包括至少一个命令总线和至少一个数据总线。

32.根据权利要求24所述的存储器模块,其中每个沟道控制器向所述相应存储器沟道传输命令以执行存储器操作,所述命令至少包括读取命令和写入命令。

33.根据权利要求24所述的存储器模块,其中所述存储器控制器还包括地址转换电路,所述地址转换电路被配置成处理由所述存储器模块接收的传入请求,每个传入请求包括逻辑存储器地址,其中所述存储器控制器的所述地址转换电路将所述逻辑存储器地址转换为识别所述半导体存储器裸片中的所述存储晶体管的物理存储器地址,所述物理存储器地址包含用于从所述多个存储器沟道中选择相应存储器沟道的一个或多个地址位。

34.根据权利要求33所述的存储器模块,其中用于选择存储器沟道的所述物理存储器地址的所述一个或多个地址位包括所述物理存储器地址的较低阶地址位。

35.根据权利要求33所述的存储器模块,其中所述物理存储器地址包含用于从所述多个存储器沟道中选择存储器沟道的地址位、用于从所述多个半导体存储器裸片中选择存储器裸片的地址位,用于从每个分区中的所述块中选择存储器组的地址位、用于在所述存储器组内选择存储晶体管行的地址位,以及用于从所述行中选择存储晶体管子集以形成存储器页的地址位。

36.根据权利要求24所述的存储器模块,其中所述多个半导体存储器裸片包括k+1个半导体存储器裸片,其中所述半导体存储器裸片中的k个半导体存储器裸片提供所述存储器模块的标示存储器容量且一个半导体存储器裸片提供冗余存储器容量,其中对所述存储器模块的传入请求被寻址到跨越所述k个半导体存储器裸片且不包含提供所述冗余存储器容量的所述半导体裸片的存储器地址空间。

37.根据权利要求36所述的存储器模块,其中所述存储器控制器还包括地址转换电路,所述地址转换电路被配置成处理由所述存储器模块接收的传入请求,每个传入请求包括被定向到所述k个半导体存储器裸片的所述存储器地址空间的逻辑存储器地址,其中所述存储器控制器的所述地址转换电路将所述逻辑存储器地址转换为识别所述k+1个半导体存储器裸片中的对应存储晶体管的物理存储器地址。

38.根据权利要求37所述的存储器模块,其中所述地址转换电路将被定向到所述k个半导体存储器裸片的所述存储器地址空间的第一逻辑存储器地址转换为跨越所述k+1个半导体存储器裸片的所述存储器地址空间中的所述物理存储器地址。

39.一种存储器模块,其包括:

40.根据权利要求39所述的存储器模块,其中所述存储器控制器被配置成响应于检测到所述第一存储器阵列中的预定条件而发起用所述至少一个备用半导体存储器裸片中的冗余存储器阵列替换所述第一数量的半导体存储器裸片中的第一存储器阵列。

41.根据权利要求40所述的存储器模块,其中所述存储器控制器对跨越所述第一数量的半导体存储器裸片和所述至少一个备用半导体存储器裸片两者的第二存储器地址空间中的所述存储器阵列执行存储器操作。

42.根据权利要求39所述的存储器模块,其中所述第一数量的半导体存储器裸片包含k个半导体存储器裸片和所述备用半导体存储器裸片,一起形成一组k+1个半导体存储器裸片,使得所述第一数量的半导体存储器裸片定义所述第一存储器地址空间并且所述一组k+1个半导体存储器裸片定义第二存储器地址空间。

43.根据权利要求42所述的存储器模块,其中所述存储器控制器还包括地址转换电路,所述地址转换电路被配置成处理由所述存储器模块接收的传入请求,每个传入请求包括被定向到所述第一存储器地址空间的逻辑存储器地址,其中所述存储器控制器的所述地址转换电路将所述逻辑存储器地址转换为识别所述k+1个半导体存储器裸片中的对应存储晶体管的物理存储器地址。

44.根据权利要求43所述的存储器模块,其中所述地址转换电路将被定向到所述第一存储器地址空间的第一逻辑存储器地址转换为所述第二存储器地址空间中的物理存储器地址。

45.根据权利要求39所述的存储器模块,其中所述多个半导体存储器裸片被形成为一个堆叠在另一个之上,并且通过第二互连结构集连接在一起。

46.根据权利要求45所述的存储器模块,其中所述互连结构集包括硅通孔(tsv)、混合键合、铜螺柱或中介层中的一者,并且所述第二互连结构集包括硅通孔(tsv)。

47.根据权利要求42所述的存储器模块,其中所述存储器控制器在所述第一存储器地址空间上与所述主机处理器通信,并且在所述第二存储器地址空间上管理存储器操作。

技术总结在一些实施例中,一种存储器装置实施基于块的架构,所述基于块的架构包含:独立且同时可操作的存储器晶体管阵列或块的布置,其中每个块包含以三维阵列布置的存储器晶体管;以及操作所述块中的所述存储器晶体管的局部模块化控制电路。所述存储器装置的所述基于块的架构能够实现对多个块的同时存储器存取,这使得能够跨多个块执行独立且同时的存储器操作。对所述存储器装置的所述基于块的同时存取具有通过确保存储晶体管的高可用性来增加存储器带宽并降低所述存储器装置的尾部延迟的益处。在其它实施例中,一种存储器模块包含耦合到存储器控制器的多个半导体存储器裸片,其中所述半导体存储器裸片被划分为独立可存取的存储器沟道,其中每个存储器沟道跨所述多个半导体存储器裸片形成。技术研发人员:吉原正浩,吕子宜,劳尔·阿德里安·塞内亚,谢伊·福克斯,萨吉·戈登伯格,叶利·哈拉里受保护的技术使用者:日升存储公司技术研发日:技术公布日:2024/7/11本文地址:https://www.jishuxx.com/zhuanli/20240731/185434.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。