一种正交时钟生成电路及方法

- 国知局

- 2024-08-02 15:25:42

本申请涉及集成电路设计,尤其涉及的是一种正交时钟生成电路及方法。

背景技术:

1、随着数据中心、云计算、大数据、5g通信以及自动驾驶等应用领域的不断发展和普及,数据传输对总线带宽的要求越来越高,高速serdes接口芯片的应用也越来越广泛。高速serdes接口中主要包含了发射、接收和多相时钟生成电路。为了降低时钟分布的载波频率和功耗,高速serdes发射电路一般都会采用四分之一速率的架构,接收电路中的超高速模数转换器通常会采用时间交错技术,都要求时钟生成电路能够提供高精度低抖动的多相时钟。此外,高速serdes需要向下兼容中低传输速率,也要求多相时钟电路实现宽频带调谐。因此,低功耗、低抖动、高相位精度以及宽频带的多相时钟生成电路是实现高速serdes接口的关键。

2、近年来,已有多种时钟生成技术被提出。研究者们提出了一种采用分频器来生成注入信号的宽锁定范围注入锁定振荡器。但功耗较高,且输出频率范围较窄。而其它的基于注入锁定环形振荡器生成多相时钟的方法存在抖动性能和相位精度的折中。

3、因此,现有技术还有待于改进和发展。

技术实现思路

1、鉴于上述现有技术的不足,本申请的目的在于提供一种正交时钟生成电路及方法,以解决现有技术中时钟生成技术相位精度低且功耗高的问题。

2、本申请的技术方案如下:

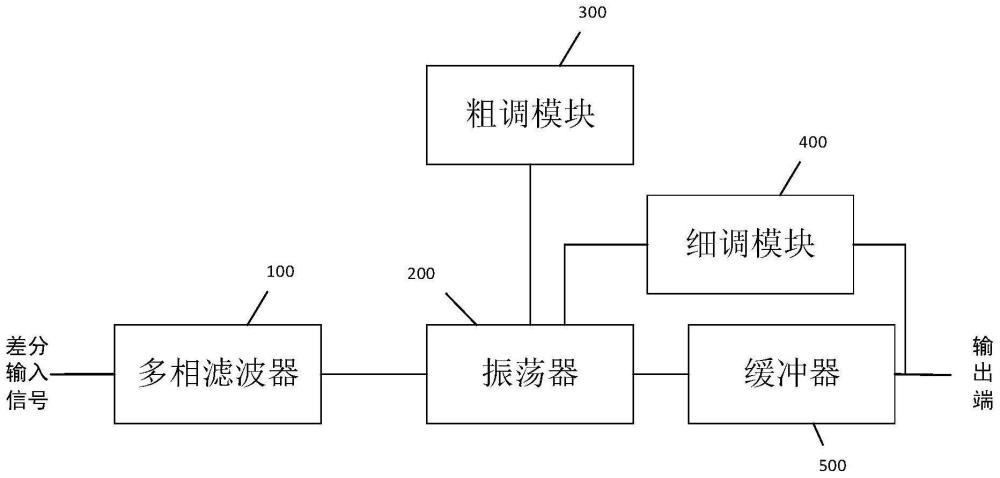

3、一种正交时钟生成电路,包括:输出端、多相滤波器、振荡器、粗调模块以及细调模块;

4、所述多相滤波器接入差分输入信号,用于将差分输入信号生成四相注入信号;

5、所述振荡器与所述多相滤波器连接,用于根据四相注入信号产生振荡信号;

6、所述粗调模块与所述振荡器连接,用于在振荡信号与所述差分输入信号频率不匹配时,调节所述振荡器的输入电流;

7、所述细调模块分别与输出端以及所述振荡器连接,用于检测所述输出端的正交相位差,并根据正交相位差调节所述振荡器的输入电流。

8、本申请的进一步设置,所述多相滤波器为无源多相滤波器。

9、本申请的进一步设置,所述振荡器为注入锁定环形振荡器。

10、本申请的进一步设置,还包括缓冲器;

11、所述缓冲器分别与所述振荡器以及输出端连接,用于对所述振荡信号进行缓冲。

12、本申请的进一步设置,所述多相滤波器包括若干个第一电阻电容单元以及若干个第二电阻电容单元,所述第一电阻电容单元串联且形成闭环;所述第二电阻电容单元串联且形成闭环,所述第二电阻电容单元接入差分信号,并与所述第一电阻电容单元间隔串联。

13、本申请的进一步设置,所述振荡器包括延迟单元以及与所述延迟单元对应连接的场效应管;

14、所述场效应管的栅极接入四相注入信号,所述场效应管的漏极与所述延迟单元的输入端连接,所述场效应管的源极接地;

15、所述延迟单元的电源端与所述粗调模块连接,用于根据所述粗调模块的输出电流进行延迟振荡。

16、本申请的进一步设置,所述粗调模块包括电流源阵列以及频率控制开关;

17、所述电流源阵列与所述频率控制开关连接,用于输出多路电流;

18、所述频率控制开关与所述振荡器连接,用于控制多路电流输出,以调整所述振荡器的偏置电流。

19、本申请的进一步设置,所述细调模块包括相位误差检测器、放大器以及电流调节管;

20、所述相位误差检测器与所述输出端连接,用于将输出信号混频后生成正比于相位误差的电压信号;

21、所述放大器与所述电流调节管连接,用于将电压信号进行放大,并输出放大信号至所述电流调节管;

22、所述电流调节管与所述振荡器连接,用于根据方法信号调整所述振荡器的偏置电流。

23、本申请的进一步设置,所述相位误差检测器设有两个。

24、本申请基于同样的发明构思,还提供了一种用于生成正交时钟信号的方法,所述方法包括:

25、通过多相滤波器将差分输入信号生成四相注入信号;

26、通过振荡器根据四相输入信号产生振荡信号;

27、通过粗调模块在振荡信号与所述差分输入信号频率不匹配时,调节所述振荡器的输入电流;

28、通过细调模块检测输出端的正交相位差,并根据正交相位差调节所述振荡器的输入电流。

29、本申请所提供的一种正交时钟生成电路及方法,所述正交时钟生成电路包括:输出端、多相滤波器、振荡器、粗调模块以及细调模块;所述多相滤波器接入差分输入信号,用于将差分输入信号生成四相注入信号;所述振荡器与所述多相滤波器连接,用于根据四相注入信号产生振荡信号;所述粗调模块与所述振荡器连接,用于在振荡信号与所述差分输入信号频率不匹配时,调节所述振荡器的输入电流;所述细调模块分别与输出端以及所述振荡器连接,用于检测所述输出端的正交相位差,并根据正交相位差调节所述振荡器的输入电流。本申请先通过多相滤波器采用差分信号生成四相注入信号,降低功耗,再将四相注入信号注入至振荡器中,生成高精度和低抖动的正交时钟信号。最后使用粗调模块粗略调整振荡频率,同时使用相位误差环路构成的细调模块检测输出信号相位误差,经过反馈到振荡器,调整其自谐振频率,从而生成精确相位。

技术特征:1.一种正交时钟生成电路,其特征在于,包括:输出端、多相滤波器、振荡器、粗调模块以及细调模块;

2.根据权利要求1所述的正交时钟生成电路,其特征在于,所述多相滤波器为无源多相滤波器。

3.根据权利要求1所述的正交时钟生成电路,其特征在于,所述振荡器为注入锁定环形振荡器。

4.根据权利要求1所述的正交时钟生成电路,其特征在于,还包括缓冲器;

5.根据权利要求1所述的正交时钟生成电路,其特征在于,所述多相滤波器包括若干个第一电阻电容单元以及若干个第二电阻电容单元,所述第一电阻电容单元串联且形成闭环;所述第二电阻电容单元串联且形成闭环,所述第二电阻电容单元接入差分信号,并与所述第一电阻电容单元间隔串联。

6.根据权利要求1所述的正交时钟生成电路,其特征在于,所述振荡器包括延迟单元以及与所述延迟单元对应连接的场效应管;

7.根据权利要求1所述的正交时钟生成电路,其特征在于,所述粗调模块包括电流源阵列以及频率控制开关;

8.根据权利要求1所述的正交时钟生成电路,其特征在于,所述细调模块包括相位误差检测器、放大器以及电流调节管;

9.根据权利要求8所述的正交时钟生成电路,其特征在于,所述相位误差检测器设有两个。

10.一种用于生成正交时钟信号的方法,其特征在于,所述方法包括:

技术总结本申请公开了一种正交时钟生成电路及方法,所述正交时钟生成电路包括:输出端、多相滤波器、振荡器、粗调模块以及细调模块。本申请先通过多相滤波器采用差分信号生成四相注入信号,降低功耗,再将四相注入信号注入至振荡器中,生成高精度和低抖动的正交时钟信号。最后使用粗调模块调整振荡频率,同时使用相位误差环路构成的细调模块检测输出信号相位误差,经过反馈到振荡器,调整其自谐振频率,从而生成精确相位。技术研发人员:刘小龙,刘炎炜,骆其轩受保护的技术使用者:南方科技大学技术研发日:技术公布日:2024/7/18本文地址:https://www.jishuxx.com/zhuanli/20240801/246043.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表