集成电路结构及其制造方法与流程

- 国知局

- 2024-08-02 15:28:34

本揭露的实施方式是有关于一种集成电路结构及其制造方法。

背景技术:

1、半导体集成电路(ic)产业已历经快速成长。集成电路材料与设计中的技术进步已经产生数个集成电路世代,其中每个世代具有比前一世代更小且更复杂的电路。在集成电路发展的进程中,随着几何尺寸[亦即,利用一工艺可形成的最小构件(或线)]的减少,功能密度(亦即,每晶片面积的互连元件的数量)大体上已获得增加。这样的尺寸缩减过程通常通过提高生产效率与降低相关成本来提供好处。这样的尺寸缩减也增加了集成电路加工与制造的复杂性,要实现这些进展,集成电路加工与制造需要类似的发展。

2、举例而言,电容器作为一种被动元件,为集成电路(ic)中的重要元件,且广泛地应用于各种目的,例如在随机存取记忆体(ram)非挥发性记忆体元件、去耦电容器、或电阻电容(rc)电路中。当集成电路朝特征尺寸更小的先进技术节点发展时,由于电容器的特性,电容器几乎是不可缩减而无法缩小到小尺寸。电容器占了相当的电路面积损失。此外,现有的制造电容器的方法将缺陷引入电容器中,而造成不受欢迎的问题,例如材料整合与通过电容器的漏电流。因此,亟需提供一种没有上述缺点的与其他电路元件整合的电容器结构及其制造方法。

技术实现思路

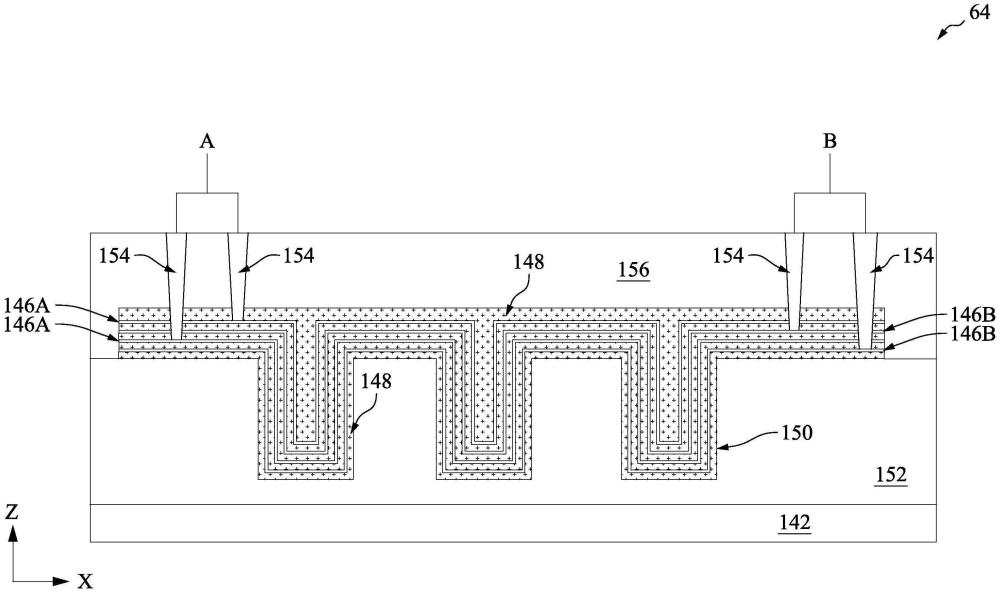

1、在一态样中,本揭露提供一种集成电路结构,包含第一基板具有集成电路形成于其上;第二基板接合至第一基板;以及深沟渠电容器形成于第二基板上且电性连接集成电路。深沟渠电容器包含数个导电层与数个介电层的堆叠设于数个深沟渠中,以及数个导电插塞分别落在导电层上。每个导电插塞包含第一金属层、第二金属层设于第一金属层上、以及第三金属层设于第二金属层上。第一金属层、第二金属层、与第三金属层的成分不同。

2、在另一态样中,本揭露提供一种集成电路结构。此集成电路结构包含数个深沟渠电容器形成在第一基板上且配置成一阵列。这些深沟渠电容器包含第一深沟渠电容器设于沿第一方向纵向定向的数个第一深沟渠中;以及第二深沟渠电容器与阵列中的第一深沟渠电容器相邻,且设于沿第二方向纵向定向的数个第二深沟渠中,第二方向与第一方向正交。每个深沟渠电容器包含数个导电层与数个介电层的堆叠设于数个深沟渠中,以及数个导电插塞分别落在导电层上。每个导电插塞包含第一金属层、第二金属层设于第一金属层上、以及第三金属层设于第二金属层上。第一金属层、第二金属层、与第三金属层的成分不同。

3、在又一态样中,本揭露提供一种集成电路结构的制造方法。此方法包含形成数个第一沟渠于第一基板上;形成堆叠于第一沟渠中,此堆叠包含数个导电层与数个介电层,其中这些导电层与介电层在此堆叠中互相交错;形成介电特征于此堆叠与第一沟渠的上方;形成数个开口于介电特征中,借以分别暴露出这些开口中的导电层;沉积第一金属层于这些开口中;沉积第二金属层于第一金属层上,第二金属层包含铜锰合金;以及沉积第三金属层于第二金属层上,第三金属层包含钨、铜、与铜铝合金中的一者。

技术特征:1.一种集成电路结构,其特征在于,该集成电路结构包含:

2.如权利要求1所述的集成电路结构,其特征在于,

3.如权利要求1所述的集成电路结构,其特征在于,所述多个导电插塞落在各自的所述导电层上具有不同的高度。

4.如权利要求1所述的集成电路结构,其特征在于,该集成电路结构还包含多个深沟渠电容器,形成在该第二基板上,且配置成一阵列,其中

5.如权利要求4所述的集成电路结构,其特征在于,所述多个深沟渠电容器的该第一者包含多个第一导电插塞,所述多个第一导电插塞设于所述多个第一深沟渠的相邻二者之间且沿该第一方向对齐。

6.如权利要求5所述的集成电路结构,其特征在于,所述多个深沟渠电容器的该第二者包含多个第二导电插塞,所述多个第二导电插塞设于所述多个第二深沟渠的相邻二者之间且沿该第二方向对齐。

7.一种集成电路结构,其特征在于,该集成电路结构包含多个深沟渠电容器形成在一第一基板上且配置成一阵列,其中所述多个深沟渠电容器包含:

8.如权利要求7所述的集成电路结构,其特征在于,

9.如权利要求7所述的集成电路结构,其特征在于,该集成电路结构还包含一互连结构设于该第一深沟渠电容器与该第二深沟渠电容器上,其中该互连结构包含一第一金属层,该第一金属层具有多个第一金属线连接至所述多个导电插塞,其中所述多个第一金属线包含一第一子集的所述多个第一金属线沿该第一方向纵向定向,以及一第二子集的所述多个第一金属线沿该第二方向纵向定向。

10.一种集成电路结构的制造方法,其特征在于,该方法包含:

技术总结本揭露提供一种集成电路结构及其制造方法,集成电路(IC)结构包含第一基板具有集成电路形成于其上;第二基板接合至第一基板;以及深沟渠电容器形成于第二基板上且电性连接集成电路。深沟渠电容器包含数个导电层与数个介电层的堆叠设于数个深沟渠中,以及数个导电插塞分别落在导电层上。每个导电插塞包含第一金属层、第二金属层设于第一金属层上、以及第三金属层设于第二金属层上。第一金属层、第二金属层、与第三金属层的成分不同。技术研发人员:郭富强,龚柏诚,陈信良受保护的技术使用者:台湾积体电路制造股份有限公司技术研发日:技术公布日:2024/7/23本文地址:https://www.jishuxx.com/zhuanli/20240801/246268.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。