晶粒封装结构的制作方法

- 国知局

- 2024-08-05 11:53:21

本发明关于一种小尺寸产品封装的,尤指一种晶粒封装结构。

背景技术:

1、请同时参照图1及图2,其中图1为现有晶粒封装结构的示意图之一,图2为现有晶粒封装结构的示意图之二。对于小尺寸封装产品,如图1及图2所示的晶粒封装结构9的晶粒91,目前业界使用的封装方式是使晶粒91的p结911经由打线(wire bond)工序而以金属线92(例如铜线、金线、铝线、铁线等)与框架93(例如导线架(lead frame))做电性连结,并使位于p结911的相对侧的n结912经由导电胶94(例如银胶)与框架93做电性连结。

2、于上述的晶粒封装结构9中,由于金属线92的线径与电流承受能力有关,通常电流规格小。

3、目前已发展出另外一种封装技术,即所谓的晶片尺寸封装(chip scale package,csp),于此封装技术中,晶粒的p结与n结需位在同一侧,故并不适用于具有位于相对侧的p结与n结的晶粒。

技术实现思路

1、为了解决上述传统晶粒封装结构存在的各种问题,例如金属线承受能力不足、不能适用于具有位于相对侧的p结与n结的晶粒等,本发明提出一种晶粒封装结构,可适用于原有具有位于相对侧的p结与n结的晶粒,利用原有晶粒位于相对侧的p结与n结,将p结外延出一绝缘层与一外延金属层,通过外延金属层直接与例如印刷电路板(pcb)做结合以进行p结输出,而n结则通过导电胶接合层与框架做结合以进行n结输出。

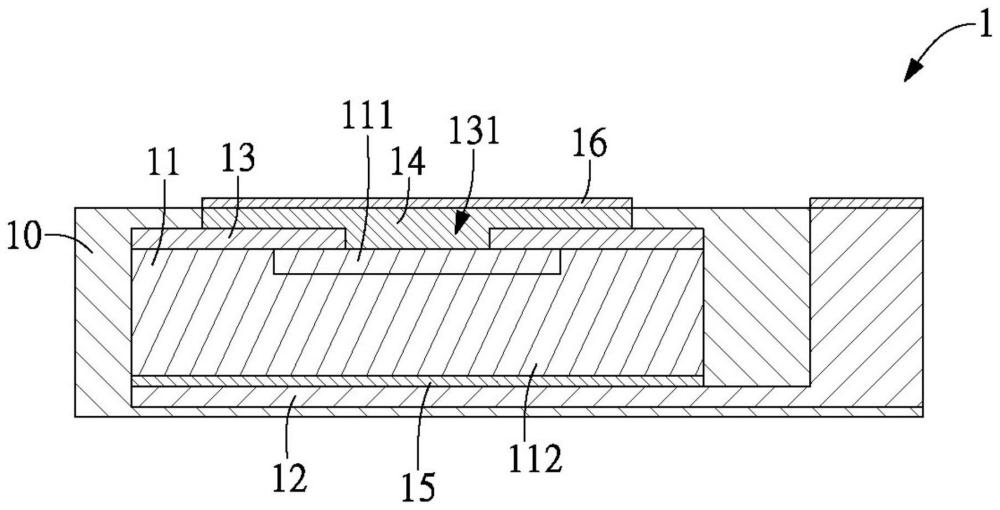

2、本发明所提出的晶粒封装结构包含一晶粒、一框架、一绝缘层、一外延金属层以及一导电接合层。其中,该晶粒包含位于相对侧的一p结及一n结;该绝缘层层叠于该p结上并形成有一开口,该开口连通于该p结;该外延金属层层叠于该绝缘层上并经由该开口层叠于该p结上;该导电接合层层叠于该n结与该框架之间。

3、如上所述,通过将该晶粒的该p结外延出该绝缘层与该外延金属层,故于该晶粒封装结构中并不需要经过打线工序(即不会有金属线),因此可增强电流的规格,且因无打线工序(无金属线),亦可降低成品的高度。

4、非限制性地于一实施例中,上述的该绝缘层为一聚酰亚胺(polyimide,pi)层。

5、非限制性地于一实施例中,上述的该绝缘层为一苯环丁烯(benzocyclobutene,bcb)层。

6、非限制性地于一实施例中,上述的该外延金属层为一铜(cu)层。

7、非限制性地于一实施例中,上述的该导电接合层为一导电胶。

8、非限制性地于一实施例中,上述的该导电接合层为一银胶(silver glue)。

9、非限制性地于一实施例中,上述的该晶粒封装结构进一步包含一镀锡层(snplating),层叠于该外延金属层上。

10、非限制性地于一实施例中,上述的该开口的位置对应于该p结的中央位置。

技术特征:1.一种晶粒封装结构,包含:

2.根据权利要求1所述的晶粒封装结构,其中该绝缘层为一聚酰亚胺层。

3.根据权利要求1所述的晶粒封装结构,其中该绝缘层为一苯环丁烯层。

4.根据权利要求1所述的晶粒封装结构,其中该外延金属层为一铜层。

5.根据权利要求1所述的晶粒封装结构,其中该导电接合层为一导电胶。

6.根据权利要求1所述的晶粒封装结构,其中该导电接合层为一银胶。

7.根据权利要求1所述的晶粒封装结构,其中进一步包含一镀锡层,层叠于该外延金属层上。

8.根据权利要求1所述的晶粒封装结构,其中该开口的位置对应于该p结的中央位置。

技术总结为了解决传统晶粒封装结构的金属线承受能力不足、不能适用于具有位于相对侧的P结与N结的晶粒等问题,本发明提出一种晶粒封装结构,包含一晶粒、一框架、一绝缘层、一外延金属层以及一导电接合层。其中,晶粒包含位于相对侧的一P结及一N结;绝缘层层叠于P结上并形成有一开口,开口连通于P结;外延金属层层叠于绝缘层上并经由开口层叠于P结上;导电接合层层叠于N结与框架之间。通过将P结外延出绝缘层与外延金属层,不需要经过打线工序而不会有金属线,因此可增强电流的规格,亦可降低成品的高度。技术研发人员:廖皇顺受保护的技术使用者:力勤股份有限公司技术研发日:技术公布日:2024/8/1本文地址:https://www.jishuxx.com/zhuanli/20240802/259916.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表