一种系统级芯片的异常处理方法、装置、设备及介质与流程

- 国知局

- 2024-08-05 12:03:15

本发明涉及集成芯片,特别是涉及一种系统级芯片的异常处理方法、装置、设备及介质。

背景技术:

1、随着系统级芯片(system on chips,soc)的高速发展,在soc芯片运行过程中,无法避免地出现某些异常的任务处理过程,且一般将出现的异常归纳在异常源中,此时,异常源可分为同步异常源和异步异常源;

2、现有的对异常进行处理的方法中不对同步异常源和异步异常源进行区分,只要识别到异常源就直接将系统级芯片当前正在进行的进程停止,直到异常处理完毕才再次恢复正常进程,由此导致soc芯片的异常处理的效率低下。

3、鉴于上述存在的问题,寻求如何提高soc芯片的异常处理效率是本领域技术人员竭力解决的问题。

技术实现思路

1、本发明的目的是提供一种系统级芯片的异常处理方法、装置、设备及介质,用于解决soc芯片针对异常处理的效率低下,且异常处理的效果不理想的问题。

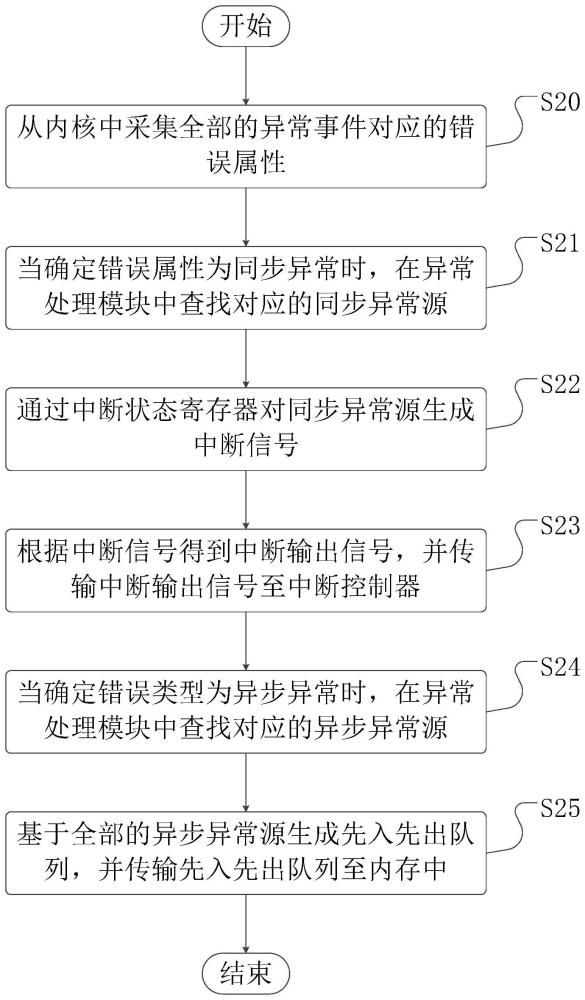

2、为解决上述技术问题,本发明提供一种系统级芯片的异常处理方法,应用于至少设置有内核、中央处理器、异常处理模块、中断控制器、内存的系统级芯片,所述方法包括:

3、从所述内核中采集全部的异常事件对应的错误属性,所述错误属性为同步异常和异步异常;

4、当确定所述错误属性为所述同步异常时,在所述异常处理模块中查找对应的同步异常源;

5、通过中断状态寄存器对所述同步异常源生成中断信号;

6、根据所述中断信号得到中断输出信号,并传输所述中断输出信号至所述中断控制器,以便于根据所述中断输出信号进行同步异常处理;

7、当确定所述错误类型为所述异步异常时,在所述异常处理模块中查找对应的异步异常源;

8、基于全部的所述异步异常源生成先入先出队列,并传输所述先入先出队列至所述内存中,以便于根据所述先入先出队列进行异步异常处理。

9、另一方面,通过所述内核确认出现所述异常事件之后,还包括:

10、构建异常编码,所述异常编码的数据位至少为6位;

11、确定所述异常事件的事件类型,所述事件类型为通用异常和引擎异常;

12、根据所述事件类型确定所述异常编码的最高位的数据;

13、确定所述异常事件的错误类型,所述错误类型为异常告警和异常错误;

14、根据所述错误类型确定所述异常编码的次高位的数据;

15、确定所述异常事件的异常类别;

16、根据所述异常类别生成所述异常编码的高6位中除所述最高位和所述次高位之外其余位的数据;

17、获取表征所述同步异常源存储位置的独热编码和表征所述异步异常源存储位置的数据编码;

18、将所述独热编码和所述数据编码与所述异常编码建立映射关系;

19、根据所述映射关系进行异常处理;

20、当所述异常编码共设置有12位时,还包括:

21、按照所述异常事件的优先级顺序生成所述异常编码的低6位的数据;

22、获取所述高6位的数据和所述低6位的数据组成所述异常编码。

23、另一方面,在所述通过中断状态寄存器对所述同步异常源生成中断信号之后,在所述根据所述中断信号得到中断输出信号,并传输所述中断输出信号至所述中断控制器之前,还包括:

24、判断所述中断信号是否为表征原始状态的原始中断信号;

25、若所述中断信号是所述原始中断信号,则将所述原始中断信号屏蔽为0;

26、若所述中断信号不是所述原始中断信号,则判断所述中断信号是否为0;

27、若所述中断信号为0,则确定所述中断信号有效,并进入所述根据所述中断信号得到中断输出信号,并传输所述中断输出信号至所述中断控制器的步骤。

28、另一方面,所述基于全部的所述异步异常源生成先入先出队列包括:

29、对全部的表征所述异步异常源存储位置的数据编码按照预设时间顺序进行仲裁轮询;

30、并对满足仲裁轮询要求的所述数据编码赋予仲裁权;

31、获取具有所述仲裁权的所述数据编码对应的所述异常编码;

32、根据所述异常编码生成所述先入先出队列。

33、另一方面,所述通过中断状态寄存器对所述同步异常源生成中断信号包括:

34、判断中断使能寄存器是否处于工作状态;

35、若所述中断使能寄存器不处于工作状态,则发送使能信号至所述中断使能寄存器;

36、若所述中断使能寄存器处于工作状态,则通过所述中断状态寄存器输出各所述同步异常源的状态信息;

37、基于所述状态信息,通过所述中断屏蔽寄存器生成表征记录操作或补充操作或上报操作的所述中断信号;

38、基于所述状态信息,通过所述中断清除寄存器生成表征清除操作或上报操作的所述中断信号。

39、另一方面,还包括:

40、判断是否接收到表征通过异常调试使能寄存器开启调试操作的调试信号;

41、若接收到所述调试信号,则插入所述异常事件对应的所述同步异常源或所述异步异常源;

42、当根据所述调试信号插入所述异常事件对应的所述同步异常源时,进入所述通过中断状态寄存器对所述同步异常源生成中断信号的步骤;

43、当根据所述调试信号插入所述异常事件对应的所述异步异常源时,进入所述在所述异常处理模块中查找对应的异步异常源的步骤。

44、另一方面,包括:

45、判断是否接收到表征通过异常调试掩码寄存器退出调试操作的退出信号;

46、若接收到所述退出信号,则退出所述调试操作;

47、若未接收到所述退出信号,则等待预设时长后,退出所述调试操作,并输出表征退出所述调试操作的提示信息。

48、为解决上述技术问题,本发明还提供了一种系统级芯片的异常处理装置,应用于至少设置有内核、中央处理器、异常处理模块、中断控制器、内存的系统级芯片,所述装置包括:

49、采集模块,用于从所述内核中采集全部的异常事件对应的错误属性,所述错误属性为同步异常和异步异常;

50、第一查找模块,用于当确定所述错误属性为所述同步异常时,在所述异常处理模块中查找对应的同步异常源;

51、第一生成模块,用于通过中断状态寄存器对所述同步异常源生成中断信号;

52、得到传输模块,用于根据所述中断信号得到中断输出信号,并传输所述中断输出信号至所述中断控制器,以便于根据所述中断输出信号进行同步异常处理;

53、第二查找模块,用于当确定所述错误类型为所述异步异常时,在所述异常处理模块中查找对应的异步异常源;

54、第二生成模块,用于基于全部的所述异步异常源生成先入先出队列,并传输所述先入先出队列至所述内存中,以便于根据所述先入先出队列进行异步异常处理。

55、为解决上述技术问题,本发明还提供了一种系统级芯片的异常处理设备,包括:

56、存储器,用于存储计算机程序;

57、处理器,用于指向计算机程序,实现系统级芯片的异常处理方法的步骤。

58、为解决上述技术问题,本发明还提供了一种非易失性存储介质,该非易失性存储介质上存储有计算机程序,计算机程序被处理器执行时,实现上述全部系统级芯片的异常处理方法的步骤。

59、本发明所提供的一种系统级芯片的异常处理方法,将同步属性的异常事件和异步属性的异常事件进行区分,此时,同步异常对应的同步异常源能够通过中断状态寄存器生成中断信号;并根据所述中断信号得到中断输出信号,传输所述中断输出信号至所述中断控制器,以便于根据所述中断输出信号进行同步异常处理,异步异常对应的异步异常源能够生成先入先出队列,并传输所述先入先出队列至所述内存中,以便于根据所述先入先出队列进行异步异常处理,此时同步异常源和异步异常源分别具有不同的异常处理方式,无需停止系统级芯片当前正在进行的进程,由此实现了提高异常处理效率。

60、另外,对出现的异常构建格式统一的异常编码,能够进一步简化系统级芯片的程序,进一步提高异常处理效率,并且统一格式的异常编码能够保证异常处理的效果更好;且为了能够对某些异常源进行调试,还在异常调试使能寄存器接收到所述调试信号的情况下插入所述异常事件对应的所述同步异常源或所述异步异常源,以便于通过调试操作纠正异常,此时更进一步提高了异常处理的效果。

61、本发明还提供了一种系统级芯片的异常处理装置、设备及介质,效果同上。

本文地址:https://www.jishuxx.com/zhuanli/20240802/260831.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。