一种高功率密度TVS器件及其制造方法

- 国知局

- 2024-08-08 17:06:38

本发明属于半导体功率器件,具体涉及一种高功率密度瞬态电压抑制器件(transient voltage suppressor,tvs)及其制造方法。

背景技术:

1、电浪涌/瞬态电压,指的是在电路中突然出现的随机且超过正常情况下的高电压或者大电流,其特点为发生时间短,瞬时能量非常大。电浪涌对电子元件与集成电路有着很强的破坏性,轻则诱发逻辑电路产生误动作,重则导致三极管的二次击穿、互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)的闩锁效应等严重热效应使得器件或者集成电路失效。电浪涌通常有两种具有随机性的来源,第一种是电网的不稳定因素,比如突然的开关通断、容性或者感性负载的突然启动、相关设备的热插拔、相关电力电源运行不稳定等。第二种是外界的突发干扰,比如雷电、静电放电等。

2、tvs器件是一种重要的半导体保护器件,开启时具有极低的电阻值,可以吸收高达数千瓦的瞬态脉冲功率,并将端口的电压钳位在一个较为安全的预设值,从而保护相应电路免受由于瞬态电压脉冲或电流浪涌带来的损伤甚至不可逆的损坏。tvs器件具有响应速度快、漏电小、瞬态功率高、体积小等特点,目前已经广泛应用于机电系统、电源设备、电磁干扰抑制、输入输出接口、通讯设备、继电器等各个领域的过压保护。

3、然而,对于常规横向tvs器件,其泄放瞬态脉冲电流的能力与器件面积成正比,更高的保护能力就意味着更大的器件的面积,这为现代集成电子系统的小型化和便捷性带来了巨大的挑战。

技术实现思路

1、本发明要解决的技术问题是:在不增大器件面积的情况下,通过对tvs器件结构和制造工艺的改进,提高tvs器件的过电流能力,增大tvs器件在单位面积下能够承受的最大瞬态脉冲功率。

2、为解决上述技术问题,本发明的技术方案如下:

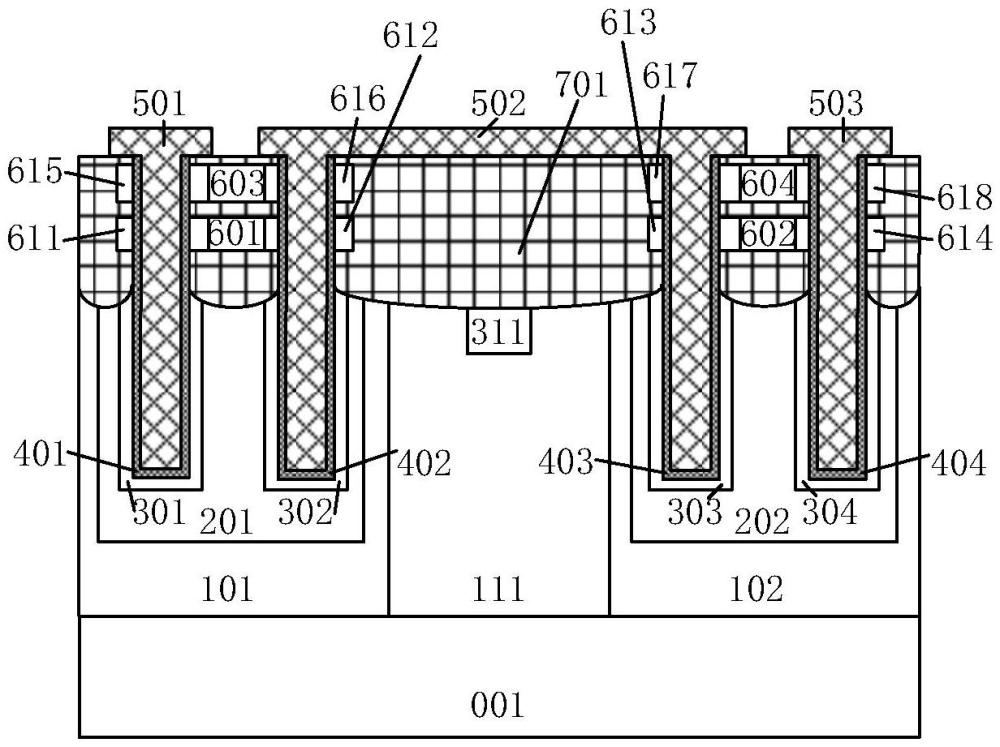

3、一种高功率密度tvs器件,由至少两个基本结构单元通过第二金属铝区502串联堆叠而成;

4、所述基本结构单元由具有深沟槽形n+的硅基npn结构和位于该硅基npn上方的被介质区701隔离的两个多晶硅npn结构组成,上述硅基npn结构和多晶硅npn结构通过金属钨和金属铝并联在一起;介质区701位于n型衬底001上方,其下边缘与n型衬底001上边缘相切;

5、所述两个基本结构单元中的硅基npn结构分别位于第一n型深阱区101和第二n型深阱区102中,第一n型深阱区101和第二n型深阱区102中间由第一p型深阱区111实现电学隔离,并在第一p型深阱区111内部上方加入第一p+区311以提高隔离区性能。

6、第一n型深阱区101、第二n型深阱区102和第一p型深阱区111位于n型衬底001内部,其上边缘与n型衬底001上边缘相切,其下边缘高于n型衬底001下边缘;其中,第一n型深阱区101与第一p型深阱区111相邻且第一n型深阱区101位于第一p型深阱区111左侧,第一p型深阱区111与第二n型深阱区102相邻且第一p型深阱区111位于第二n型深阱区102左侧;

7、第一p+区311位于第一p型深阱区111内部,其上边缘与第一p型深阱区111上边缘相切,其下边缘高于第一p型深阱区111下边缘。

8、作为优选方式,第一n+区301、第二n+区302和第一p型阱区201构成第一有深沟槽形n+的硅基npn结构,第三n+区303、第四n+区304和第二p型阱区202构成第二具有深沟槽形n+的硅基npn结构;

9、第一p型阱区201位于第一n型深阱区101内部,其上边源与第一n型深阱区101上边缘相切,其下边缘高于第一n型深阱区101下边缘;第二p型阱区202位于第二n型深阱区102内部,其上边源与第二n型深阱区102上边缘相切,其下边缘高于第二n型深阱区102下边缘;

10、第一n+区301和第二n+区302位于第一p型阱区201内部,其上边缘与第一p型阱区201上边缘相切,其下边缘高于第一p型阱区201下边缘,其中,第一n+区301位于第二n+区302左侧,两侧保持一定间隔;

11、第三n+区303和第四n+区304位于第二p型阱区202内部,其上边缘与第二p型阱区202上边缘相切,其下边缘高于第二p型阱区202下边缘,其中,第三n+区303位于第四n+区304左侧,两侧保持一定间隔。

12、作为优选方式,第一p型多晶硅区601、第一n+多晶硅区611和第二n+多晶硅区612组成第一多晶硅npn结构;具体的,第一n+多晶硅区611、第一p型多晶硅区601和第二n+多晶硅区612从左至右无缝依次排列,周围被介质区701包裹以实现电学隔离;

13、第二p型多晶硅区602、第三n+多晶硅区613和第四n+多晶硅区614组成第二多晶硅npn结构;具体的,第三n+多晶硅区613、第二p型多晶硅区602和第四n+多晶硅区614从左至右无缝依次排列,周围被介质区701包裹以实现电学隔离;

14、第三p型多晶硅区603、第五n+多晶硅区615和第六n+多晶硅区616组成第三多晶硅npn结构;具体的,第五n+多晶硅区615、第三p型多晶硅区603和第六n+多晶硅区616从左至右无缝依次排列,周围被介质区701包裹以实现电学隔离;

15、第四p型多晶硅区604、第七n+多晶硅区617和第八n+多晶硅区618组成第四多晶硅npn结构;具体的,第七n+多晶硅区617、第四p型多晶硅区604和第八n+多晶硅区618从左至右无缝依次排列,周围被介质区701包裹以实现电学隔离。

16、作为优选方式,

17、第一p型多晶硅区601位于介质区701内部左侧偏下位置,其左右边缘分别与第一p型阱区201的左右边缘相切,其下边缘高于n型衬底001的上边缘,其上边缘低于第三p型多晶硅区603的下边缘;

18、第二p型多晶硅区602位于介质区701内部右侧偏下位置,其左右边缘分别与第二p型阱区202的左右边缘相切,其下边缘高于n型衬底001的上边缘,其上边缘低于第四p型多晶硅区604的下边缘;

19、第三p型多晶硅区603位于介质区701内部左侧偏上位置,其左右边缘分别与第一p型阱区201的左右边缘相切,其下边缘高于第一p型多晶硅区601上边缘,其上边缘低于介质区701的上边缘;

20、第四p型多晶硅区604位于介质区701内部右侧偏上位置,其左右边缘分别与第二p型阱区202的左右边缘相切,其下边缘高于第二p型多晶硅区602上边缘,其上边缘低于介质区701的上边缘;

21、第一n+多晶硅区611位于第一p型多晶硅区601内部左侧,其上边缘、下边缘和左边缘分别与第一p型多晶硅区601上边缘、下边缘和左边缘相切;

22、第二n+多晶硅区612位于第一p型多晶硅区601内部右侧,其上边缘、下边缘和右边缘分别与第一p型多晶硅区601上边缘、下边缘和右边缘相切;第一n+多晶硅区611的右边缘位于第二n+多晶硅区612左边缘的左侧并保持一定间距;

23、第三n+多晶硅区613位于第二p型多晶硅区602内部左侧,其上边缘、下边缘和左边缘分别与第二p型多晶硅区602上边缘、下边缘和左边缘相切;

24、第四n+多晶硅区614位于第二p型多晶硅区602内部右侧,其上边缘、下边缘和右边缘分别与第二p型多晶硅区602上边缘、下边缘和右边缘相切;第三n+多晶硅区613的右边缘位于第四n+多晶硅区614左边缘的左侧并保持一定间距;

25、第五n+多晶硅区615位于第三p型多晶硅区603内部左侧,其上边缘、下边缘和左边缘分别与第三p型多晶硅区603上边缘、下边缘和左边缘相切;

26、第六n+多晶硅区616位于第三p型多晶硅区603内部右侧,其上边缘、下边缘和右边缘分别与第三p型多晶硅区603上边缘、下边缘和右边缘相切;第五n+多晶硅区615的右边缘位于第六n+多晶硅区616左边缘的左侧并保持一定间距;

27、第七n+多晶硅区617位于第四p型多晶硅区604内部左侧,其上边缘、下边缘和左边缘分别与第四p型多晶硅区604上边缘、下边缘和左边缘相切;

28、第八n+多晶硅区618位于第四p型多晶硅区604内部右侧,其上边缘、下边缘和右边缘分别与第四p型多晶硅区604上边缘、下边缘和右边缘相切;第七n+多晶硅区617的右边缘位于第八n+多晶硅区618左边缘的左侧并保持一定间距;

29、第一金属钨区401纵跨第一n+区301、第一n+多晶硅区611、第五n+多晶硅区615和介质区701,第一金属钨区401的上边缘与介质区701上边缘相切,其下边缘高于第一n+区301,其宽度窄于第一n+区301,第一金属钨区401的下半部分被第一n+区301包裹;

30、第二金属钨区402纵跨第二n+区302、第二n+多晶硅区612、第六n+多晶硅区616和介质区701,第二金属钨区402的上边缘与介质区701上边缘相切,其下边缘高于第二n+区302,其宽度窄于第二n+区302,第二金属钨区402的下半部分被第二n+区302包裹;

31、第三金属钨区403纵跨第三n+区303、第三n+多晶硅区613、第七n+多晶硅区617和介质区701,第三金属钨区403的上边缘与介质区701上边缘相切,其下边缘高于第三n+区303,其宽度窄于第三n+区303,第三金属钨区403的下半部分被第三n+区303包裹;

32、第四金属钨区404纵跨第四n+区304、第四n+多晶硅区614、第八n+多晶硅区618和介质区701,第四金属钨区404的上边缘与介质区701上边缘相切,其下边缘高于第四n+区304,其宽度窄于第三n+区304,第四金属钨区404的下半部分被第四n+区304包裹;

33、第一金属铝区501的下半部分即未超出介质区701上边缘的部分被第一金属钨区401包围,第一金属铝区501下半部分的左边缘、右边缘和下边缘分别与第一金属钨区401的左边缘、右边缘和下边缘保持一定间距,第一金属铝区501的上半部分即超出介质区701上边缘的部分的宽度宽于第一金属铝区501的下半部分的宽度;

34、第二金属铝区502下半部分即未超出介质区701上边缘的部分的左侧部分被第二金属钨区402包围,其左边缘、右边缘和下边缘分别与第二金属钨区402的左边缘、右边缘和下边缘保持一定间距,第二金属铝区502下半部分的右侧部分被第三金属钨区403包围,其左边缘、右边缘和下边缘分别与第三金属钨区403的左边缘、右边缘和下边缘保持一定间距,第二金属铝区502上半部分即超出介质区701上边缘的部分连接了第二金属铝区502下半部分的左右两部分;

35、第三金属铝区503的下半部分即未超出介质区701上边缘的部分被第四金属钨区404包围,第三金属铝区503下半部分的左边缘、右边缘和下边缘分别与第四金属钨区404的左边缘、右边缘和下边缘保持一定间距,第三金属铝区503的上半部分即超出介质区701上边缘的部分的宽度宽于第三金属铝区503的下半部分的宽度。

36、作为优选方式,将基本结构单元的npn结构替换成scr结构。

37、作为优选方式,将基本结构单元的npn结构替换成pnp结构。

38、作为优选方式,将基本结构单元的npn结构替换成二极管结构。

39、本发明还提供一种所述的高功率密度tvs器件的制造方法,包括以下步骤:

40、(1)准备n型衬底;

41、(2)使用硅局部氧化工艺在n型衬底上生长隔离介质二氧化硅;

42、(3)通过离子注入和热推阱,形成n型深阱区和p型深阱区;

43、(4)通过离子注入和热推阱形成p型阱区;

44、(5)刻蚀p型阱区的部分区域形成深沟槽;

45、(6)通过离子注入和热激活形成n+区和p+区;

46、(7)在沟槽中填充金属钨和金属铝;

47、(8)生长或淀积隔离介质后化学机械抛光;

48、(9)在介质区上方淀积多晶硅,并刻蚀形成分段多晶硅区;

49、(10)通过离子注入和热过程形成n+多晶硅区;

50、(11)生长或淀积隔离介质后化学机械抛光;

51、(12)在介质区上方淀积多晶硅,并刻蚀形成分段多晶硅区;

52、(13)通过离子注入和热过程形成n+多晶硅区;

53、(14)生长或淀积隔离介质后化学机械抛光;

54、(15)使用刻蚀工艺挖沟槽暴露出第一金属钨区和金属铝区;

55、(16)在沟槽中填充金属钨和金属铝,并通过光刻和刻蚀调整其超出介质区的部分;

56、(17)后续处理形成高功率密度的tvs器件。

57、本发明的有益效果为:本发明在不增加器件面积的基础上,通过对器件结构和制造方法的优化设计,形成了具有深沟槽形的n+区和具有esd防护能力多晶硅npn区;其中,深沟槽形的n+区增大了器件的有效过流面积,提高了器件tvs器件在大电流下的电流均匀性,多晶硅npn区也能提供一定的泄放电流的能力。通过上述深沟槽形n+区和多晶硅npn区的结合,本发明能够在不增大器件面积的情况下,显著地提高器件地泄放电流能力,增大tvs器件在单位面积下能够承受的最大瞬态脉冲功率。

本文地址:https://www.jishuxx.com/zhuanli/20240808/272401.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表