一种基于对准键合的光电器件及其制备方法与流程

- 国知局

- 2024-08-22 14:59:16

本发明涉及半导体,尤其是指一种基于对准键合的光电器件及其制备方法。

背景技术:

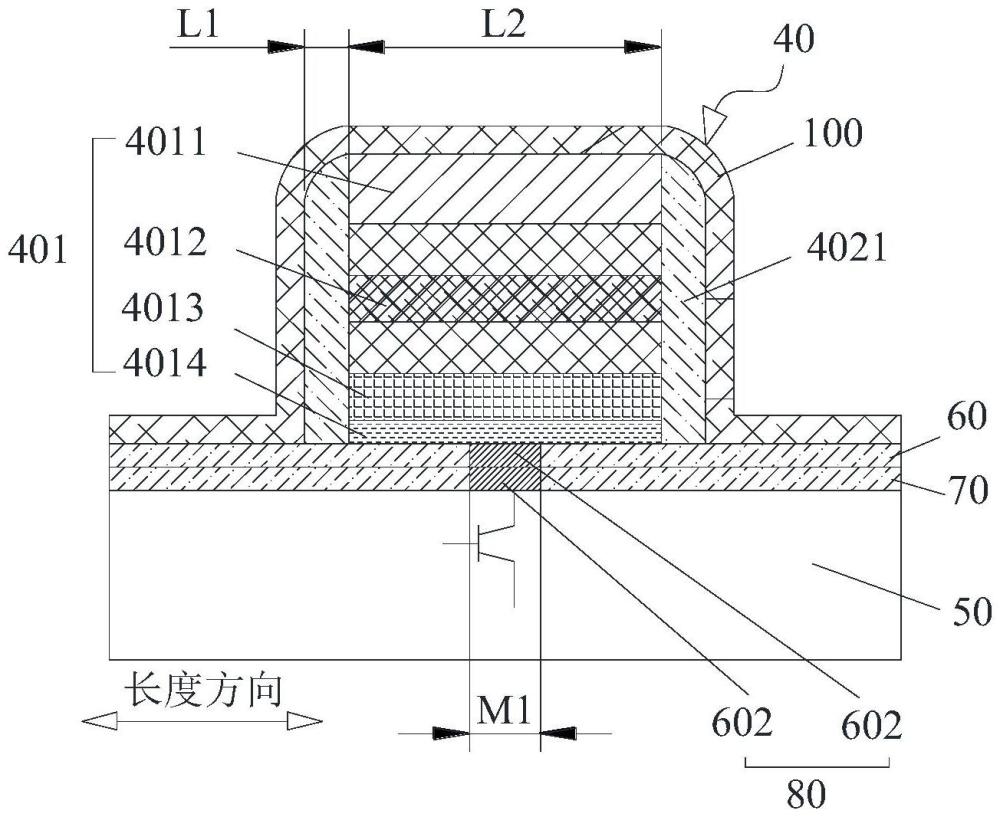

1、现有的led光电器件的像素单元40一般包括p型半导体层4013和n型半导体层4011,如图1所示,p型半导体层4013需要和驱动晶圆50的阳极触点101进行电连接,现有的像素单元40通常通过键合金属层10和驱动晶圆50进行键合而实现阳极连接,但是当p型半导体层4013和键合金属层10之间存在绝缘介质层20时,则需要在像素单元40外部另外设置导电的阳极连接件30来实现阳极联通,这导致光电器件结构更加复杂且不易加工,且该阳极连接件一旦发生变形或安装偏差,也容易引发p型半导体层4013和n型半导体层4011之间发生短路漏电现象,从而引发led光电器件发生失效现象。

2、因此,现有的led光电器件阳极连接结构复杂且不易加工,无法有效保证阳极连接的便捷性,同时也容易发生短路漏电现象,从而无法保证led光电器件的使用可靠性。

技术实现思路

1、为此,本发明所要解决的技术问题在于克服现有技术中led光电器件无法有效保证阳极连接的便捷性且容易发生短路漏电的缺陷,以提升led光电器件的使用可靠性。

2、为解决上述技术问题,本发明提供了一种基于对准键合的光电器件,包括,

3、驱动晶圆,所述驱动晶圆上设置有第二绝缘层,所述第二绝缘层设置有通孔,所述通孔内填充有阳极金属件;

4、像素单元,所述像素单元包括像素主体和外缘壁体,所述外缘壁体设置于所述像素主体的侧壁上,所述外缘壁体包括第一壁体层,所述第一壁体层为绝缘体,所述第一壁体层与所述像素主体的侧壁相贴合;

5、所述像素主体包括沿远离所述驱动晶圆方向依次设置的p型半导体层、有源层和n型半导体层;每个所述像素单元中的所述n型半导体层和p型半导体层之间通过所述第一壁体层相绝缘;

6、所述第二绝缘层和像素单元的p型半导体层之间还设置有第一绝缘层,所述第一绝缘层上也设置有通孔,所述通孔内填充有阳极金属件,所述第一绝缘层的通孔和所述第二绝缘层的通孔一一对应,所述第一绝缘层通孔内的阳极金属件和对应的所述第二绝缘层通孔内的阳极金属件相互键合形成键合主体,所述p型半导体层通过键合主体和所述驱动晶圆电连接;

7、其中,所有所述像素单元中的n型半导体层通过共阴极相连接。

8、在本发明的一个实施方案中,所所述第一绝缘层和/或第二绝缘层的所述阳极金属件包括本体端,所述本体端位于所述通孔内,所述本体端上形成有扩展端,所述扩展端的长度大于所述本体端的长度。

9、在本发明的一个实施方案中,所所述键合主体中阳极金属件的扩展端位于所述第一绝缘层和第二绝缘层之间。

10、在本发明的一个实施方案中,所所述第一绝缘层和第二绝缘层之间设置有第三绝缘层,所述扩展端位于所述第三绝缘层中。

11、在本发明的一个实施方案中,所所述扩展端的长度不小于所述像素主体长度的0.5倍。

12、在本发明的一个实施方案中,所述通孔的长度为像素主体长度的0.1~0.5倍。

13、在本发明的一个实施方案中,所述外缘壁体还包括第二壁体层,所述第二壁体层与所述第一壁体层的外壁相贴合。

14、在本发明的一个实施方案中,所述第二壁体层为反射层或导电层中的一种,或者为反射层和导电层构成的复合层。

15、在本发明的一个实施方案中,所述第一壁体层靠近所述驱动晶圆的一端形成有台阶部,所述第二壁体层位于所述台阶部上。

16、在本发明的一个实施方案中,每个所述像素单元的两侧还设置有金属网栅,所述金属网栅和所述共阴极电连接。

17、在本发明的一个实施方案中,所述金属网栅位于所述共阴极和所述第一绝缘层之间。

18、本发明还公开了一种基于对准键合的光电器件的制备方法,包括,

19、制备驱动晶圆,使得所述驱动晶圆上设置有第二绝缘层,所述第二绝缘层设置有通孔,所述通孔内填充有阳极金属件;

20、以及制备化合物半导体,所述化合物半导体包括衬底、以及沿远离所述衬底方向依次形成的n型半导体层、有源层、p型半导体层和第一绝缘层;在所述第一绝缘层上设置通孔,所述通孔内填充有阳极金属件,所述第二绝缘层的通孔和所述第一绝缘层的通孔一一对应;

21、将所述第一绝缘层通孔内的阳极金属件和对应的所述第二绝缘层通孔内的阳极金属件相互键合形成键合主体,使得所述p型半导体层通过键合主体和所述驱动晶圆电连接;

22、对所述化合物半导体进行处理而形成与所述键合主体相对应的像素单元;所述像素单元包括像素主体和外缘壁体,所述外缘壁体设置于所述像素主体的侧壁上,所述外缘壁体包括第一壁体层,所述第一壁体层为绝缘体,所述第一壁体层与所述像素主体的侧壁相贴合;每个所述像素主体均包括沿远离所述驱动晶圆方向依次设置的p型半导体层、有源层和n型半导体层;每个所述像素单元中的所述n型半导体层和p型半导体层之间通过所述第一壁体层相绝缘;

23、将所述像素单元中的n型半导体层与共阴极相连接。

24、在本发明的一个实施方案中,对所述化合物半导体进行处理而形成与所述键合主体相对应的像素单元的方法,包括,

25、步骤s1)、去除化合物半导体的衬底;

26、步骤s2)、通过第一刻蚀方式对化合物半导体进行刻蚀,刻蚀时以第一绝缘层为刻蚀截止层,刻蚀后获得与所述键合主体相对应的像素主体;

27、步骤s3)、在所述像素主体的外部沉积第一壁体层,并利用干法刻蚀方式对所述第一壁体层进行刻蚀,刻蚀后仅保留位于所述像素主体侧壁处的第一壁体层。

28、在本发明的一个实施方案中,在步骤s3)中,在所述像素主体的外部沉积第一壁体层之后还需沉积第二壁体层,全部沉积完成后,再利用干法刻蚀方式对第一壁体层和第二壁体层构成的整体结构进行整体刻蚀,刻蚀后仅保留位于所述像素主体侧壁处的第一壁体层和第二壁体层;

29、或者,在所述像素主体的外部沉积第一壁体层之后,先利用干法刻蚀方式对所述第一壁体层进行刻蚀,刻蚀后仅保留位于所述像素主体侧壁处的第一壁体层,然后再在第一壁体层的外部沉积第二壁体层,沉积完成后,再利用干法刻蚀方式对第二壁体层进行刻蚀,刻蚀后仅保留位于所述像素主体侧壁处的第二壁体层。

30、在本发明的一个实施方案中,制备化合物半导体时,在第一绝缘层的通孔内形成阳极金属件时,使得所述阳极金属件包括本体端,并在所述本体端上形成有扩展端,所述本体端位于所述通孔内,所述扩展端的长度大于所述本体端的长度。

31、在本发明的一个实施方案中,将所述第一绝缘层通孔内的阳极金属件和对应的所述第二绝缘层通孔内的阳极金属件相互键合形成键合主体时,所述键合主体中阳极金属件的扩展端位于所述第一绝缘层和第二绝缘层之间。

32、在本发明的一个实施方案中,将所述像素单元中的n型半导体层与共阴极连接之前,还需在每个所述像素单元的两侧形成金属网栅,所述金属网栅沉积于所述第一绝缘层上,然后再在所述像素单元外部制备共阴极,并使得所述金属网栅位于所述共阴极和所述第一绝缘层之间。

33、在本发明的一个实施方案中,所述第一绝缘层和第二绝缘层均包括氧化硅、氧化铝、氮化硅、氧化钛或氧化铌中的一种或多种。

34、本发明的上述技术方案相比现有技术具有以下优点:

35、本发明所述的基于对准键合的光电器件及其制备方法,第一绝缘层的通孔和第二绝缘层的通孔一一对准,从而使得第一绝缘层通孔内的阳极金属件和对应的第二绝缘层通孔内的阳极金属件相互键合形成导电的键合主体,不仅可以有效保证阳极电流增强效果,也更便于布置和加工,也利于避免像素单元内部发生漏电现象;另外,使得n型半导体层和p型半导体层之间通过第一壁体层相绝缘,也可以更好的避免像素单元发生短路漏电现象,能够有效提升光电器件的使用可靠性。

本文地址:https://www.jishuxx.com/zhuanli/20240822/280675.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表