静电防护电路、静电防护器件及其制造方法与流程

- 国知局

- 2024-09-05 14:54:19

本公开涉及半导体制造,更具体地,涉及一种静电防护电路、静电防护器件及其制造方法。

背景技术:

1、静电放电(electro-static discharge,esd)防护器件是一种电压钳位型过压保护器件,当被保护电路出现瞬态高能量浪涌脉冲时,能以纳秒到皮秒级的速度迅速开启,将两极间的高阻抗变成低阻抗,能够吸收几瓦到数千瓦的浪涌功率,从而避免电子设备损坏。

2、可控硅整流器(silicon controlled rectifiers,scr)作为静电防护器件的结构之一,具有电流泄放效率高、自身抗静电能力强、静态漏电低、寄生电容小的优点,但其触发电压高,维持电压vh只有1~2v,低于被保护器件的工作电压易造成闩锁问题,电源保护电路的工作电压一般在3.3v以上,导致可控硅整流器不适合应用在电源保护电路。因此为了提高可控硅整流器的抗闩锁能力,必须将维持电压vh提升到电源工作电压之上。

3、因此,研究出一款维持电压vh可调控的新型静电防护器件是本领域的技术人员亟待解决的技术问题。

技术实现思路

1、鉴于上述问题,本公开的目的在于提供一种静电防护电路、静电防护器件及其制造方法,通过让横向可控硅整流器结构与纵向的维持电压提升模块串联,以适应绝大部分的维持电压的应用场景。

2、根据本公开实施例的第一方面,提供了一种静电防护电路,包括:

3、第一晶体管、第二晶体管和第一电阻,所述第一晶体管的基极连接所述第二晶体管的集电极,所述第一晶体管的集电极连接所述第二晶体管的基极,所述第一晶体管的发射极连接第一电位,所述第一电阻串联在所述第二晶体管的基极与发射极之间;

4、第二电阻和第一二极管,所述第二电阻串联在所述第一电位与所述第一二极管的阴极之间,所述第一二极管的阳极连接第二电位;以及

5、维持电压提升模块,所述维持电压提升模块的一端连接所述第二晶体管的发射极,另一端连接所述第二电位,

6、所述第一晶体管为pnp三极管,所述第二晶体管为npn三极管,

7、其中,当所述第一电位大于所述第二电位时,电流经过所述第一晶体管、所述第二晶体管、所述第一电阻以及所述维持电压提升模块的路径以释放静电,所述第一二极管和所述第二电阻的路径反向截止,

8、当所述第一电位小于所述第二电位时,电流经过所述第一二极管和所述第二电阻的路径以释放静电,所述第一晶体管、所述第二晶体管、所述第一电阻以及所述维持电压提升模块的路径反向截止。

9、可选地,所述维持电压提升模块为第三电阻,

10、所述第三电阻的一端连接所述第二晶体管的发射极,另一端连接所述第二电位。

11、可选地,所述维持电压提升模块为第三电阻与第二二极管,

12、所述第三电阻的一端连接所述第二晶体管的发射极,另一端连接所述第二二极管的阴极,所述第二二极管的阳极连接所述第二电位。

13、可选地,所述第二二极管为稳压二极管。

14、可选地,所述维持电压提升模块为第三电阻与第三晶体管,

15、所述第三电阻的一端连接所述第二晶体管的发射极,另一端连接所述第三晶体管的发射极,所述第三晶体管的集电极连接所述第二电位,所述第三晶体管的基极悬空。

16、可选地,所述第三晶体管为pnp三极管。

17、可选地,还包括触发电压降低模块,所述触发电压降低模块的一端连接所述第二晶体管的集电极,另一端连接所述第二晶体管的发射极或基极。

18、可选地,所述触发电压降低模块为第三二极管,

19、所述第三二极管的阴极连接所述第二晶体管的集电极,所述第三二极管的阳极连接所述第二晶体管的发射极。

20、可选地,所述第三二极管为稳压二极管。

21、可选地,所述触发电压降低模块为第四晶体管,

22、所述第四晶体管的集电极连接所述第二晶体管的集电极,

23、所述第四晶体管的发射极连接所述第二晶体管的基极,

24、所述第四晶体管的基极悬空,

25、其中,所述第一晶体管的发射极还连接所述第二晶体管的集电极。

26、可选地,所述第四晶体管为npn三极管。

27、可选地,所述静电防护电路的维持电压的范围包括3~37v。

28、可选地,所述第一晶体管、所述第二晶体管和所述第一电阻用于构成可控硅整流器结构。

29、可选地,所述可控硅整流器结构包括多个并联的可控硅整流器单元,每个所述可控硅整流器单元包括所述第一晶体管、所述第二晶体管和所述第一电阻。

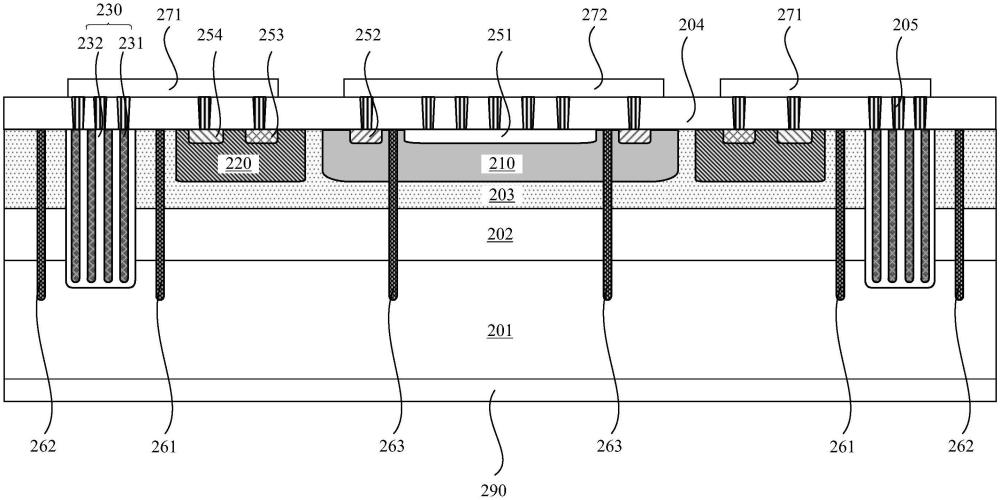

30、根据本公开实施例的第二方面,提供了一种静电防护器件,包括:

31、衬底;

32、第一外延层,位于所述衬底上;

33、第二外延层,位于所述第一外延层上;

34、第一阱区与第二阱区,位于所述第二外延层中;

35、第一掺杂区与第二掺杂区,位于所述第一阱区中;

36、第三掺杂区与第四掺杂区,位于所述第二阱区中;

37、纵向连接区,自所述第二外延层表面向所述衬底方向延伸;

38、第一隔离结构,自所述第二外延层表面延伸至所述衬底中,以将所述第一阱区与所述纵向连接区隔开、将所述第二阱区与所述纵向连接区隔开;

39、隔离层,位于所述第二外延层上;

40、第一导电层,位于所述隔离层上,所述第一导电层通过连接柱电连接所述第三掺杂区、所述第四掺杂区和所述纵向连接区;以及

41、第二导电层,位于所述隔离层上,所述第二导电层通过连接柱电连接所述第一掺杂区与所述第二掺杂区,

42、其中,所述衬底、所述第一外延层、所述第二阱区、所述第二掺杂区和所述第四掺杂区为第一掺杂类型,所述第二外延层、所述第一阱区、所述第一掺杂区和所述第三掺杂区为第二掺杂类型,所述第一掺杂类型与所述第二掺杂类型相反。

43、可选地,所述第二外延层、所述第一阱区、所述第二掺杂区、所述第二阱区、所述第三掺杂区和第四掺杂区用于构成互补型的第一晶体管与第二晶体管,所述第一晶体管为pnp三极管,所述第二晶体管为npn三极管,

44、所述第二阱区与所述第四掺杂区用于构成第一电阻,

45、所述第一阱区与所述第一掺杂区用于构成第二电阻,

46、所述第一外延层与所述第二外延层用于构成第一二极管,

47、所述纵向连接区用于构成维持电压提升模块,

48、所述第一晶体管的发射极连接第一电位,所述第一晶体管的基极连接所述第二晶体管的集电极,所述第一晶体管的集电极连接所述第二晶体管的基极,所述第一电阻串联在所述第二晶体管的基极与发射极之间;

49、所述第二电阻串联在所述第一电位与所述第一二极管的阴极之间,所述第一二极管的阳极连接第二电位,

50、维持电压提升模块的一端连接所述第二晶体管的发射极,另一端连接所述第二电位,

51、当所述第一电位大于所述第二电位时,电流经过所述第一晶体管、所述第二晶体管、所述第一电阻以及所述维持电压提升模块的路径以释放静电,所述第一二极管和所述第二电阻的路径反向截止,

52、当所述第一电位小于所述第二电位时,电流经过所述第一二极管和所述第二电阻的路径以释放静电,所述第一晶体管、所述第二晶体管、所述第一电阻以及所述维持电压提升模块的路径反向截止。

53、可选地,所述纵向连接区包括多个沟槽,多晶硅填充结构填充在所述沟槽中并形成扩散区,所述多晶硅填充结构自所述第二外延层表面向所述衬底方向延伸;

54、或者,所述纵向连接区包括多个沟槽,金属填充结构填充在所述沟槽中,所述金属填充结构自所述第二外延层表面向所述衬底方向延伸。

55、可选地,所述纵向连接区自所述第二外延层表面延伸至所述衬底中,

56、所述维持电压提升模块为第三电阻,所述纵向连接区构成所述第三电阻,

57、其中,所述纵向连接区为第一掺杂类型。

58、可选地,所述第三电阻的一端连接所述第二晶体管的发射极,另一端连接所述第二电位。

59、可选地,所述纵向连接区自所述第二外延层表面延伸至所述衬底中,

60、所述维持电压提升模块为第三电阻与第二二极管,所述纵向连接区构成所述第三电阻,所述纵向连接区与所述衬底构成所述第二二极管,

61、其中,所述纵向连接区为第二掺杂类型。

62、可选地,还包括第一埋层,位于所述衬底与所述第一外延层交界处并位于所述衬底与所述第一外延层中,

63、所述纵向连接区自所述第二外延层表面延伸至所述第一埋层中,

64、所述维持电压提升模块为第三电阻与第二二极管,所述纵向连接区构成所述第三电阻,所述第一埋层和所述衬底构成所述第二二极管,

65、其中,所述纵向连接区与所述第一埋层为第二掺杂类型。

66、可选地,所述第三电阻的一端连接所述第二晶体管的发射极,另一端连接所述第二二极管的阴极,所述第二二极管的阳极连接所述第二电位。

67、可选地,所述第二二极管为稳压二极管。

68、可选地,还包括:

69、第二埋层,位于所述第一外延层中;以及

70、第三埋层,位于所述第一外延层与所述第二外延层交界处并位于所述第一外延层与所述第二外延层中,所述第三埋层位于所述第二埋层上并与所述第二埋层接触,

71、所述纵向连接区自所述第二外延层的表面延伸至所述第三埋层中,

72、所述维持电压提升模块为第三电阻与第三晶体管,所述纵向连接区构成所述第三电阻,所述纵向连接区、所述第三埋层和所述第二埋层构成所述第三晶体管,

73、其中,所述纵向连接区与所述第二埋层为第一掺杂类型,所述第三埋层为第二掺杂类型。

74、可选地,所述第三晶体管为pnp三极管。

75、可选地,所述第三电阻的一端连接所述第二晶体管的发射极,另一端连接所述第三晶体管的发射极,所述第三晶体管的集电极连接所述第二电位,所述第三晶体管的基极悬空。

76、可选地,还包括第二隔离结构,自所述第二外延层的表面延伸至所述衬底中,

77、其中,所述纵向连接区位于所述第一隔离结构与所述第二隔离结构之间。

78、可选地,所述第一晶体管、所述第二晶体管和所述第一电阻用于构成可控硅整流器结构,

79、所述可控硅整流器结构包括至少一个可控硅整流器单元,每个所述可控硅整流器单元包括所述第一阱区、所述第二阱区、所述第一掺杂区、所述第二掺杂区、所述第三掺杂区和所述第四掺杂区,

80、所述第一隔离结构环绕所有的所述可控硅整流器单元,所述纵向连接区位于所述第一隔离结构外侧。

81、可选地,所述可控硅整流器结构仅包括一个可控硅整流器单元,所述第二阱区环绕所述第一阱区,所述第一隔离结构环绕所述第二阱区,所述纵向连接区环绕所述第一隔离结构;

82、所述第二掺杂区、所述第三掺杂区、所述第四掺杂区依次环绕所述第一掺杂区;

83、或者,所述第二掺杂区、所述第四掺杂区、所述第三掺杂区依次环绕所述第一掺杂区。

84、可选地,所述可控硅整流器结构包括多个可控硅整流器单元,多个可控硅整流器单元并联,在每个所述可控硅整流器单元中,所述第一阱区与所述第二阱区沿所述第一方向交替分布,

85、所述第一阱区、所述第二阱区、所述第一掺杂区、所述第二掺杂区、所述第三掺杂区和所述第四掺杂区沿第二方向延伸,所述第一方向和所述第二方向垂直。

86、可选地,所述可控硅整流器结构包括多个可控硅整流器单元,多个可控硅整流器单元并联,在每个可控硅整流器单元中,所述第二阱区环绕所述第一阱区,所述第二掺杂区、所述第三掺杂区、所述第四掺杂区依次环绕所述第一掺杂区;或者,所述第二掺杂区、所述第四掺杂区、所述第三掺杂区依次环绕所述第一掺杂区;

87、所述多个可控硅整流器单元呈阵列分布。

88、可选地,还包括第三隔离结构,自所述第二外延层的表面延伸至所述衬底中,所述第三隔离结构位于所述第一掺杂区和所述第二掺杂区之间并环绕所述第一掺杂区,以分隔所述可控硅整流器结构、所述维持电压提升模块的路径和所述第一二极管、所述第二电阻的路径。

89、可选地,还包括第五掺杂区,位于所述第二外延层中的所述第一阱区和所述第二阱区之间,并分别与所述第一阱区和所述第二阱区连接,

90、其中,所述第二外延层、所述第一阱区、所述第二阱区以及所述第五掺杂区构成第三二极管,

91、所述第五掺杂区用于降低所述静电防护器件的触发电压,所述第三二极管构成触发电压降低模块。

92、可选地,所述第五掺杂区的数量为多个,且分隔设置。

93、可选地,所述第三二极管的阴极连接所述第二晶体管的集电极,所述第三二极管的阳极连接所述第二晶体管的发射极。

94、可选地,所述第三二极管为稳压二极管。

95、可选地,还包括:

96、第三阱区,位于所述第二外延层中且位于所述第一阱区和所述第二阱区之间;

97、第六掺杂区与第七掺杂区,位于所述第三阱区中;

98、第八掺杂区,位于所述第二阱区中;以及

99、第三导电层,位于所述隔离层上,通过连接柱电连接所述第七掺杂区与所述第八掺杂区,

100、所述第二导电层还通过连接柱与所述第六掺杂区电连接,

101、其中,所述第三阱区与所述第八掺杂区为第一掺杂类型,所述第六掺杂区与所述第七掺杂区为第二掺杂类型,

102、所述第三阱区、所述第六掺杂区和所述第七掺杂区构成第四晶体管,用于降低所述静电防护器件的触发电压,所述第四晶体管构成触发电压降低模块。

103、可选地,所述第四晶体管为npn三极管。

104、可选地,所述第四晶体管的集电极连接所述第二晶体管的集电极,

105、所述第四晶体管的发射极连接所述第二晶体管的基极,

106、所述第四晶体管的基极悬空,

107、其中,所述第一晶体管的发射极还连接所述第二晶体管的集电极。

108、可选地,所述静电防护器件的维持电压的范围为3~37v。

109、可选地,所述静电防护器件为单向静电防护器件,所述静电防护器件还包括背面电极,所述背面电极位于所述衬底远离所述第一外延层的一侧。

110、根据本公开实施例的第三方面,提供了一种静电防护器件的制造方法,包括:

111、在衬底上形成第一外延层;

112、在所述第一外延层上形成第二外延层;

113、在所述第二外延层中形成第一阱区与第二阱区;

114、在所述第一阱区中形成第一掺杂区与第二掺杂区;

115、在所述第二阱区中形成第三掺杂区与第四掺杂区;

116、形成纵向连接区,所述纵向连接区自所述第二外延层表面向所述衬底方向延伸;

117、形成第一隔离结构,所述第一隔离结构自所述第二外延层表面延伸至所述衬底中,以将所述第一阱区与所述纵向连接区隔开、将所述第二阱区与所述纵向连接区隔开;

118、在所述第二外延层上形成隔离层;

119、在所述隔离层上形成第一导电层,所述第一导电层通过连接柱电连接所述第三掺杂区、所述第四掺杂区和所述纵向连接区;以及

120、在所述隔离层上形成第二导电层,所述第二导电层通过连接柱电连接所述第一掺杂区与所述第二掺杂区,

121、其中,所述衬底、所述第一外延层、所述第二阱区、所述第二掺杂区和所述第四掺杂区为第一掺杂类型,所述第二外延层、所述第一阱区、所述第一掺杂区和所述第三掺杂区为第二掺杂类型,所述第一掺杂类型与所述第二掺杂类型相反。

122、可选地,所述第二外延层、所述第一阱区、所述第二掺杂区、所述第二阱区、所述第三掺杂区和第四掺杂区用于构成互补型的第一晶体管与第二晶体管,所述第一晶体管为pnp三极管,所述第二晶体管为npn三极管,

123、所述第二阱区与所述第四掺杂区用于构成第一电阻,

124、所述第一阱区与所述第一掺杂区用于构成第二电阻,

125、所述第一外延层与所述第二外延层用于构成第一二极管,

126、所述纵向连接区用于构成维持电压提升模块,

127、所述第一晶体管的发射极连接第一电位,所述第一晶体管的基极连接所述第二晶体管的集电极,所述第一晶体管的集电极连接所述第二晶体管的基极,所述第一电阻串联在所述第二晶体管的基极与发射极之间;

128、所述第二电阻串联在所述第一电位与所述第一二极管的阴极之间,所述第一二极管的阳极连接第二电位,

129、维持电压提升模块的一端连接所述第二晶体管的发射极,另一端连接所述第二电位,

130、当所述第一电位大于所述第二电位时,电流经过所述第一晶体管、所述第二晶体管、所述第一电阻以及所述维持电压提升模块的路径以释放静电,所述第一二极管和所述第二电阻的路径反向截止,

131、当所述第一电位小于所述第二电位时,电流经过所述第一二极管和所述第二电阻的路径以释放静电,所述第一晶体管、所述第二晶体管、所述第一电阻以及所述维持电压提升模块的路径反向截止。

132、可选地,形成所述纵向连接区包括形成多个沟槽,在所述多个沟槽中填充多晶硅填充结构并形成扩散区,所述多晶硅填充结构自所述第二外延层表面向所述衬底方向延伸;

133、或者,形成所述纵向连接区包括形成多个沟槽,在所述多个沟槽中填充金属填充结构,所述金属填充结构自所述第二外延层表面向所述衬底方向延伸。

134、可选地,所述纵向连接区自所述第二外延层表面延伸至所述衬底中,

135、所述维持电压提升模块为第三电阻,所述纵向连接区构成所述第三电阻,

136、其中,所述纵向连接区为第一掺杂类型。

137、可选地,所述第三电阻的一端连接所述第二晶体管的发射极,另一端连接所述第二电位。

138、可选地,所述纵向连接区自所述第二外延层表面延伸至所述衬底中,

139、所述维持电压提升模块为第三电阻与第二二极管,所述纵向连接区构成所述第三电阻,所述纵向连接区与所述衬底构成所述第二二极管,

140、其中,所述纵向连接区为第二掺杂类型。

141、可选地,还包括形成第一埋层,所述第一埋层位于所述衬底与所述第一外延层交界处并位于所述衬底与所述第一外延层中,

142、所述纵向连接区自所述第二外延层表面延伸至所述第一埋层中,

143、所述维持电压提升模块为第三电阻与第二二极管,所述纵向连接区构成所述第三电阻,所述第一埋层和所述衬底构成所述第二二极管,

144、其中,所述纵向连接区与所述第一埋层为第二掺杂类型。

145、可选地,所述第三电阻的一端连接所述第二晶体管的发射极,另一端连接所述第二二极管的阴极,所述第二二极管的阳极连接所述第二电位。

146、可选地,所述第二二极管为稳压二极管。

147、可选地,还包括形成第二埋层与第三埋层,

148、所述第二埋层位于所述第一外延层中,

149、所述第三埋层位于所述第一外延层与所述第二外延层交界处并位于所述第一外延层与所述第二外延层中,所述第三埋层位于所述第二埋层上并与所述第二埋层接触,

150、所述纵向连接区自所述第二外延层的表面延伸至所述第三埋层中,

151、所述维持电压提升模块为第三电阻与第三晶体管,所述纵向连接区构成所述第三电阻,所述纵向连接区、所述第三埋层和所述第二埋层构成所述第三晶体管,

152、其中,所述纵向连接区与所述第二埋层为第一掺杂类型,所述第三埋层为第二掺杂类型。

153、可选地,所述第三晶体管为pnp三极管。

154、可选地,所述第三电阻的一端连接所述第二晶体管的发射极,另一端连接所述第三晶体管的发射极,所述第三晶体管的集电极连接所述第二电位,所述第三晶体管的基极悬空。

155、可选地,还包括形成第二隔离结构,所述第二隔离结构自所述第二外延层的表面延伸至所述衬底中,

156、其中,所述纵向连接区位于所述第一隔离结构与所述第二隔离结构之间。

157、可选地,所述第一晶体管、所述第二晶体管和所述第一电阻用于构成可控硅整流器结构,

158、所述可控硅整流器结构包括至少一个可控硅整流器单元,每个所述可控硅整流器单元包括所述第一阱区、所述第二阱区、所述第一掺杂区、所述第二掺杂区、所述第三掺杂区和所述第四掺杂区,

159、所述第一隔离结构环绕所有的所述可控硅整流器单元,所述纵向连接区位于所述第一隔离结构外侧。

160、可选地,所述可控硅整流器结构仅包括一个可控硅整流器单元,所述第二阱区环绕所述第一阱区,所述第一隔离结构环绕所述第二阱区,所述纵向连接区环绕所述第一隔离结构;

161、所述第二掺杂区、所述第三掺杂区、所述第四掺杂区依次环绕所述第一掺杂区;

162、或者,所述第二掺杂区、所述第四掺杂区、所述第三掺杂区依次环绕所述第一掺杂区。

163、可选地,所述可控硅整流器结构包括多个可控硅整流器单元,多个可控硅整流器单元并联,在每个所述可控硅整流器单元中,所述第一阱区与所述第二阱区沿所述第一方向交替分布,

164、所述第一阱区、所述第二阱区、所述第一掺杂区、所述第二掺杂区、所述第三掺杂区和所述第四掺杂区沿第二方向延伸,所述第一方向和所述第二方向垂直。

165、可选地,所述可控硅整流器结构包括多个可控硅整流器单元,多个可控硅整流器单元并联,在每个所述可控硅整流器单元中,所述第二阱区环绕所述第一阱区,所述第二掺杂区、所述第三掺杂区、所述第四掺杂区依次环绕所述第一掺杂区;或者,所述第二掺杂区、所述第四掺杂区、所述第三掺杂区依次环绕所述第一掺杂区;

166、所述多个可控硅整流器单元呈阵列分布。

167、可选地,还包括形成第三隔离结构,所述第三隔离结构自所述第二外延层的表面延伸至所述衬底中,所述第三隔离结构位于所述第一掺杂区和所述第二掺杂区之间并环绕所述第一掺杂区,以分隔所述可控硅整流器结构、所述维持电压提升模块的路径和所述第一二极管、所述第二电阻的路径。

168、可选地,还包括在所述第二外延层中的所述第一阱区和所述第二阱区之间形成第五掺杂区,所述第五掺杂区分别与所述第一阱区和所述第二阱区连接,

169、其中,所述第二外延层、所述第一阱区、所述第二阱区以及所述第五掺杂区构成第三二极管,

170、所述第五掺杂区用于降低所述静电防护器件的触发电压,所述第三二极管构成触发电压降低模块。

171、可选地,所述第五掺杂区的数量为多个,且分隔设置。

172、可选地,所述第三二极管的阴极连接所述第二晶体管的集电极,所述第三二极管的阳极连接所述第二晶体管的发射极。

173、可选地,所述第三二极管为稳压二极管。

174、可选地,还包括:

175、在所述第二外延层中形成第三阱区,且所述第三阱区位于所述第一阱区和所述第二阱区之间;

176、在所述第三阱区中形成第六掺杂区与第七掺杂区;

177、在所述第二阱区中形成第八掺杂区;以及

178、在所述隔离层上形成第三导电层,所述第三导电层通过连接柱电连接所述第七掺杂区与所述第八掺杂区,

179、所述第二导电层还通过连接柱与所述第六掺杂区电连接,

180、其中,所述第三阱区与所述第八掺杂区为第一掺杂类型,所述第六掺杂区与所述第七掺杂区为第二掺杂类型,

181、所述第三阱区、所述第六掺杂区和所述第七掺杂区构成第四晶体管,用于降低所述静电防护器件的触发电压,所述第四晶体管构成触发电压降低模块。

182、可选地,所述第四晶体管为npn三极管。

183、可选地,所述第四晶体管的集电极连接所述第二晶体管的集电极,

184、所述第四晶体管的发射极连接所述第二晶体管的基极,

185、所述第四晶体管的基极悬空,

186、其中,所述第一晶体管的发射极还连接所述第二晶体管的集电极。

187、可选地,所述静电防护器件的维持电压的范围为3~37v。

188、可选地,所述静电防护器件为单向静电防护器件,所述制造方法还包括形成背面电极,所述背面电极位于所述衬底远离所述第一外延层的一侧。

189、上述技术方案中的一个技术方案具有如下有益效果:

190、通过将可控硅整流器结构与维持电压提升模块串联,当第一电位大于第二电位时,第一二极管和第二电阻所在的路径反向截止,可控硅整流器结构以及维持电压提升模块所在的路径被导通,从而释放静电,其中,通过设置维持电压提升模块使得静电防护电路的维持电压可以高于被保护的电路的工作电压,从而将该静电防护电路适用于不同电源电路的esd防护。

191、在一些实施例中,维持电压提升模块为纵向连接区构成的第三电阻,将控制静电防护电路的维持电压转换为控制第三电阻的电阻值,具体地,通过调节纵向连接区的材料或掺杂浓度,从而控制第三电阻两端的电阻值,进而控制电流流过时第三电阻两端的压降。

192、在一些实施例中,维持电压提升模块为纵向连接区与衬底构成的第三电阻与第二二极管,将控制静电防护电路的维持电压转换为控制第二二极管的击穿电压,具体的,通过调节纵向连接区的掺杂浓度与退火条件从而调控第二二极管的击穿电压。

193、在一些实施例中,维持电压提升模块为纵向连接区、第一埋层和衬底构成的第三电阻与第二二极管,将控制静电防护电路的维持电压转换为控制第二二极管的击穿电压,具体的,通过调节第一埋层的掺杂浓度与退火条件从而调控第二二极管的击穿电压。

194、在一些实施例中,维持电压提升模块为纵向连接区、第二埋层和第三埋层构成的第三电阻与第三晶体管,将控制静电防护电路的维持电压转换为控制第三晶体管的击穿电压,具体的,通过调节第二埋层与第三埋层的掺杂浓度与退火条件从而调控第三晶体管的击穿电压。

195、进一步地,通过设置触发电压降低模块,使得静电防护电路的触发电压位于设计的窗口范围内,再结合维持电压提升模块,解决了现有技术中静电防护电路的高触发电压、低维持电压的问题。

196、在一些实施例中,触发电压降低模块为第一阱区、第二阱区和第五掺杂区构成的第三二极管,将控制静电防护电路的触发电压转换为控制第二二极管的击穿电压,具体的,通过调节第五掺杂区的掺杂浓度与退火条件从而调控第三二极管的击穿电压。

197、在一些实施例中,触发电压降低模块为第三阱区、第六掺杂区和第七掺杂区构成的第四晶体管,将控制静电防护电路的触发电压转换为控制第四晶体管的击穿电压,具体的,通过调节第三阱区、第六掺杂区和第七掺杂区的掺杂浓度与退火条件从而调控第四晶体管的击穿电压。

198、由于维持电压提升模块(二极管、三极管或电阻)的电压可以在2~35v范围内调控,可控硅整流器结构的维持电压在1~2v,因此该静电防护器件的维持电压可以在3~37v范围内,适合绝大部分的应用场景。

199、进一步地,第二二极管与第三二极管均为稳压二极管,具有静电泄放能力强、浪涌防护能力优、稳压性能好的优点,但是有寄生电容比较大的缺点;可控硅整流器结构具有电流泄放效率高,自身抗静电能力强、静态漏电低、寄生电容小的优点,但是有触发电压高、维持电压低的缺点。本公开采用稳压二极管(第二二极管与第三二极管)与可控硅整流器结构集成到一起形成触发电压和维持电压均可单独调控的新型结构,规避了稳压二极管寄生电容大和可控硅整流器结构触发电压高、维持电压低的缺点。

200、进一步地,在一些实施例中,静电防护器件为对称结构,且第一掺杂区、第二掺杂区、第三掺杂区以及第四掺杂区均为圆环形,相比于条形设置导致中间区域电流密度过大而被烧毁,圆环形的设置使得静电防护器件中的电流、电场分布更均匀,有利于提升静电和浪涌能力。

201、进一步地,本公开实施例的静电防护器件为单向静电防护器件,适用于电源线路、usb和hdmi端口的静电防护。

202、此外,本公开实施例的静电防护器件为纵向结构,适合传统的小尺寸打线封装工艺。

本文地址:https://www.jishuxx.com/zhuanli/20240905/288769.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表