一种互补型左右对称的双边自举开关及其工作方法

- 国知局

- 2024-09-11 14:41:12

本发明涉及一种互补型左右对称的双边自举开关及其工作方法,属于模拟集成电路。

背景技术:

1、为了降低mos开关导通电阻的非线性,常常采用栅压自举技术提高输入开关的线性度,减小失真,在模拟信号转换为数字信号的过程中,自举开关起着非常重要的作用,它可以周期性的采样模拟信号并保存,自举开关的线性度对其他模块的影响很大。沟道电荷注入、时钟馈通、采样电路存在寄生电容、导通电阻不固定都会影响自举开关的线性度,现有提高线性度的方法主要为优化尺寸,但其提升有限,进一步提升线性度就需要在结构上进行改善,为此,提出本发明。

技术实现思路

1、针对现有技术的不足,本发明提供一种互补型左右对称的双边自举开关,基于传统的自举开关,通过在关键的mos管上添加电路来增加关键mos管的栅源电压,减小寄生电容对采样管栅源电压的影响,然后对自举开关进行左右对称和上下互补对称,变为一种互补型左右对称的双边自举开关,左右对称的双边对称结构可以降低采样管子的栅源电压对输入信号的依赖,以此来增加自举开关的线性度,同时也可以降低采样管子体效应对采样线性度的影响,上下对称的互补型对称架构可以使nmos释放的电子和pmos释放的空穴结合,减小沟道电荷的注入效应,从而增加线性度,进行左右上下对称之后,自举开关的线性度得到明显的提升。

2、本发明还提供上述互补型左右对称的双边自举开关的工作方法。

3、本发明的技术方案如下:

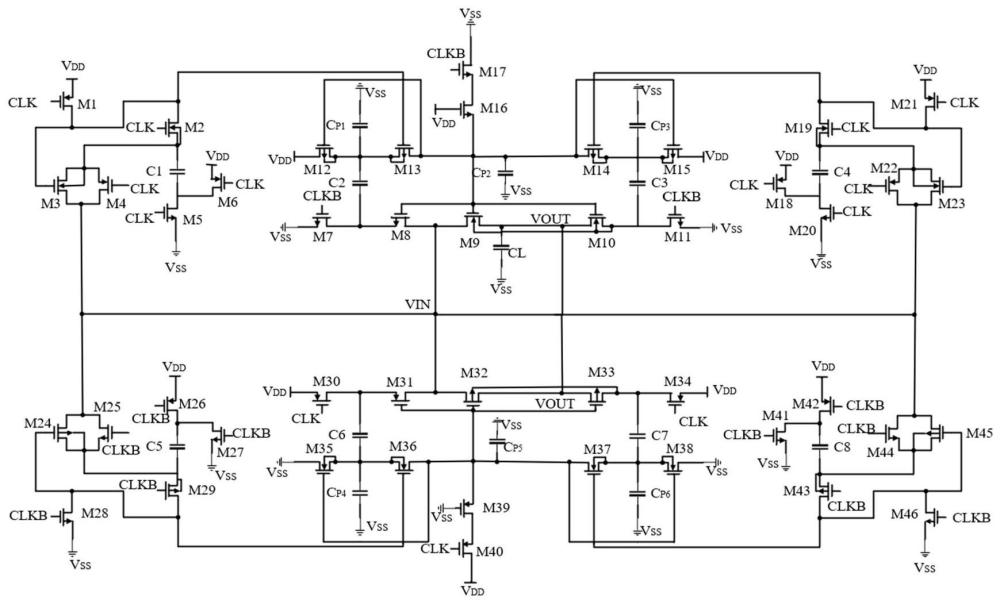

4、一种互补型左右对称的双边自举开关,包括上半部分电路和下半部分电路,上半部分电路由nmos采样,由clk和clkb提供两个相反的采样时钟,下半部分电路由pmos进行采样,由clk和clkb提供两个相反的采样时钟。

5、根据本发明优选的,上半部分电路包括23个mos管,分别为m1-m23,采样原理为nmos采样,其中,m2、m3、m5、m7、m8、m9、m10、m11、m16、m17、m19、m20、m23为nmos管,m1、m4、m6、m12、m13、m14、m15、m18、m21、m22为pmos管,电路连接关系为:

6、m1、m6、m12、m15、m18、m21的源极和m16的栅极分别接vdd,m5、m7、m11、m20的源极和m17的漏极分别接vss,m1、m2、m4、m5、m6、m18、m19、m20、m21、m22的栅极分别接采样时钟clk,m7、m11、m17的栅极分别接采样时钟clkb,m4、m8、m22的漏极和m3、m9、m23的源极分别接输入信号vin,m9的漏极和m10的源极分别接输出信号vout;

7、m1漏极分别连接有m3的栅极、m2的漏极和m13的栅极,m3的漏极分别连接有m4的源极和m2的源极,m5的漏极连接有m6的漏极,m12的栅极分别连接有m13的漏极、m16的源极、m14的源极和m19的栅极,m12的漏极连接有m13的源极,m7的漏极连接有m8的源极,m16的漏极连接有m17的源极,上半部分电路的右半部分连接方式与左半部分完全对称,具体的连接方式为:m21漏极分别连接有m23的栅极、m19的漏极和m14的栅极,m23的漏极分别连接有m22的源极和m19的源极,m20的漏极连接有m18的漏极,m15的栅极连接有m14的漏极,m15的漏极连接有m14的源极,m11的漏极连接有m10的源极,m3、m12、m15、m19、m23的衬底和分别和对应的漏极连接(如m3的衬底和m3的漏极连接),m2、m13、m14的衬底分别和对应的源极连接,m9的衬底分别连接m10的衬底和m10的漏极,其余nmos管衬底接地vss,pmos管衬底接电源电压vdd;

8、电容cp1、cp2、cp3是对地的寄生电容,电容c1上极板接m2的源极,下极板接m5的漏极;电容c2的上极板接m12的漏极,下极板接m7的漏极;电容c3的上极板接m15的漏极,下极板接m11的漏极;电容c4上极板接m19的源极,下极板接m20的漏极。

9、m7-m17为自举开关的主体结构,nmos管m9为采样管子,m13和m14为关键的采样管子,m1-m6用于将m13的栅源电压增加为两倍的vdd,m18-m23用于将m14的栅源电压增加到两倍的vdd,电容c1、c2用于控制采样管m19的栅源电压,cp1、cp2、cp3为关键结点的寄生电容。

10、根据本发明优选的,下半部分电路包括23个mos管,分别为m24-m46,采样原理为pmos采样。其中m25、m27、m28、m35、m36、m37、m38、m41、m44、m46为nmos管,m24、m26、m29、m30、m31、m32、m33、m34、m39、m40、m42、m43、m45为pmos管,电路连接关系为:

11、m26、m30、m34、m40、m42的源极分别连接有vdd,m28、m27、m35、m38、m41、m46的源极和m39的栅极分别连接有vss,m25、m26、m27、m28、m29、m41、m42、m43、m44、m46的栅极分别连接有采样时钟clkb,m30、m34、m40的栅极分别连接有采样时钟clk,m25、m31、m44的漏极和m24、m32、m45的源极分别连接有输入信号vin,m32的漏极和m33的源极分别连接有输出信号vout;

12、m28漏极分别连接有m24的栅极、m29的漏极和m36的栅极,m24的漏极分别连接有m25源极和m29的源极,m26的漏极连接有m27的漏极,m35的栅极分别连接有m36的漏极、m39的源极、m37的源极和m32的栅极,m35的漏极连接有m36的源极,m30的漏极连接有m31的源极,m39的漏极连接有m40的源极,下半部分电路的右半部分的连接方式与左半部分完全对称,具体的连接方式为:m46漏极分别连接有m45的栅极、m43的漏极和m37的栅极,m45的漏极分别连接有m44的源极和m43的源极,m42的漏极连接有m41的漏极,m38的栅极连接有m37的漏极,m38的漏极连接有m37的源极,m34的漏极连接有m33的源极;

13、m24、m35、m38、m45的衬底分别和对应的漏极连接,m29、m29、m36、m37、m43的衬底分别和对应的源极连接,m32的衬底分别连接m33的衬底和m33的漏极,其余nmos管衬底接地vss,pmos衬底接电源电压vdd;

14、cp4、cp5、cp6是对地的寄生电容,电容c5上极板接m29的源极,下极板接m26的漏极;电容c6的上极板接m30的漏极,下极板接m35的漏极;电容c7的上极板接m34的漏极,下极板接m38的漏极;电容c8上极板接m43的源极,下极板接m42的漏极。

15、m30-m40为自举开关的主体结构,pmos管m32为采样管子,m36和m37为关键的采样管子,m24-m29用于将m36的栅源电压增加为两倍的vdd,m41-m46用于将m37的栅源电压增加到两倍的vdd,电容c3、c4用于控制采样管m32的栅源电压,cp4、cp5、cp6为关键结点的寄生电容。

16、上述互补型左右对称的双边自举开关的工作方法,包括保持阶段和采样阶段,具体步骤如下:

17、(1)保持阶段:clk为低电平,clkb为高电平,各个mos管的状态为:mos管m1、m3、m4、m6、m7、m11、m12、m15、m16、m17、m18、m21、m22、m23、m24、m25、m27、m28、m30、m34、m35、m38、m39、m40、m41、m44、m45、m46导通,mos管m2、m5、m8、m9、m10、m13、m14、m19、m20、m26、m29、m31、m32、m33、m36、m37、m42、m43截止;

18、c1上极板电位为vin,下极板电位为vdd;c2上极板电位为vdd,下极板电位为vss;c3上极板电位为vdd,下极板电位为vss;c4上极板电位为vin,下极板电位为vdd;c5上极板电位为vin,下极板电位为vss;c6上极板电位为vdd,下极板电位为vss;c7上极板电位为vdd,下极板电位为vss;c8上极板电位为vin,下极板电位为vss;

19、(2)采样阶段:clk为高电平,clkb为低电平,各个mos管的状态为:mos管m2、m5、m8、m9、m10、m13、m14、m19、m20、m26、m29、m31、m32、m33、m36、m37、m42、m43导通,mos管m1、m3、m4、m6、m7、m11、m12、m15、m16、m17、m18、m21、m22、m23、m24、m25、m27、m28、m30、m34、m35、m38、m39、m40、m41、m44、m45、m46截止;

20、c1上极板电位为vin-vdd,下极板电位为vss;c2上极板电位为vin+vdd,下极板电位为vin;c3上极板电位为vin+vdd,下极板电位为vin;c4上极板电位为vin-vdd,下极板电位为vss;c5上极板电位为vin+vdd,下极板电位为vdd;c6上极板电位为vin,下极板电位为vin-vdd;c7上极板电位为vin,下极板电位为vin-vdd;c8上极板电位为vin+vdd,下极板电位为vdd,此时,m9的栅源电压vgs7=(vdd+vin)-vin=vdd,m32的栅源电压vsg20=vin(vin-vdd)=vdd,m13与m14的栅源电压相同,均为vsg2=(vin+vdd)-(vin-vdd)=2vdd,m36和m37的栅源电压相同,均为vgs15=(vin+vdd)-(vin-vdd)=2vdd,关键寄生节点的mos晶体管具有较高的栅源电压。

21、工作原理:自举开关的主要作用是在一定的周期内,按照设定的模式控制采样电容的充放电过程。具体来说,采样开关负责在两个连续的信号之间切换,使得采样电容能够在某一瞬间捕捉并存储信号的瞬时值。这样做的目的是将连续的模拟信号转换为离散的数据点,以便后续的处理和分析。采样阶段结束后主采样管m9、m32的漏极电压为采样结束时刻与输入信号vin相同的输出电压vout,采样结束时将时域连续、幅度域连续的模拟输入信号vin变为离散化的数据点vout,便于后续的处理与分析。

22、本发明的有益效果在于:

23、1、本发明在关键的mos管上加上部分电路来增加关键mos管的栅源电压,以减小寄生电容对采样管栅源电压的影响,左右对称的双边对称结构可以减低采样管子的栅源电压对输入信号的依赖,以此来增加自举开关的线性度,同时也可以降低采样管子体效应对采样线性度的影响。

24、2、本发明上下对称的互补型对称架构可以使nmos释放的电子和pmos释放的空穴结合,减小沟道电荷的注入效应,从而增加线性度。

本文地址:https://www.jishuxx.com/zhuanli/20240911/291825.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表