一种横向变掺杂体二极管的SiCVDMOSFET器件的制作方法

- 国知局

- 2024-09-14 14:35:53

本发明涉及mos半导体,更具体的说是一种横向变掺杂体二极管的sicvdmosfet器件。

背景技术:

1、在大功率变流器应用中,垂直双扩散场效应晶体管开关器件需要一个续流二极管在vdmosfet关断时提供电流通路。特别在硬开关应用中,通常采用vdmosfet和二极管反向并联的拓扑结构,例如同步buck直流变换器和逆变器,这种拓扑在续流期间主要由vdmosfet反向导通提供续流通路,而二极管在死区时间续流。二极管从续流时的导通状态到关断状态会经历反向恢复过程,如果反向恢复特性较差,不仅会影响器件的开关特性,而且开关功耗增加、电路效率下降,而且可能产生较大的反向尖峰电流损害器件的可靠性。

2、现有专利公开了一种横向变掺杂体二极管的sic vdmosfet器件(公开号cn115632069a),包括:由下至上依次设置的漏极、n+衬底和n-漂移区;n-漂移区的两侧部上分别具有p阱区;p阱区的内部具有n+有源区;p阱区朝外的侧面表面上形成第一p+接触区;第一p+接触区背向n+有源区的侧面上形成有p-接触区;p-接触区背向第一p+接触区的侧面上形成第二p+接触区。该专利所公开技术中,横向的p阱层采用p+、p-、p+顺序排布设计,会造成由于p+区与源极的直接接触,并因受到源极、漏极之间电势影响形成寄生电荷,进而影响该mos半导体的开关响应速度。并且相邻的mos元胞之间,也会因为电势的相互影响,会出现扩散层的电荷向相邻mos元胞扩散。

技术实现思路

1、本发明主要解决的技术问题是提供一种横向变掺杂体二极管的sic vdmosfet器件,解决了上述背景技术中的问题。

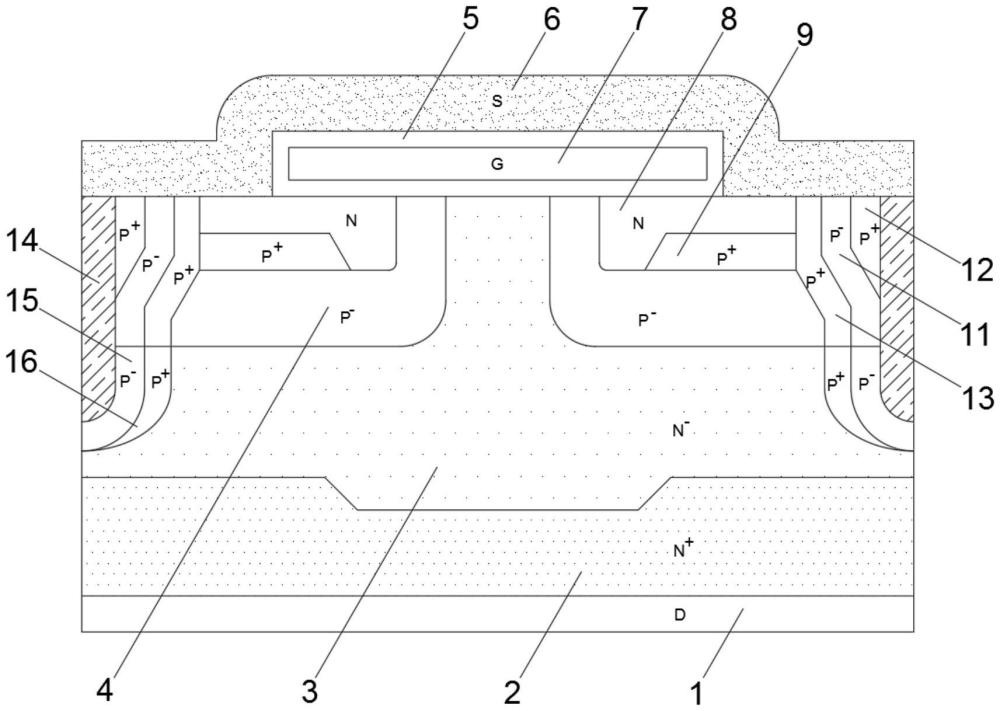

2、为解决上述技术问题,根据本发明的一个方面,更具体的说是一种横向变掺杂体二极管的sic vdmosfet器件,包括多个水平排列并前后延伸的mos元胞结构,所述mos元胞包括衬底层、扩散层、p体区、掺杂n体区以及位于两侧横向变掺杂的p阱层,所述沉底层的下层包括有漏极;

3、所述p体区包括低掺杂p阱层一、高掺杂p阱层一、高掺杂p阱层二、低掺杂p阱层二、高掺杂p阱层三、低掺杂p阱层三以及高掺杂p阱层四;

4、所述mos元胞上淀积有金属源极,其中掺杂n体区、p阱层均与金属源极欧姆接触;

5、所述金属源极的内部嵌设有栅极,所述栅极的外表面包裹有栅氧化层。

6、更进一步的,单个所述mos元胞中的沉底层两侧通过较高浓度的离子注入形成两侧高中间低洼的形状;

7、所述衬底层的中间低洼区设计以增大衬底层与栅极之间的最小间距,并且衬底层两侧较高区域与栅极的腰部形成两个有倾斜角的最小间距。

8、更进一步的,所述低掺杂p阱层一通过离子注入1.8×1016mol/cm3的硼元素,以增加所述低掺杂p阱层一中电荷载流子的浓度。

9、更进一步的,所述掺杂n体区通过离子注入2.3×1018mol/cm3的磷元素。

10、更进一步的,所述栅极与漏极之间接入电压状态下,所述衬底层的正电荷在扩散层内沿两侧最小距离向栅极腰部靠拢,并在所述低掺杂p阱层一内靠近栅极位置处形成电荷沟道。

11、更进一步的,所述低掺杂p阱层二通过在所述高掺杂p阱层二与高掺杂p阱层三之间进行离子注入0.8×1016mol/cm3的硼元素形成。

12、更进一步的,所述相邻所述mos元胞之间的低掺杂p阱层三共为一体,其低掺杂p阱层三结构抑制单颗mos元胞中的电荷向相邻mos元胞中漂移。

13、更进一步的,相邻所述mos元胞之间共设有低掺杂n型材料,其中低掺杂n型材料主要由氮化硅si3n4构成。

14、本发明一种横向变掺杂体二极管的sic vdmosfet器件的有益效果为:

15、1、本发明通过在单颗mos元胞的侧边形成横向变掺杂的p阱层,该设计降低了续流期间注入漂移区的电荷浓度,即加快反向恢复过程中电荷空穴被扫出漂移区的速度,从而解决sicvdmosfet寄生体二极管反向恢复特性较差带来的开关功耗增加、器件可靠性下降的问题。

16、2、本发明通过将衬底层两侧离子注入高浓度元素以形成两侧高中心低的形状,这样可以将衬底层至栅极腰部的最小路径拆分成左右两个,这样既可以增大栅极与漏极之间的承压能力,同时减少对mos半导体电荷导通率的影响。

技术特征:1.一种横向变掺杂体二极管的sic vdmosfet器件,其特征在于,包括多个水平排列并前后延伸的mos元胞结构,所述mos元胞包括衬底层(2)、扩散层(3)、p体区、掺杂n体区(8)以及位于两侧横向变掺杂的p阱层,所述沉底层(2)的下层包括有漏极(1);

2.根据权利要求1所述的横向变掺杂体二极管的sic vdmosfet器件,其特征在于:单个所述mos元胞中的沉底层(2)两侧通过较高浓度的离子注入形成两侧高中间低洼的形状;

3.根据权利要求1所述的横向变掺杂体二极管的sic vdmosfet器件,其特征在于:所述低掺杂p阱层一(4)通过离子注入1.8×1016mol/cm3的硼元素,以增加所述低掺杂p阱层一(4)中电荷载流子的浓度。

4.根据权利要求3所述的横向变掺杂体二极管的sic vdmosfet器件,其特征在于:所述掺杂n体区(8)通过离子注入2.3×1018mol/cm3的磷元素。

5.根据权利要求4所述的横向变掺杂体二极管的sic vdmosfet器件,其特征在于:所述栅极(7)与漏极(1)之间接入电压状态下,所述衬底层(2)的正电荷在扩散层(3)内沿两侧最小距离向栅极(7)腰部靠拢,并在所述低掺杂p阱层一(9)内靠近栅极(7)位置处形成电荷沟道(17)。

6.根据权利要求1所述的横向变掺杂体二极管的sic vdmosfet器件,其特征在于:所述低掺杂p阱层二(11)通过在所述高掺杂p阱层二(12)与高掺杂p阱层三(13)之间进行离子注入0.8×1016mol/cm3的硼元素形成。

7.根据权利要求6所述的横向变掺杂体二极管的sic vdmosfet器件,其特征在于:所述相邻所述mos元胞之间的低掺杂p阱层三(15)共为一体,其低掺杂p阱层三(15)结构抑制单颗mos元胞中的电荷向相邻mos元胞中漂移。

8.根据权利要求7所述的横向变掺杂体二极管的sic vdmosfet器件,其特征在于:相邻所述mos元胞之间共设有低掺杂n型材料(14),其中低掺杂n型材料(14)主要由氮化硅(si3n4)构成。

技术总结本发明涉及MOS半导体技术领域,且公开了一种横向变掺杂体二极管的SiC VDMOSFET器件,包括多个水平排列并前后延伸的MOS元胞结构,所述MOS元胞包括衬底层、扩散层、P体区、掺杂N体区以及位于两侧横向变掺杂的P阱层,所述沉底层的下层包括有漏极;所述P体区包括低掺杂P阱层一、高掺杂P阱层一、高掺杂P阱层二、低掺杂P阱层二、高掺杂P阱层三、低掺杂P阱层三以及高掺杂P阱层四。本发明通过在单颗MOS元胞的侧边形成横向变掺杂的P阱层,该设计降低了续流期间注入漂移区的电荷浓度,即加快反向恢复过程中电荷空穴被扫出漂移区的速度,从而解决SiCVDMOSFET寄生体二极管反向恢复特性较差带来的开关功耗增加、器件可靠性下降的问题。技术研发人员:许一力受保护的技术使用者:北京清芯微储能科技有限公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/294981.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表