芯片组件及电子设备的制作方法

- 国知局

- 2024-09-14 14:49:36

本申请涉及半导体,尤其涉及一种芯片组件及电子设备。

背景技术:

1、随着芯片性能需求的不断提升,芯片技术不断往先进工艺演进。即使如此,仍然面临单片面积太大导致无法实现等问题。为了解决该问题,本领域技术人员采用将芯片分成多个较小的裸芯片(die),代替单一的单片设计的方案。以处理器芯片为例,将处理器芯片分成处理器裸芯片和输入输出接口裸芯片,以获得高性能的处理器芯片。

2、芯粒(chiplet)技术,是一种应用较多的、用来代替单一的单片设计的技术。但是如何让裸芯片与裸芯片之间高速互连,是chiplet技术的一大全新挑战。

技术实现思路

1、本申请实施例提供一种芯片组件及电子设备,用于实现芯片组件中裸芯片与裸芯片的高速互连。

2、为达到上述目的,本申请采用如下技术方案:

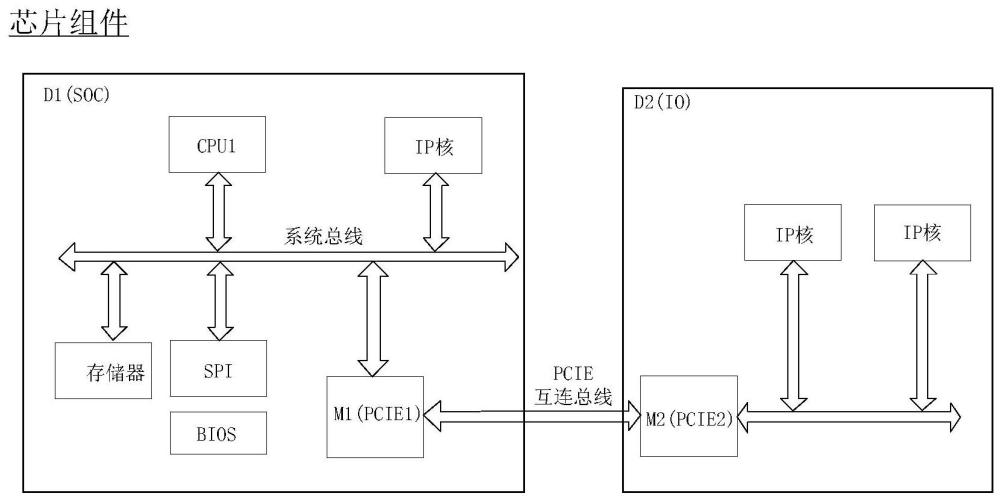

3、本申请实施例的第一方面,提供一种芯片组件包括:第一裸芯片和第二裸芯片,第一裸芯片包括第一处理器、基本输入输出系统和第一高速接口;第二裸芯片包括第二高速接口;第二高速接口用于与第一高速接口连接,第二高速接口和第一高速接口为同种类型的接口。

4、本申请实施例提供的芯片组件中的第一裸芯片包括第一高速接口,第二裸芯片包括第二高速接口,第一裸芯片和第二裸芯片通过高速互连协议互连,以实现第一裸芯片和第二裸芯片之间的高速互连。另外,第一高速接口和第二高速接口均为标准高速接口,当将第一裸芯片和第二裸芯片封装后,封装后的第一芯片和第二芯片依旧可以用第一高速接口和第二高速接口连接。因此,本申请实施例提供的第一裸芯片和第二裸芯片之间的互连方式适用于各种应用场景下,可以基于该方案构筑出不同的产品形态。而且,当芯片组件与其他芯片连接时,也可以采用同种类型的高速接口进行互连,以减少应用芯片组件的电子设备中所需的协议框架的种类,降低成本。

5、在一种可能的实现方式中,芯片组件还包括存储器,第一裸芯片与存储器连通,存储器设置在第二裸芯片外。第一裸芯片所需的部分或者全部存储空间由存储器提供,存储器没有设置在第一裸芯片内,因此,第一裸芯片和第二裸芯片通过第一高速接口和第二高速接口互连时,无需考虑访问存储器时的带宽需求,可以降低对第一高速接口和第二高速接口的带宽要求。

6、在一种可能的实现方式中,存储器用于存储第一裸芯片启动所需的数据。启动所需的数据无需从第二裸芯片调取,可以降低第一裸芯片对第二裸芯片的依赖。

7、在一种可能的实现方式中,存储器设置在第一裸芯片内。通过将存储器设置在第一裸芯片内,相当于将大带宽吞吐需求的接口设置在第一裸芯片内,无需设置第一裸芯片外接的大带宽吞吐需求的接口,简化结构、降低要求。另外,将存储器设置在第一裸芯片内,可以减少对其他芯片的依赖。

8、在一种可能的实现方式中,第一裸芯片还包括显示接口。将低延时需求的接口设置在第一裸芯片上,可以提高芯片组件的性能。

9、在一种可能的实现方式中,第二裸芯片内设置有第二处理器。芯片组件可以为双处理器系统。

10、在一种可能的实现方式中,第二裸芯片为输入输出接口裸芯片。将芯片组件中的处理器部分和接口部分解耦,第一裸芯片和第二裸芯片可以分开演进,既能打破性能提升限制,减少产品开发时间,又能降低开发成本,还有助于保证量产良率,以降低产品演进的风险和成本,支持重复使用。

11、在一种可能的实现方式中,第一裸芯片为片上系统裸芯片。这是一种技术成熟的方案。

12、在一种可能的实现方式中,第一裸芯片和第二裸芯片设置在同一封装基板上。这是一种chiplet技术的应用场景。

13、在一种可能的实现方式中,第一裸芯片和第二裸芯片均设置在主板上。这是一种板级连接的应用场景。

14、在一种可能的实现方式中,第一裸芯片设置在主板上,第二裸芯片设置在扩展坞上。这是一种设备级连接的应用场景。

15、在一种可能的实现方式中,第一高速接口为移动产业处理器接口、通用串行总线接口或者外围部件互连标准接口。这是一种技术成熟的方案。

16、在一种可能的实现方式中,第一高速接口和第二高速接口通过走线连接。这是一种技术成熟的方案。

17、本申请实施例的第二方面,提供一种电子设备,包括芯片组件和外接接口,芯片组件和外接接口耦接;芯片组件包括第一方面任一项的芯片组件。

18、本申请实施例第二方面提供的电子设备包括第一方面的芯片组件,其有益效果与芯片组件的有益效果相同,此处不再赘述。

19、在一种可能的实现方式中,电子设备还包括输入输出接口芯片,输入输出接口芯片包括第三高速接口;芯片组件还包括第四高速接口,第四高速接口用于与第三高速接口连接;第四高速接口、第三高速接口以及第一高速接口为同种类型的接口。芯片组件内部互连选取的高速互联协议,和芯片组件与外部芯片互联选取的互联协议可以为同种类型的协议,以减小协议类型。

技术特征:1.一种芯片组件,其特征在于,包括:

2.根据权利要求1所述的芯片组件,其特征在于,所述芯片组件还包括存储器,所述第一裸芯片与所述存储器连通,所述存储器设置在所述第二裸芯片外。

3.根据权利要求2所述的芯片组件,其特征在于,所述存储器用于存储所述第一裸芯片启动所需的数据。

4.根据权利要求2或3所述的芯片组件,其特征在于,所述存储器设置在所述第一裸芯片内。

5.根据权利要求1-4任一项所述的芯片组件,其特征在于,所述第一裸芯片还包括显示接口。

6.根据权利要求1-5任一项所述的芯片组件,其特征在于,所述第二裸芯片内设置有第二处理器。

7.根据权利要求1-5任一项所述的芯片组件,其特征在于,所述第二裸芯片为输入输出接口裸芯片。

8.根据权利要求1-7任一项所述的芯片组件,其特征在于,所述第一裸芯片为片上系统裸芯片。

9.根据权利要求1-8任一项所述的芯片组件,其特征在于,所述第一裸芯片和所述第二裸芯片设置在同一封装基板上。

10.根据权利要求1-8任一项所述的芯片组件,其特征在于,所述第一裸芯片和所述第二裸芯片均设置在主板上。

11.根据权利要求1-8任一项所述的芯片组件,其特征在于,所述第一裸芯片设置在主板上,所述第二裸芯片设置在扩展坞上。

12.根据权利要求1-11任一项所述的芯片组件,其特征在于,所述第一高速接口为移动产业处理器接口、通用串行总线接口或者外围部件互连标准接口。

13.根据权利要求1-12任一项所述的芯片组件,其特征在于,所述第一高速接口和所述第二高速接口通过走线连接。

14.一种电子设备,其特征在于,包括芯片组件和外接接口,所述芯片组件和所述外接接口耦接;所述芯片组件包括权利要求1-13任一项所述的芯片组件。

15.根据权利要求14所述的电子设备,其特征在于,所述电子设备还包括输入输出接口芯片,所述输入输出接口芯片包括第三高速接口;

技术总结本申请实施例提供一种芯片组件及电子设备,涉及半导体技术领域,用于实现芯片组件中裸芯片与裸芯片的高速互连。芯片组件包括:第一裸芯片和第二裸芯片,第一裸芯片包括第一处理器、基本输入输出系统和第一高速接口;第二裸芯片包括第二高速接口;第二高速接口用于与第一高速接口连接,第二高速接口和第一高速接口为同种类型的接口。芯片组件可以作为处理器系统应用。技术研发人员:谭丽娟,史舒娟受保护的技术使用者:华为技术有限公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/296068.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表