用于全长数论变换的硬件加速方法、装置及安全芯片与流程

- 国知局

- 2024-09-14 14:40:47

本发明涉及隐私计算中的数论变换,尤其涉及一种用于全长数论变换的硬件加速方法、用于全长数论变换的硬件加速装置及安全芯片。

背景技术:

1、隐私计算的众多方案中都经常使用环上多项式乘法,而以朴素的卷积方式去计算多项式乘法将会带来巨大的计算开销,因此大部分情况下都是使用ntt (numbertheoretic transforms,数论变换)辅助计算多项式乘法,为了追求更高的计算效率,也出现了计算ntt的专用加速器。

2、ntt的软件实现和硬件实现各有优劣,一般来说硬件加速器相较于软件实现能够提高处理效率,减少处理器开销,但是其灵活性较差。具体来说,在不同的隐私计算方案中,需要进行ntt变换的序列的长度不尽相同,如果ntt硬件加速器配置的可执行项数过大,虽然能够覆盖尽可能多的使用场景,但其能否实现是一个未知数,因为在时序与资源消耗上可能会出现问题。

3、因此,如何能够在现有ntt硬件加速器配置的可执行项数不变的情况下尽可能实现更长序列的ntt变换成为本领域技术人员亟待解决的技术问题。

技术实现思路

1、本发明提供了一种用于全长数论变换的硬件加速方法、用于全长数论变换的硬件加速装置及安全芯片,解决相关技术中存在的ntt变换序列的长度由于受限于当前ntt硬件加速器的配置无法实现更长序列的ntt变换的问题。

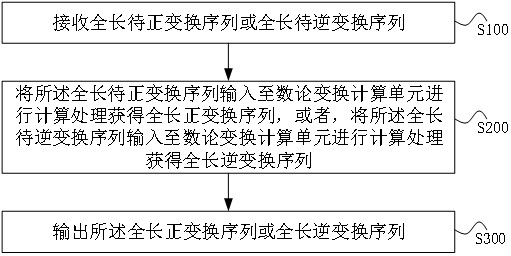

2、作为本发明的第一个方面,提供一种用于全长数论变换的硬件加速方法,其中,包括:

3、接收全长待正变换序列或全长待逆变换序列;

4、将所述全长待正变换序列输入至数论变换计算单元进行计算处理获得全长正变换序列,或者,将所述全长待逆变换序列输入至数论变换计算单元进行计算处理获得全长逆变换序列,其中所述数论变换计算单元能够对所述全长待正变换序列进行预处理后获得半长正变换待加速序列,以及能够将所述半长正变换待加速序列通过半长硬件加速器进行加速计算获得全长正变换序列,或者,所述数论变换计算单元能够对所述全长待逆变换序列进行预处理后获得半长逆变换待加速序列,以及能够将所述半长逆变换待加速序列通过半长硬件加速器进行加速计算获得全长逆变换序列;所述半长正变换待加速序列的序列长度为所述全长待正变换序列的序列长度的一半,所述半长逆变换待加速序列的序列长度为所述全长待逆变换序列的序列长度的一半;

5、输出所述全长正变换序列或全长逆变换序列。

6、进一步地,所述数论变换计算单元包括dit计算单元,所述数论变换计算单元能够对所述全长待正变换序列进行预处理后获得半长正变换待加速序列,以及能够将所述半长正变换待加速序列通过半长硬件加速器进行加速计算获得全长正变换序列,或者,所述数论变换计算单元能够对所述全长待逆变换序列进行预处理后获得半长逆变换待加速序列,以及能够将所述半长逆变换待加速序列通过半长硬件加速器进行加速计算获得全长逆变换序列,包括:

7、对所述全长待正变换序列进行逆序重排处理获得全长待正变换逆序重排序列,或者,对所述全长待逆变换序列进行逆序重排处理获得全长待逆变换逆序重排序列;

8、将所述全长待正变换逆序重排序列划分为两个半长待正变换逆序重排序列,或者,将所述全长待逆变换逆序重排序列划分为两个半长待逆变换逆序重排序列;

9、将两个半长待正变换逆序重排序列通过半长硬件加速器进行加速计算获得全长正变换序列,或者,将两个半长待逆变换逆序重排序列通过半长硬件加速器进行加速计算获得全长逆变换序列。

10、进一步地,所述全长正变换序列的表达式为:

11、,

12、,

13、其中,表示全长正变换序列,n表示序列长度为半长,和均表示半长待正变换逆序重排序列经过半长硬件加速器后的正变换计算结果,表示半长硬件加速器的正变换计算参数,表示模数;

14、所述全长逆变换序列的表达式为:

15、,

16、,

17、其中,表示全长逆变换序列,n表示序列长度为半长,和均表示半长待逆变换逆序重排序列经过半长硬件加速器后的逆变换计算结果,表示半长硬件加速器的逆变换计算参数,表示模数。

18、进一步地,对所述全长待正变换序列进行逆序重排处理获得全长待正变换逆序重排序列,或者,对所述全长待逆变换序列进行逆序重排处理获得全长待逆变换逆序重排序列,包括:

19、对所述全长待正变换序列按照下标二进制进行逆序重排获得全长待正变换逆序重排序列,或者,对所述全长待逆变换序列按照下标二进制进行逆序重排获得全长待逆变换逆序重排序列。

20、进一步地,所述数论变换计算单元包括dif计算单元,所述数论变换计算单元能够对所述全长待正变换序列进行预处理后获得半长正变换待加速序列,以及能够将所述半长正变换待加速序列通过半长硬件加速器进行加速计算获得全长正变换序列,或者,所述数论变换计算单元能够对所述全长待逆变换序列进行预处理后获得半长逆变换待加速序列,以及能够将所述半长逆变换待加速序列通过半长硬件加速器进行加速计算获得全长逆变换序列,包括:

21、对全长待正变换序列进行拆分计算处理获得两个半长待正变换序列,或者,对全长待逆变换序列进行拆分计算处理获得两个半长待逆变换序列;

22、将两个半长待正变换序列通过半长硬件加速器进行加速计算获得两个半长正变换序列,或者,将两个半长待逆变换序列通过半长硬件加速器进行加速计算获得两个半长逆变换序列;

23、将两个半长正变换序列进行拼接并进行逆序重排后获得全长正变换序列,或者,将两个半长逆变换序列进行拼接并进行逆序重排后获得全长逆变换序列。

24、进一步地,两个半长待正变换序列的表达式分别表示为:

25、,

26、,

27、其中,表示一个半长待正变换序列,表示另一个半长待正变换序列,n表示序列长度为半长,和均表示全长待正变换序列,表示半长硬件加速器的正变换计算参数,表示模数;

28、两个半长待逆变换序列的表达式分别表示为:

29、,

30、,

31、其中,表示一个半长待逆变换序列,表示另一个半长待逆变换序列,n表示序列长度为半长,和均表示全长待逆变换序列,表示半长硬件加速器的逆变换计算参数,表示模数。

32、进一步地,将两个半长正变换序列进行拼接并进行逆序重排后获得全长正变换序列,或者,将两个半长逆变换序列进行拼接并进行逆序重排后获得全长逆变换序列,包括:

33、将两个半长正变换序列进行拼接,获得正变换拼接序列;

34、将所述正变换拼接序列按照下标二进制进行逆序重排,获得全长正变换序列;或者,

35、将两个半长逆变换序列进行拼接,获得逆变换拼接序列;

36、将所述逆变换拼接序列按照下标二进制进行逆序重排,获得全长逆变换序列。

37、进一步地,所述数论变换计算单元包括:第一存储器、第二存储器、第三存储器、第四存储器、二进制翻转器、第一半长硬件加速器、第二半长硬件加速器、多路选择器、乘法器和两路模乘计算单元;

38、当所述数论变换计算单元为dit计算单元时:

39、所述第一存储器用于存储全长待正变换序列或全长待逆变换序列;

40、所述二进制翻转器的输入端连接所述第一存储器的输出端,所述二进制翻转器用于对所述全长待正变换序列进行逆序重排处理获得全长待正变换逆序重排序列,或者,用于对所述全长待逆变换序列进行逆序重排处理获得全长待逆变换逆序重排序列;

41、所述第二存储器的输入端连接所述二进制翻转器的输出端,所述第二存储器用于存储所述全长待正变换逆序重排序列或全长待逆变换逆序重排序列;

42、所述第一半长硬件加速器的输入端和所述第二半长硬件加速器的输入端均与所述第二存储器的输出端连接,所述第一半长硬件加速器用于对一个半长待正变换逆序重排序列或者一个半长待逆变换逆序重排序列进行加速计算,所述第二半长硬件加速器用于对另一个半长待正变换逆序重排序列或者另一个半长待逆变换逆序重排序列进行加速计算;

43、所述第三存储器的输入端分别连接所述第一半长硬件加速器的输出端以及第二半长硬件加速器的输出端,所述第三存储器用于存储半长待正变换逆序重排序列经过半长硬件加速器后的正变换计算结果或半长待逆变换逆序重排序列经过半长硬件加速器后的逆变换计算结果;

44、所述乘法器的一个输入端连接所述第三存储器的输出端,所述乘法器的另一个输入端连接所述多路选择器的输出端,所述多路选择器的两个输入端分别用于输入半长硬件加速器的正变换计算参数和半长硬件加速器的逆变换计算参数;

45、当所述多路选择器选择输入半长硬件加速器的正变换计算参数时,所述乘法器用于将所述半长待正变换逆序重排序列经过半长硬件加速器后的正变换计算结果与所述半长硬件加速器的正变换计算参数进行乘法计算,获得半长正变换中间乘法计算结果;

46、当所述多路选择器选择输入半长硬件加速器的逆变换计算参数时,所述乘法器用于将所述半长待逆变换逆序重排序列经过半长硬件加速器后的逆变换计算结果与所述半长硬件加速器的逆变换计算参数进行乘法计算,获得半长逆变换中间乘法计算结果;

47、两路模乘计算单元用于分别根据两个半长正变换中间乘法计算结果进行模乘运算,获得全长正变换序列;或者,用于分别根据两个半长逆变换中间乘法计算结果进行模乘运算,获得全长逆变换序列;

48、所述第四存储器的输入端连接两路模乘计算单元的输出端,用于存储全长正变换序列或全长逆变换序列;

49、当所述数论变换计算单元为dif计算单元时:

50、所述第一存储器用于存储全长待正变换序列或全长待逆变换序列;

51、所述乘法器的一个输入端连接两路模乘计算单元的减法计算结果中间输出端,所述乘法器的另一个输入端连接所述多路选择器的输出端,所述多路选择器的两个输入端分别用于输入半长硬件加速器的正变换计算参数和半长硬件加速器的逆变换计算参数;

52、当所述多路选择器选择输入半长硬件加速器的正变换计算参数时,所述乘法器用于将全长待正变换序列的减法计算序列结果与所述半长硬件加速器的正变换计算参数进行计算,获得半长待正变换中间乘法计算结果;

53、当所述多路选择器选择输入半长硬件加速器的逆变换计算参数时,所述乘法器用于将全长待逆变换序列的减法计算序列结果与所述半长硬件加速器的逆变换计算参数进行计算,获得半长待逆变换中间乘法计算结果;

54、两路模乘计算单元中的一路模乘计算单元用于根据全长待正变换序列的加法序列计算结果进行模乘运算获得一个半长待正变换序列,或者用于根据全长待逆变换序列的加法序列计算结果进行模乘运算获得一个半长待逆变换序列;另一路模乘计算单元用于根据半长待正变换中间乘法计算结果进行模乘运算获得另一个半长待正变换序列,或者,用于根据半长待逆变换中间乘法计算结果进行模乘运算获得另一个半长待逆变换序列;

55、所述第二存储器用于存储两个半长待正变换序列或两个半长待逆变换序列;

56、所述第一半长硬件加速器的输入端和所述第二半长硬件加速器的输入端均与所述第二存储器的输出端连接,所述第一半长硬件加速器用于对一个半长待正变换序列进行加速计算获得一个半长正变换序列,或者,用于对一个半长待逆变换序列进行加速计算获得一个半长逆变换序列,所述第二半长硬件加速器用于对另一个半长待正变换序列进行加速计算获得一个半长正变换序列,或者,用于对另一个半长待逆变换序列进行加速计算获得一个半长逆变换序列;

57、所述第三存储器的输入端分别连接所述第一半长硬件加速器的输出端以及第二半长硬件加速器的输出端,所述第三存储器用于存储两个半长正变换序列或两个半长逆变换序列;

58、所述二进制翻转器的输入端连接所述第三存储器的输出端,所述二进制翻转器用于对两个半长正变换序列拼接后的正变换拼接序列进行逆序重排处理,获得全长正变换序列,或者对两个半长逆变换序列拼接后的逆变换拼接序列进行逆序重排处理,获得全长逆变换序列;

59、所述第四存储器的输入端连接所述二进制翻转器的输出端,用于存储所述全长正变换序列或全长逆变换序列。

60、作为本发明的另一个方面,提供一种用于全长数论变换的硬件加速装置,用于实现前文所述的用于全长数论变换的硬件加速方法,其中,包括:

61、接收模块,用于接收全长待正变换序列或全长待逆变换序列;

62、半长加速计算模块,用于将所述全长待正变换序列输入至数论变换计算单元进行计算处理获得全长正变换序列,或者,将所述全长待逆变换序列输入至数论变换计算单元进行计算处理获得全长逆变换序列,其中所述数论变换计算单元能够对所述全长待正变换序列进行预处理后获得半长正变换待加速序列,以及能够将所述半长正变换待加速序列通过半长硬件加速器进行加速计算获得全长正变换序列,或者,所述数论变换计算单元能够对所述全长待逆变换序列进行预处理后获得半长逆变换待加速序列,以及能够将所述半长逆变换待加速序列通过半长硬件加速器进行加速计算获得全长逆变换序列;所述半长正变换待加速序列的序列长度为所述全长待正变换序列的序列长度的一半,所述半长逆变换待加速序列的序列长度为所述全长待逆变换序列的序列长度的一半;

63、输出模块,用于输出所述全长正变换序列或全长逆变换序列。

64、作为本发明的另一个方面,提供一种安全芯片,其中,包括芯片载体及设置在所述芯片载体上的前文所述的用于全长数论变换的硬件加速装置。

65、本发明提供的用于全长数论变换的硬件加速方法,通过数论变换计算单元对全长待正变换序列获得半长正变换待加速序列,或者通过数论变换计算单元对全长待逆变换序列进行预处理后获得半长逆变换待加速序列,从而能够通过半长硬件加速器实现对半长正变换待加速序列或者半长逆变换待加速序列的加速计算,最终针对半长的硬件加速计算结果整合获得全长正变换序列或全长逆变换序列。这种用于全长数论变换的硬件加速方法能够通过半长硬件实现全长ntt变换,解决了现有技术中ntt加速器固定项数在实际应用时存在局限性的问题,从而可以在现有ntt硬件加速器配置的可执行项数不变的情况下实现更长序列的ntt变换。

本文地址:https://www.jishuxx.com/zhuanli/20240914/295477.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表