一种高压碳化硅MOSFET的漏电流检测电路及方法

- 国知局

- 2024-10-21 14:49:11

本发明涉及封装测试,具体为一种一种高压碳化硅mosfet的漏电流检测电路及方法。

背景技术:

1、在功率模块的设计与研制中,测试往往用于评估产品的可靠性与性能,是其中必不可少的环节。对于高压碳化硅模块的测试,测试标准和规范的缺乏是一个重要的挑战。

2、当选择高温反偏测试(htrb)对高压碳化硅模块进行电老化测试时,htrb要求在高温环境(优选最大工作结温)下,对mosfet施加接近其最大额定电压的反向偏置电压,进行1000小时的测试并测量漏电流以及其他电特性参数。碳化硅mosfet芯片的漏电流ids一般仅仅为几微安,即使经过长时间的加速老化也无法达到ma级别,同时在高压工况下随时有击穿风险,采样的响应时间也要足够快。因此,一个实时监测且精确采样的漏电流检测方案对于高压碳化硅模块在测试中的可靠性评估具有重要意义。

3、在传统的中低压领域中,htrb测试已有成熟的商业产品,但其试验电源电压往往只能达到2000v,远不能达到高压mosfet测试的标准。对于高精度的电流采样,常见的方法分为接触式与非接触式两种。非接触式电流采样一般采用霍尔传感器或磁环,这种方法能够实现被采集电路与控制电路电气隔离,电压隔离等级高。但缺点是电路复杂、重量大,且精度很难达到微安级。接触式测量有电流采样芯片、电流镜与采样电阻放大三种。目前电流采样专用芯片隔离等级均不达标,难以满足高压环境;电流镜采样电路简单,但采样精度低,无法达到微安级水平;采样电阻放大能达到精度要求,但放大器的电压隔离也是需要解决的问题。

技术实现思路

1、针对现有技术中选择htrb测试进行高压mosfet测试时难以达到的微安级电流采样、10kv以上电压隔离以及秒级响应速度的测试要求的问题,本发明提供一种高压碳化硅mosfet的漏电流检测电路及方法。

2、本发明是通过以下技术方案来实现:

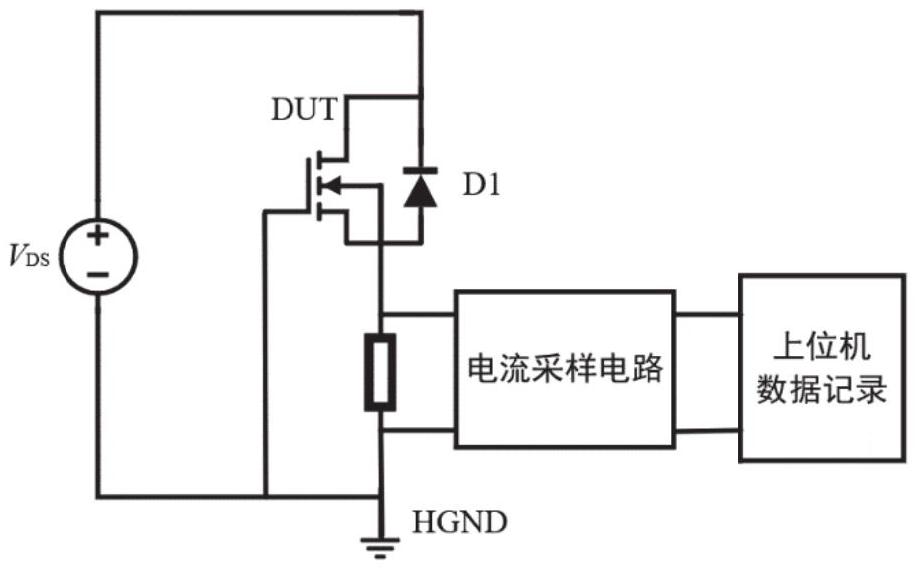

3、一种高压碳化硅mosfet的漏电流检测电路,包括htrb测试主电路、采样电路,测试所用的加热台和待测高压碳化硅mosfet均与主电路连接,采样电路包括采样电阻、仪用放大器、adc转换器和dsp处理器,待测高压碳化硅mosfet的栅极接在采样电阻与htrb测试主电路之间,采样电阻的一端与htrb测试主电路的负极连接,采样电阻与仪用放大器的输入端连接,仪用放大器的输出端与adc转换器的输入端连接,adc转换器的输出端与dsp处理器的输入端连接。

4、优选的,还包括高压保护电路,高压保护电路包括瞬态电压抑制二极管和熔断器,瞬态电压抑制二极管与采样电阻并联。

5、优选的,测试时,htrb测试电路的正极与待测高压碳化硅mosfet的漏极连接,待测高压碳化硅mosfet的源极与htrb测试电路的负极连接,htrb测试电路的负极接地,待测高压碳化硅mosfet的栅极与通过采样电阻与大地短接。

6、优选的,还包括上位机,上位机的输入端与dsp处理器的输出端连接。

7、一种高压碳化硅mosfet的漏电流检测方法,采用所述的检测电路,包括以下步骤:

8、s1,将待测高压碳化硅mosfet接入测试电路中,并使待测高压碳化硅mosfet的栅极与大地短接;

9、s2,打开电源和加热台,在测试温度下对待测高压碳化硅mosfet施加反向偏置电压;

10、s3,打开dsp电路开关,进行漏电流的采样,同时于上位机中运行程序捕捉和记录漏电流的变化量以及变化时间。

11、优选的,s2中,测试温度为最大工作结温。

12、优选的,s2中,反向偏置电压小于待测高压碳化硅mosfet的最大额定电压。

13、优选的,反向偏置电压为待测高压碳化硅mosfet的最大额定电压的80~100%。

14、优选的,测试结束后,对采集的漏电流数据进行分析,当最终漏电流ids超过限值或者待测高压碳化硅mosfet的漏电流的初始值的五倍时,待测高压碳化硅mosfet未通过测试。

15、优选的,漏电流ids的限值小于或者等于10μa。

16、与现有技术相比,本发明具有以下有益效果:

17、本发明一种高压碳化硅mosfet的漏电流检测电路通过对漏电流采样电路的设计,实现微安级电流采样、10kv以上电压隔离以及秒级响应速度的测试要求;通过对上位机程序配置,实现数据的实时记录与长期无人值守试验。其中,主电路用于对待测高压碳化硅mosfet施加反向偏置电压和提供测试所需的温度环境;采样电路用于转换和放大漏电流iv,并通过dsp处理器将电压信号转换为数字信号并实时记录。其中,微安级电流采样体现在传统的电路往往是检测si igbt器件,其初始漏电流大小为几百微安;而高压sicmosfet器件特性决定其漏电流在几微安,该检测电路能够准确对其进行检测,采样精度就已经达到了微安级。10kv以上电压隔离则体现在该电路通过设计高压保护电路使其能在高压击穿发生时对后面检测部分得到有效保护。目前进行测试的为10kv高压碳化硅mosfet,即vds达到10kv,测试很成功。也就说明了10kv以上电压隔离。

18、进一步的,引入瞬态电压抑制二极管(tvs)和熔断器是为了有效保护电路免受高压瞬态冲击和过流损坏。

19、进一步的,上位机用于显示漏电流的变化量和变化时间,可以提高测试的自动化程度和数据处理效率。在上位机程序中,还可以设置合理的阈值和报警机制,以便在漏电流超出预期范围时及时发出警告。

20、本发明一种高压碳化硅mosfet的漏电流检测方法旨在确保在极端条件下(如高温和反向偏置电压)对mosfet的漏电流性能进行准确评估。

技术特征:1.一种高压碳化硅mosfet的漏电流检测电路,其特征在于,包括htrb测试主电路、采样电路,测试所用的加热台和待测高压碳化硅mosfet均与主电路连接,采样电路包括采样电阻、仪用放大器、adc转换器和dsp处理器,待测高压碳化硅mosfet的栅极接在采样电阻与htrb测试主电路之间,采样电阻的一端与htrb测试主电路的负极连接,采样电阻与仪用放大器的输入端连接,仪用放大器的输出端与adc转换器的输入端连接,adc转换器的输出端与dsp处理器的输入端连接。

2.根据权利要求1所述的一种高压碳化硅mosfet的漏电流检测电路,其特征在于,还包括高压保护电路,高压保护电路包括瞬态电压抑制二极管和熔断器,瞬态电压抑制二极管与采样电阻并联。

3.根据权利要求1所述的一种高压碳化硅mosfet的漏电流检测电路,其特征在于,测试时,htrb测试电路的正极与待测高压碳化硅mosfet的漏极连接,待测高压碳化硅mosfet的源极与htrb测试电路的负极连接,htrb测试电路的负极接地,待测高压碳化硅mosfet的栅极与通过采样电阻与大地短接。

4.根据权利要求1所述的一种高压碳化硅mosfet的漏电流检测电路,其特征在于,还包括上位机,上位机的输入端与dsp处理器的输出端连接。

5.一种高压碳化硅mosfet的漏电流检测方法,采用如权利要求1~4任一项所述的检测电路,其特征在于,包括以下步骤:

6.根据权利要求5所述的一种高压碳化硅mosfet的漏电流检测电路,其特征在于,s2中,测试温度为最大工作结温。

7.根据权利要求5所述的一种高压碳化硅mosfet的漏电流检测电路,其特征在于,s2中,反向偏置电压小于待测高压碳化硅mosfet的最大额定电压。

8.根据权利要求7所述的一种高压碳化硅mosfet的漏电流检测电路,其特征在于,反向偏置电压为待测高压碳化硅mosfet的最大额定电压的80~100%。

9.根据权利要求5所述的一种高压碳化硅mosfet的漏电流检测电路,其特征在于,测试结束后,对采集的漏电流数据进行分析,当最终漏电流ids超过限值或者待测高压碳化硅mosfet的漏电流的初始值的五倍时,待测高压碳化硅mosfet未通过测试。

10.根据权利要求9所述的一种高压碳化硅mosfet的漏电流检测电路,其特征在于,漏电流ids的限值小于或者等于10μa。

技术总结本发明涉及封装测试技术领域,具体为一种高压碳化硅MOSFET的漏电流检测电路及方法,该电路包括HTRB测试主电路、采样电路,测试所用的加热台和待测高压碳化硅MOSFET均与主电路连接,采样电路包括采样电阻、仪用放大器、ADC转换器和DSP处理器,待测高压碳化硅MOSFET的栅极接在采样电阻与HTRB测试主电路之间,采样电阻的一端与HTRB测试主电路的负极连接,采样电阻与仪用放大器的输入端连接,仪用放大器的输出端与ADC转换器的输入端连接,ADC转换器的输出端与DSP处理器的输入端连接,本发明设计合理、全面,能够准确评估MOSFET在极端条件下的漏电流性能,通过进一步优化电路设计和检测方法,可以进一步提高测试的准确性和可靠性,为MOSFET的可靠性评估和筛选提供有力支持。技术研发人员:王来利,丁培洋,赵志强,陈琪岭,郭佳成,马良俊,袁天舒,牛芝雅受保护的技术使用者:西安交通大学技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/319412.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表