一种低杂散电感IGBT模块芯片的布局结构及制作方法与流程

- 国知局

- 2024-11-06 14:22:51

本发明属于电子器件,涉及一种低杂散电感igbt模块芯片的布局结构及制作方法。

背景技术:

1、目前大功率igbt器件普遍采用多芯片并联方法提高其功率等级。现有技术中并联功率半导体芯片由于控制回路长度不同,且控制回路和功率回路有重叠,导致并联芯片间开关不同步或电流不均衡,由于igbt器件内部并联芯片的均流效果会对器件的性能产生较大影响,并联芯片间电流分布不均将导致芯片功耗不同,内部温度分布存在差异,长时间尺度下薄弱环节凸显,缩短器件整体使用寿命。

2、传统高压大功率器件芯片布局结构如图1所示。第一芯片1-1、第二芯片1-2、第三芯片1-3、第四芯片1-4为功率igbt芯片,第五芯片2-1、第六芯片2-2为frd芯片,4个igbt芯片和2个frd芯片反并联连接在dbc基板10上。igbt芯片的集电极和frd芯片阴极连接于基板(10)铜层3上;igbt芯片发射极和frd芯片阳极通过第十一键合线9-1、第十二键合线9-2、第十三键合线9-3、第十四键合线9-4、第十五键合线9-5、第十六键合线9-6连接于第六铜层4上;信号端子g连接在第三铜层5上,并通过第五键合线7-1和第六铜层7,以及第六键合线8-1、第七键合线8-2、第八键合线8-3、第九键合线8-4分别与4个igbt芯片栅极连接。辅助发射极端子连接在第四铜层6上,通过第十键合线6-1和第六铜层4,以及第十一键合线9-1、第十二键合线9-2、第十三键合线9-3、第十四键合线9-4分别igbt芯片发射极连接,组成控制回路。主功率端子c和主功率端子e分别连接在第一铜层3和第六铜层4上,通过键合线和功率芯片组成功率回路。现有技术芯片布局遵守了左右对称原则,但由于驱动回路辅助发射极引出端子采用kelvin端子,辅助发射极端子到功率端子e间的杂散电感(如图2所示)由两部分构成:lee为共发射极杂散电感,主功率回路与驱动回路共同使用(图1虚线a的a部分);le为kelvin端子到功率端子e的电感,用作驱动回路(图1虚线b的b部分)。

3、并联芯片回路长度不同导致寄生参数的差异,如图1中回路a和回路b分别为芯片1-1和芯片1-2的控制回路,驱动发射极到芯片发射极杂散电感lee(图1中回路a由于路径不同,杂散电感也会不同。由于经过功率回路,而实际应用中功率回路电流变化率dic/dt非常大,杂散电感的差异将导致芯片间电流的差异。通过仿真得出,芯片1-1和芯片1-4间寄生电感相差约6.6nh,高压大功率器件dic/dt非常大,如6500v600a模块开通时刻电流变化率约为1000a/ìs,导致芯片1-1和芯片1-4间驱动电压相差约6.6v,造成芯片间开关的不同步和电流的不均衡。

技术实现思路

1、本发明的目的在于克服上述现有技术的缺点,提出一种低杂散电感igbt模块芯片的布局结构及制作方法。

2、为了实现上述目的,本发明采用了如下技术方案:

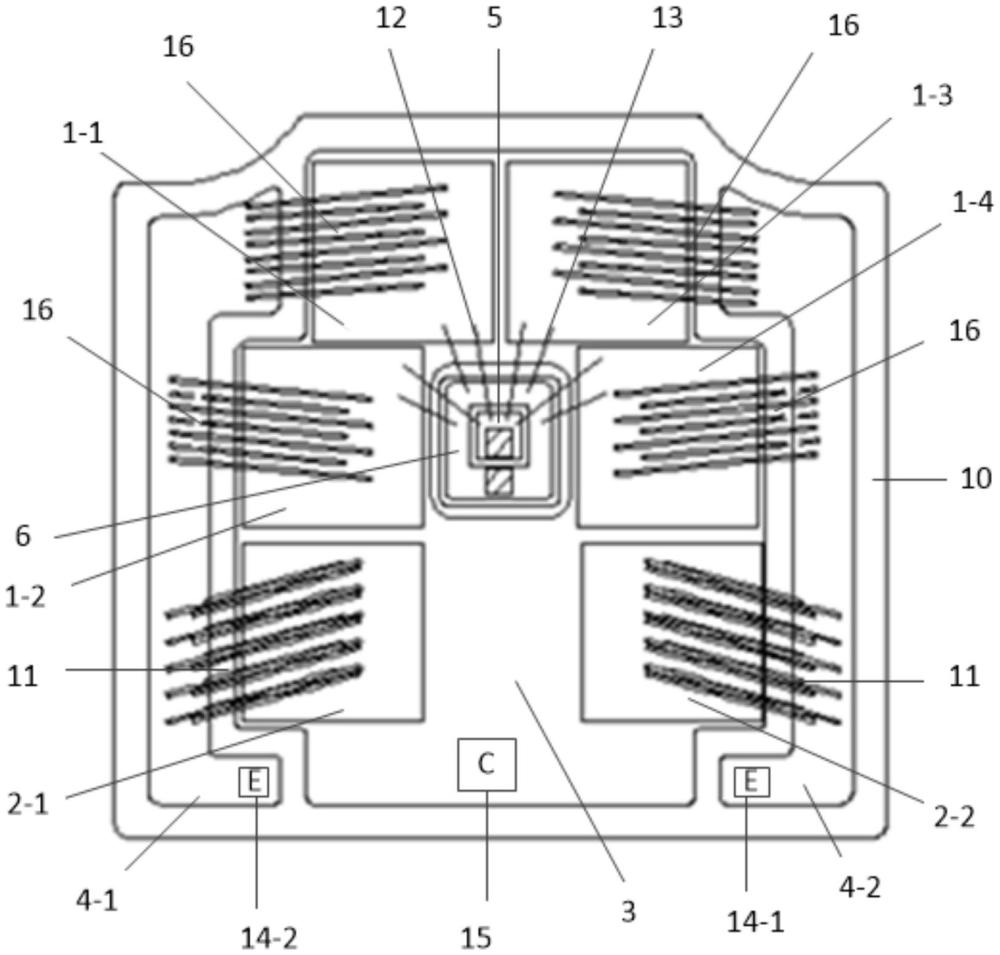

3、一种低杂散电感igbt模块芯片的布局结构,包括基板,所述基板上左右对称设置有多个芯片,所述芯片包括igbt芯片和frd芯片,所述基板上还设置有第一铜层、第二铜层、第五铜层;所述第一铜层与igbt芯片的集电极、frd芯片的阴极相连接;所述第二铜层与基板左侧的芯片的发射极和阳极相连接,所述第五铜层与基板右侧的芯片的发射极和阳极相连接;

4、所述基板的中心位置设置有端子连接部,所述端子连接部包括与驱动信号端子相连接的第三铜层、与辅助发射极端子相连接的第四铜层,所述第三铜层与每个芯片的驱动信号端子相连接的回路的长度相等,所述第四铜层与辅助发射极端子相连接的回路的长度相等;

5、所述第一铜层设置于基板左侧最下方的芯片和的基板右侧最下方芯片之间;

6、所述第二铜层设置于左侧芯片的外侧,所述第二铜层与基板左侧的芯片的发射极或阳极相连接;所述第五铜层设置于右侧芯片的外侧,所述第五铜层与基板右侧的芯片的发射极或阳极相连接。

7、进一步地,所述第三铜层设置于端子连接部的中心位置,所述第三铜层的外侧环绕设置有第四铜层。

8、进一步地,所述第三铜层和第四铜层的区域设置为两个相对的“e”形,所述第三铜层和第四铜层相互嵌合。

9、进一步地,所述第二铜层上设置有第一发射极焊接位,所述第五铜层上设置有第二发射极焊接位,所述第一铜层上设置有集电极焊接位。

10、进一步地,所述芯片为硅芯片、碳化硅芯片或氮化镓芯片。

11、进一步地,所述基板的两个上角处设置有凹口。

12、进一步地,所述基板上的igbt芯片与frd芯片的数量比为:(1~2):1。

13、本发明还提供了一种低杂散电感igbt模块芯片的布局结构的制作方法,包括以下步骤:

14、步骤一:在基板上设置第一铜层、第三铜层、第四铜层、第二铜层、第五铜层;

15、步骤二:在第二铜层的内侧设置多个第一igbt芯片和若干第一frd芯片,在第五铜层的内侧设置多个第二igbt芯片和若干第二frd芯片;

16、步骤三:将每个第一igbt芯片的发射极与第二铜层通过第一键合线相连接,将每个第一frd芯片的阳极与第二铜层通过第二键合线相连接;将每个第二igbt芯片的发射极与第二铜层通过第一键合线相连接,将每个第二frd芯片的阳极与第二铜层通过第二键合线相连接;

17、将第三铜层与每个第一igbt芯片和每个第二igbt芯片的栅极通过第三键合线相连接,将第四铜层与igbt芯片的发射极通过第四键合线相连接。

18、进一步地,所述第一键合线、第二键合线、第三键合线、第四键合线为铝线、铝带、铜线、铜带、铝包铜线中的其中一种。

19、与现有技术相比,本发明具有以下有益效果:

20、第一,本发明提出的一种igbt模块的芯片布局结构,将驱动信号端子放置在dbc基板中间位置,与4个并联igbt芯片栅极距离相同,且通过键合线与芯片栅极直接连接。

21、第二,辅助发射极端子连接的铜层包围驱动信号端子连接的铜层,且与芯片发射极直接连接,不仅减小驱动回路路径,使并联igbt芯片驱动回路路径相同,且避免了驱动回路路径与功率回路路径的重叠,降低了并联igbt芯片间驱动电压的差异,减小了芯片间的电流差异率,芯片均流性能得到提升,有利于芯片的长期稳定运行。

技术特征:1.一种低杂散电感igbt模块芯片的布局结构,其特征在于,包括基板(10),所述基板(10)上左右对称设置有多个芯片,所述芯片包括igbt芯片和frd芯片,所述基板(10)上还设置有第一铜层(3)、第二铜层(4-1)、第五铜层(4-2);所述第一铜层(3)与igbt芯片的集电极、frd芯片的阴极相连接;所述第二铜层(4-1)与基板(10)左侧的芯片的发射极和阳极相连接,所述第五铜层(4-2)与基板(10)右侧的芯片的发射极和阳极相连接;

2.根据权利要求1所述的一种低杂散电感igbt模块芯片的布局结构,其特征在于,所述第三铜层(5)设置于端子连接部的中心位置,所述第三铜层(5)的外侧环绕设置有第四铜层(6)。

3.根据权利要求1所述的一种低杂散电感igbt模块芯片的布局结构,其特征在于,所述第三铜层(5)和第四铜层(6)的区域设置为两个相对的“e”形,所述第三铜层(5)和第四铜层(6)相互嵌合。

4.根据权利要求1所述的一种低杂散电感igbt模块芯片的布局结构,其特征在于,所述第二铜层(4-1)上设置有第一发射极焊接位(14-2),所述第五铜层(4-2)上设置有第二发射极焊接位(14-1),所述第一铜层(3)上设置有集电极焊接位(15)。

5.根据权利要求1所述的一种低杂散电感igbt模块芯片的布局结构,其特征在于,所述芯片为硅芯片、碳化硅芯片或氮化镓芯片。

6.根据权利要求1所述的一种低杂散电感igbt模块芯片的布局结构,其特征在于,所述基板(10)的两个上角处设置有凹口。

7.根据权利要求1所述的一种低杂散电感igbt模块芯片的布局结构,其特征在于,所述基板(10)上的igbt芯片与frd芯片的数量比为(1~2):1。

8.一种如权利要求1~7所述的一种低杂散电感igbt模块芯片的制作方法,其特征在于,包括以下步骤:

9.根据权利要求8所述的一种低杂散电感igbt模块芯片的制作方法,其特征在于,所述第一键合线(16)、第二键合线(11)、第三键合线(12)、第四键合线(13)均为铝线、铝带、铜线、铜带、铝包铜线中的其中一种。

技术总结本发明属于电子器件技术领域,涉及一种低杂散电感IGBT模块芯片的布局结构及制作方法。基板上左右对称设置有多个芯片,芯片包括IGBT芯片和FRD芯片,所述基板上还设置有第一铜层、第二铜层、第五铜层;第一铜层与IGBT芯片的集电极、FRD芯片的阴极相连接;第二铜层与基板左侧的芯片的发射极和阳极相连接,第五铜层与基板右侧的芯片的发射极和阳极相连接;基板的中心位置设置有端子连接部,第三铜层与每个芯片的驱动信号端子相连接的回路的长度相等。将驱动信号端子放置在DBC基板中间位置,与4个并联IGBT芯片栅极距离相同,且通过键合线与芯片栅极直接连接。技术研发人员:荆海燕,刘艳宏,王晓丽,邢毅受保护的技术使用者:西安中车永电电气有限公司技术研发日:技术公布日:2024/11/4本文地址:https://www.jishuxx.com/zhuanli/20241106/321694.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。