一种可集成的纵向高压器件及其制备方法与流程

- 国知局

- 2024-11-19 09:30:53

本发明涉及半导体器件,尤其涉及一种纵向高压器件及其制备方法。

背景技术:

1、在高压集成电路领域中,往往需要大面积的功率输出管和普通的互补金属氧化物半导体(complementary metal oxide semiconductor cmos)器件集成。对于传统的bcd(bipolar-cmos-dmos)工艺中,大面积的功率管使用平面式横向扩散金属氧化物半导体(laterally diffused metal oxide semiconductor,ldmos)器件完成,但是对于ldmos器件而言,特别是随着电压的提升,该种器件的面积会剧烈增加,导致高压下器件性价比急剧下降,同时高压ldmos可靠性差,也一直限制着高压bcd工艺的持续发展。

2、在现有的做法中,功率管也会会采用纵向高压器件,即将ldmos的漏极设置在芯片的背面,以缩小器件面积,提高芯片的利用率,芯片的基板一般为极低电阻的硅,需要在基板上外延一定厚度的高阻硅,并在外延的高阻硅上形成栅极深槽,填充多晶硅槽栅,以形成纵向器件。可在纵向高压器件中注入深阱,以隔离高压器件和平面cmos器件,从而将cmos器件集成于纵向高压器件,同时完成纵向高压器件和平面cmos器件,实现高压bcd工艺。

3、但是,为形成深槽栅结构,以及保证纵向高压器件的耐压值,需要设置较大厚度的外延高阻硅,会导致深阱注入难度较大,难以达到较大深度的深阱注入,若注入深度相较于外延高阻硅较浅,则不利于器件集成,若为满足器件集成,需要设置较小厚度的外延高阻硅,则无法满足较高的耐压值。

技术实现思路

1、本发明提供了一种纵向高压器件及其制备方法,以提高压器件的可靠性,实现大面积的功率输出管的集成。

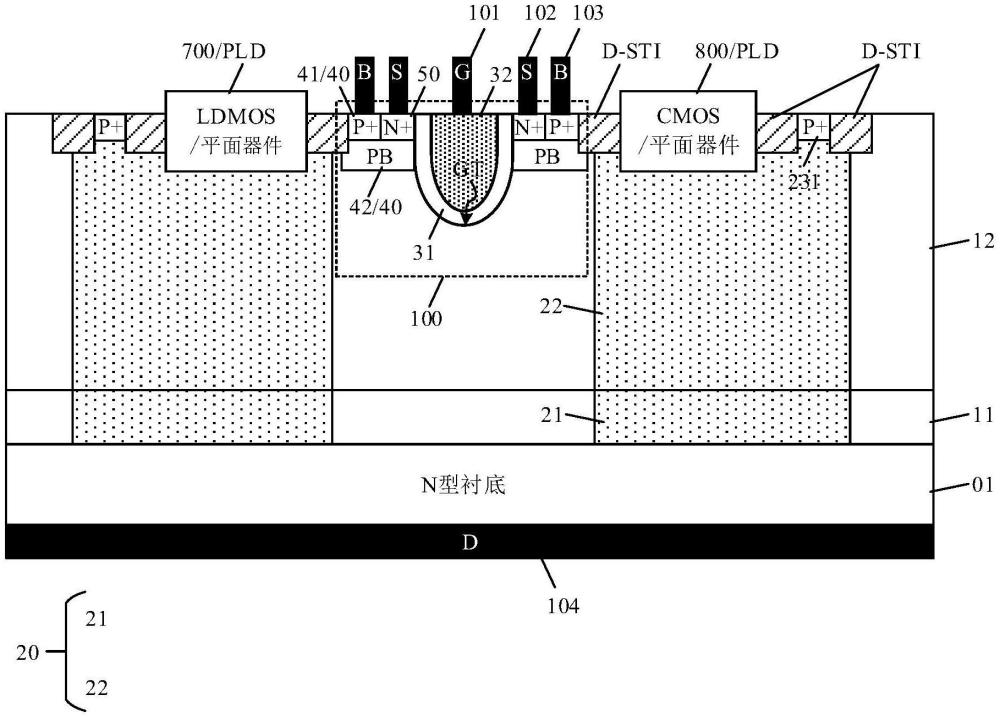

2、根据本发明的一方面,提供了一种可集成的纵向高压器件,包括:

3、n型衬底;

4、第一n型外延层,位于所述n型衬底的上方;

5、第一p阱区,位于所述第一n型外延层;

6、第二n型外延层,位于所述第一n型外延层的上方;

7、第二p阱区,位于所述第二n型外延层,且位于所述第一p阱区的上方;

8、栅极沟槽,位于未设置所述第二p阱区的所述第二n型外延层;所述栅极沟槽内设置有纵向栅氧化层和纵向多晶硅栅,所述纵向栅氧化层包裹所述纵向多晶硅栅;

9、纵向体区,也位于未设置所述第二p阱区的所述第二n型外延层;所述纵向体区与所述栅极沟槽沿水平方向相邻设置;其中,所述纵向体区设置有纵向源区、体重掺杂区和体轻掺杂区,所述体重掺杂区、所述纵向源区和所述栅极沟槽沿水平方向依次相邻设置,所述体轻掺杂区位于所述体重掺杂区和所述纵向源区的下方;

10、平面器件,位于所述第二p阱区,且位于所述第二p阱区的上表面;其中,所述平面器件包括ldmos晶体管和/或cmos器件。

11、可选的,所述平面器件包括所述ldmos晶体管和所述cmos器件;

12、所述ldmos晶体管和所述cmos器件分别位于不同的所述第二p阱区,且不同的所述第二p阱区分别位于不同的所述第一p阱区的上方;

13、沿水平方向,所述纵向高压器件、所述ldmos晶体管和所述cmos器件中任意两者之间设置有器件浅槽隔离。

14、可选的,在未设置所述第二p阱区的所述第二n型外延层设置有漏区;所述漏区贯穿所述第二n型外延层和所述第一n型外延层,连接所述n型衬底;

15、其中,至少部分所述第一p阱区以及其上方的所述第二p阱区位于所述漏区与所述纵向高压器件之间。

16、可选的,所述漏区包括深n阱区;

17、或者,所述漏区包括深漏槽,以及位于所述深漏槽内的n型多晶硅;

18、或者,所述漏区包括深漏槽,以及位于所述深漏槽内的导电金属结构。

19、可选的,还包括:p型衬底;

20、所述p型衬底位于所述n型衬底的下方。

21、可选的,所述平面器件包括所述ldmos晶体管;

22、所述ldmos晶体管包括位于所述第二p阱区的横向漂移区和横向体区;

23、所述ldmos晶体管还包括位于所述横向漂移区的横向漏区、位于所述横向体区的横向源区、以及至少部分位于所述横向漂移区和所述横向体区之间,且位于所述第二p阱区上方的横向多晶硅栅。

24、可选的,所述ldmos晶体管还包括位于所述横向漂移区上方的横向浅槽隔离;

25、所述横向浅槽隔离位于所述横向漏区靠近所述横向体区的一侧,且所述横向浅槽隔离与所述横向漏区沿水平方向相邻设置;

26、沿竖直方向,所述横向浅槽隔离的深度大于或等于所述横向漏区的深度。

27、可选的,所述平面器件包括所述cmos器件;

28、所述cmos器件包括位于所述第二p阱区的p型体区、n型体区,以及位于所述p型体区的nmos区和位于所述n型体区的pmos区;

29、所述nmos区包括两个n型重掺杂区,两个所述n型重掺杂区之间存在第一间隔;所述第一间隔的上方设置有第一栅氧化层和第一多晶硅栅,其中,所述第一多晶硅栅位于所述第一栅氧化层的上方;

30、所述pmos区包括两个p型重掺杂区,两个所述p型重掺杂区之间存在第二间隔;所述第二间隔的上方设置有第二栅氧化层和第二多晶硅栅,其中,所述第二多晶硅栅位于所述第二栅氧化层的上方。

31、可选的,所述p型体区还包括p型体重掺杂区,所述p型体重掺杂区位于所述nmos区的其中一个所述n型重掺杂区远离所述第一间隔的一侧,且所述p型体重掺杂与该所述n型重掺杂区之间设置有第一浅槽隔离;

32、所述n型体区还包括n型体重掺杂区,所述n型体重掺杂区位于所述pmos区的其中一个所述p型重掺杂区远离所述第二间隔的一侧,且所述n型体重掺杂与该所述p型重掺杂区之间设置有第二浅槽隔离;

33、所述cmos器件还包括位于所述p型体区和所述n型体区之间的第三浅槽隔离。

34、根据本发明的另一方面,提供了一种如上述可集成的纵向高压器件的制备方法,包括:

35、提供n型衬底;

36、在所述n型衬底的上方生长第一n型外延层,并在所述第一n型外延层的部分区域进行离子注入,以形成第一p阱区;

37、在所述第一n型外延层的上方生长第二n型外延层,并在所述第一p阱区上方的所述第二n型外延层进行离子注入,以形成第二p阱区;

38、在未设置所述第二p阱区的所述第二n型外延层形成纵向高压器件,以及在所述第二p阱区形成平面器件。

39、可选的,在所述第一n型外延层的部分区域进行离子注入,以形成第一p阱区,包括:进行第一温度的高温炉管推结;所述第一温度大于或等于1000℃,小于或等于1500℃;

40、和/或,在所述第一p阱区上方的所述第二n型外延层进行离子注入,以形成第二p阱区,包括:进行第二温度的高温炉管推结;所述第二温度大于或等于1000℃,小于或等于1500℃。

41、可选的,在未设置所述第二p阱区的所述第二n型外延层形成纵向高压器件,包括:

42、在未设置所述第二p阱区的所述第二n型外延层进行刻蚀,形成深漏槽,露出所述n型衬底;

43、在所述深漏槽中填充n型多晶硅或导电金属结构。

44、可选的,所述纵向高压器件还包括p型衬底;所述p型衬底位于所述n型衬底的下方;

45、提供n型衬底,包括:

46、提供p型衬底,在所述p型衬底的上方进行外延,形成所述n型衬底;

47、或者,提供p型衬底,在所述p型衬底进行离子注入,形成所述n型衬底;

48、或者,提供p型衬底,在所述p型衬底的上方键合所述n型衬底。

49、本发明的技术方案,通过设置纵向高压器件,有利于节省信号走线的空间,缩小横向空间,同时,还有利于降低导通电阻;通过在n型衬底的上方设置第一n型外延层、第二n型外延层,以及在第一n型外延层中设置第一p阱区,在第一p阱区上方的第二n型外延层中设置第二p阱区,可以分两次进行外延,分别形成第一n型外延层、第二n型外延层,还可以在每次外延后分别进行离子注入,即分两次注入,分别形成第一p阱区和第二p阱区,以降低深阱注入难度,实现较大深度的深阱注入,有利于平面器件的集成,同时,实现较高的耐压值;另外,第一p阱区和第二p阱区既可以隔离纵向高压器件和平面器件,也可以作为平面器件的衬底,在第二p阱区中制备形成平面器件,以便于器件的集成,提高集成度。

50、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

本文地址:https://www.jishuxx.com/zhuanli/20241118/329115.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表