半导体结构及其制造方法与流程

- 国知局

- 2024-12-06 12:37:57

本申请涉及半导体,特别是涉及一种半导体结构及其制造方法。

背景技术:

1、超结(super junction)金属氧化物半导体场效应管(metal oxidesemiconductor field effect transistor,简称mosfet)是一种新型功率半导体器件,其在常规纵向双扩散金属氧化物半导体(vertical diffused metal oxide semiconductor,简称vdmos)的基础上,引入超结结构(super junction)。超结mosfet器件不仅具有vdmos的输入阻抗高、开关速度快、工作频率高、电压控制性好、热稳定性好以及驱动电路简单的优良特性,还能够在此基础上克服vdmos的导通电阻随击穿电压急剧增大的缺点。其中,超结mosfet器件中p柱的制造工艺对器件的整体性能以及成本有着很大影响。

2、相关技术中,p柱的制造通常采用多层外延工艺以及深沟槽外延填充工艺。然而,多层外延工艺通常采用多次光刻、多次离子注入以及多次推进过程形成p柱,存在工艺复杂以及成本较高问题;此外,深沟槽外延填充工艺通常采用一次沟槽刻蚀以及一次外延生长形成p柱,因沟槽的深宽比较大,容易存在沟槽顶部封口问题,导致沟槽内部形成不规则空洞,从而造成器件的可靠性降低。

技术实现思路

1、基于此,本申请实施例提供了一种半导体结构及其制造方法,以有效避免沟槽顶部封口问题以及外延填充层内部空洞问题,从而提升产品良率并提高器件的可靠性。

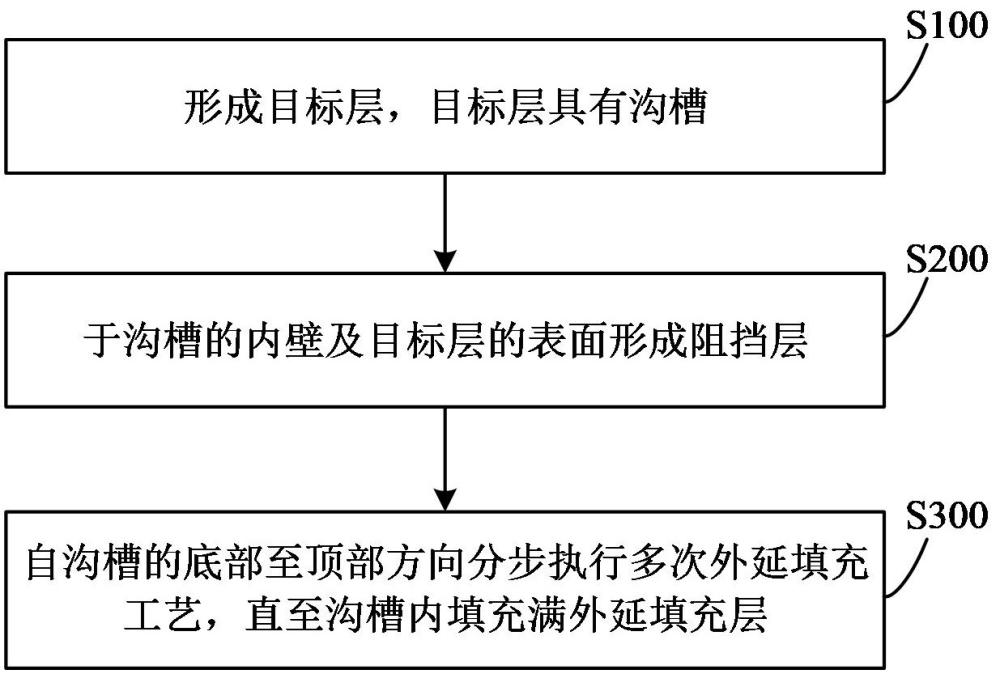

2、为了实现上述目的,一方面,本申请一些实施例提供了一种半导体结构的制造方法。该制造方法包括:形成目标层,目标层具有沟槽;于沟槽的内壁及目标层的表面形成阻挡层;自沟槽的底部至顶部方向分步执行多次外延填充工艺,直至沟槽内填充满外延填充层;其中,单次外延填充工艺包括:去除部分阻挡层,以至少裸露出沟槽的部分内壁;于沟槽的裸露内壁上形成外延填充层。

3、在一些实施例中,单次外延填充工艺还包括:在沟槽的裸露内壁上形成外延填充层的过程中,向沟槽内通入目标气体,以去除阻挡层表面上的外延填充材料。

4、在一些实施例中,目标气体包括氯化氢气体。

5、在一些实施例中,阻挡层保形覆盖沟槽的内壁;自沟槽的底部至其顶部的方向,阻挡层的成膜厚度逐渐增大。

6、在一些实施例中,阻挡层的形成工艺包括炉管热氧化工艺。

7、在一些实施例中,阻挡层采用氢气烘焙工艺去除。

8、在一些实施例中,去除部分阻挡层时,至少包括如下一项特征:

9、氢气烘焙工艺的氢气流量范围包括:10slm~100slm;

10、氢气烘焙工艺的烘焙温度范围包括:900℃~1200℃;

11、氢气烘焙工艺的炉腔压力范围包括:100torr~600torr;

12、氢气烘焙工艺的烘焙时间范围包括:40s~120s。

13、在一些实施例中,半导体结构的制造方法还包括:在沟槽内填充满外延填充层之后,研磨外延填充层和目标层的表面,使得保留于沟槽内的外延填充层构成超结结构的第一导电类型柱;其中,目标层包括第二导电类型外延层。

14、另一方面,本公开还根据一些实施例提供了一种半导体结构;该半导体结构包括目标层和外延填充层。目标层具有沟槽;外延填充层填充满沟槽;外延填充层采用如本公开前述一些实施例中任一项所述的半导体结构的制造方法形成。

15、在一些实施例中,外延填充层包括第一导电类型柱;目标层包括第二导电类型外延层;外延填充层和目标层构成超结结构。

16、本申请实施例可以/至少具有以下优点:

17、本申请实施例中,通过于沟槽的内壁及目标层的表面形成阻挡层,并自沟槽的底部至顶部方向执行多次外延填充工艺,在每次外延填充工艺中都去除部分阻挡层并于沟槽内未被阻挡层覆盖的裸露内壁沉积形成外延填充层,以通过去除工艺与外延工艺多次交替执行的方式,于沟槽内由下至上逐步形成填充满沟槽的外延填充层。如此,通过形成阻挡层以及分步执行多次外延填充工艺获得外延填充层,防止了目标层表面以及沟槽顶部出现外延填充材料堆积,以避免了沟槽在外延填充过程中的顶部封口问题;此外,还提高了沟槽中外延填充层的填充质量,避免了外延填充层内部空洞问题,从而提高了器件的可靠性。

18、本申请的一个或多个实施例的细节在下面的附图和描述中提出。本申请的其他特征、目的和优点将从说明书、附图以及权利要求书变得明显。

技术特征:1.一种半导体结构的制造方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制造方法,其特征在于,单次所述外延填充工艺还包括:

3.根据权利要求2所述的半导体结构的制造方法,其特征在于,所述目标气体包括氯化氢气体。

4.根据权利要求1所述的半导体结构的制造方法,其特征在于,

5.根据权利要求4所述的半导体结构的制造方法,其特征在于,所述阻挡层的形成工艺包括炉管热氧化工艺。

6.根据权利要求4所述的半导体结构的制造方法,其特征在于,所述阻挡层采用氢气烘焙工艺去除。

7.根据权利要求6所述的半导体结构的制造方法,其特征在于,所述去除部分所述阻挡层时,至少包括如下一项特征:

8.根据权利要求1~7中任一项所述的半导体结构的制造方法,其特征在于,还包括:

9.一种半导体结构,其特征在于,包括:

10.根据权利要求9所述的半导体结构,其特征在于,所述外延填充层包括第一导电类型柱;所述目标层包括第二导电类型外延层;所述外延填充层和所述目标层构成超结结构。

技术总结本申请涉及一种半导体结构及其制造方法。该半导体结构的制造方法包括:形成目标层,目标层具有沟槽;于沟槽的内壁及目标层的表面形成阻挡层;自沟槽的底部至顶部方向分步执行多次外延填充工艺,直至沟槽内填充满外延填充层;其中,单次外延填充工艺包括:去除部分阻挡层,以至少裸露出沟槽的部分内壁;于沟槽的裸露内壁上形成外延填充层。本申请能够有效避免沟槽顶部封口问题以及外延填充层内部空洞问题,从而提升产品良率并提高器件的可靠性。技术研发人员:闫晓晖,周华,聂翔宇,江秋婷受保护的技术使用者:上海积塔半导体有限公司技术研发日:技术公布日:2024/12/2本文地址:https://www.jishuxx.com/zhuanli/20241204/342348.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。