使用多个二维沟道的晶体管结构的制作方法

- 国知局

- 2024-12-26 16:07:54

本申请涉及高电子迁移率晶体管(或hemt)领域,具体涉及包括多个异质结和多个二维电子气(2deg)层的hemt。

背景技术:

1、电子电路通常包括晶体管,其用作调节或控制部分电路中的电流流动的电子开关。一种类型的晶体管是场效应晶体管,其中电压被施加到栅极端子以导通和关断晶体管。半导体沟道区设置在漏极端子和源极端子之间。当晶体管导通时,电流流过源极端子和漏极端子之间的半导体沟道区。当晶体管关断时,较少或没有电流流过源极端子和漏极端子之间的半导体沟道区。栅极端子设置在源极端子和漏极端子之间的半导体沟道区上。栅极端子上的电压产生影响半导体沟道区是否传导电流的场,因此称为术语“场效应晶体管”。

2、传统上,硅被用于制造晶体管。然而,较宽带隙半导体材料可以用于制造传导更高功率并以比硅晶体管更高的效率操作的晶体管。碳化硅(sic)、氮化铝(aln)、氧化锌(zno)和氮化镓(gan)均是可以用于功率电子器件中的宽带隙半导体材料的实例。使用这种较宽带隙半导体材料的一种方式是形成两层不同的半导体材料,以在它们之间形成异质结。

3、这两种半导体材料可以具有充分不同的带隙,使得当聚集在一起时,接合的带隙刚好在沟道层内下降到费米能级以下。这意味着电子可以在该区域内自由流动。该区域在深度上较薄并且形成平行于沟道区的上表面的平面。因此,该区域被称为“2deg”区,以强调其平面形式。此外,由于该区域中电子的高迁移率,该区域也被称为“二维电子气”(或“2deg”)。因此,2deg是高度导电的。2deg可以形成功率半导体的沟道区,以允许高电流以相对低的电阻通过。

4、2deg可以在具有不同带隙和能带对准的某些半导体对的异质结构中形成。这些半导体对通常包括宽带隙材料和窄带隙材料。2deg的形成取决于材料的特定性质,诸如晶格常数、电子亲和力和能带偏移。

5、本文要求保护的主题不限于解决任何缺点或仅在诸如上述环境的环境中操作的实施方案。相反,提供本背景仅是为了说明可以实践本文描述的一些实施方案的一个示例性技术领域。

技术实现思路

1、提供本技术实现要素:是为了以简化形式介绍将在以下具体实施方式中进一步描述的一些概念。本发明内容并不旨在标识要求保护的主题的关键特征或必要特征,也并不旨在用于辅助确定要求保护的主题的范围。

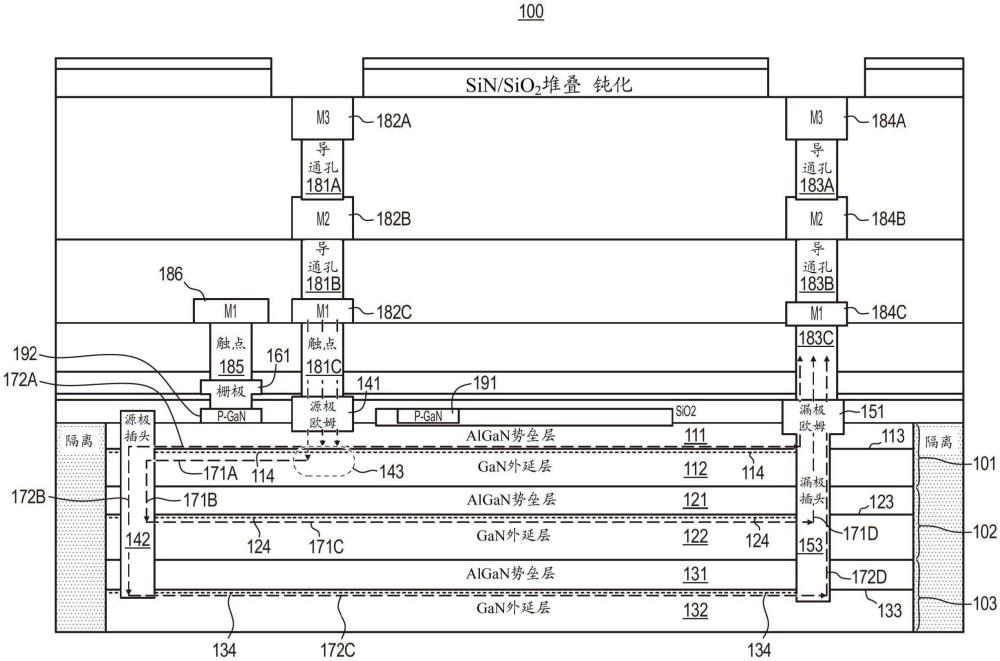

2、本文描述的实施方案涉及一种晶体管结构,其包括多个异质结层组。例如,第一异质结层组包括第一势垒半导体层和第一沟道半导体层,以及在第一势垒半导体层和第一沟道半导体层之间的界面处形成的第一异质结。第一异质结在第一沟道半导体层内诱导第一二维电子气(2deg)。第二异质结层组包括第二势垒半导体层和第二沟道半导体层,以及在第二势垒半导体层和第二沟道半导体层之间的界面处形成的第二异质结。第二异质结在第二沟道半导体层内诱导第二2deg。

3、源极触点在第一2deg的一部分处与第一2deg导电接触。另外,导电源极插头在第一2deg和第二2deg之间延伸,以便将第一2deg与第二2deg连接。栅极端子靠近第一2deg,使得施加到栅极端子的电压控制第一2deg在导电源极插头和第一2deg的与源极触点导电接触的部分之间是否连续。晶体管结构还具有漏极触点和从漏极触点延伸穿过第一异质结层组、穿过第一2deg并到达第二2deg的导电漏极插头。因此,当向栅极端子施加足以使第一2deg在导电源极插头和第一2deg的与源极触点导电接触的部分之间连续的电压时,经由第一2deg、导电源极插头、第二2deg和导电漏极插头在源极触点和漏极触点之间形成电流路径。

4、因此,晶体管结构可以利用在最表面水平2deg以下的一个或多个2deg中的导电路径,同时仍然允许刚好在最表面水平2deg以上的栅极控制。这有可能提供大量的技术益处,取决于子表面2deg的使用方式。例如,晶体管结构可以使用多个2deg在源极和漏极之间引导电流,从而显著降低导通电阻。此外,晶体管结构甚至可以对每个都共享源极和漏极的两个或多个独立可控晶体管执行功能。

5、另外的特征和优点将在以下描述中阐述,并且部分地将根据描述明显可见,或者可以通过实践本文的教导来获知。本发明的特征和优点可以通过所附权利要求中特别指出的仪器和组合来实现和获得。本发明的特征将根据以下描述和所附权利要求变得更明显可见,或者可以通过如下文阐述的实践本发明来获知。

技术特征:1.一种晶体管结构,其包括:

2.根据权利要求1所述的晶体管结构,所述电流路径是第一电流路径,所述晶体管还包括:

3.根据权利要求1所述的晶体管结构,所述导电源极插头比所述源极触点离所述导电漏极插头更远,所述栅极端子也比所述源极触点离所述导电漏极插头更远。

4.根据权利要求3所述的晶体管结构,所述电流路径是第一电流路径,所述栅极端子是第一栅极端子,所述晶体管结构还包括:

5.根据权利要求4所述的晶体管结构,所述第一栅极端子用于第一晶体管,并且所述第二栅极端子用于第二晶体管,所述第二晶体管与所述第一晶体管共享所述源极触点并且与所述第一晶体管共享所述漏极触点。

6.根据权利要求4所述的晶体管结构,其还包括:

7.根据权利要求4所述的晶体管结构,其还包括控制电路,所述控制电路被配置为:

8.根据权利要求4所述的晶体管结构,其还包括控制电路,所述控制电路被配置为:

9.根据权利要求1所述的晶体管结构,所述第一沟道半导体层由与所述第二沟道半导体层相同的半导体材料组成。

10.根据权利要求1所述的晶体管结构,所述第一势垒半导体层由与所述第二势垒半导体层相同的半导体材料组成。

11.根据权利要求1所述的晶体管结构,所述第一沟道半导体层由与所述第二沟道半导体层不同的半导体材料组成。

12.根据权利要求1所述的晶体管结构,所述第一势垒半导体层由与所述第二势垒半导体层不同的半导体材料组成。

13.根据权利要求1所述的晶体管结构,所述第一沟道半导体层是gan层,所述第一势垒半导体层是algan层。

14.根据权利要求1所述的晶体管结构,所述第一沟道半导体层是gan层,所述第一势垒半导体层是alingan层。

15.根据权利要求1所述的晶体管结构,所述第一沟道半导体层是gan层,所述第一势垒半导体层是alinn层。

16.根据权利要求1所述的晶体管结构,所述第一沟道半导体层是gaas层,所述第一势垒半导体层是algaas层。

17.根据权利要求1所述的晶体管结构,所述第一2deg和所述第二2deg是平行的。

18.根据权利要求1所述的晶体管结构,所述导电漏极插头垂直于所述第一2deg的平面和所述第二2deg的平面延伸。

19.根据权利要求16所述的晶体管结构,所述导电源极插头也垂直于所述第一2deg的平面和所述第二2deg的平面延伸。

20.根据权利要求1所述的晶体管结构,所述导电源极插头垂直于所述第一2deg的平面和所述第二2deg的平面延伸。

技术总结一种晶体管结构,其包括多个异质结层组,每个异质结层组产生二维电子气(2DEG),使得晶体管结构具有可以用于在源极和漏极之间传导的2DEG的堆叠。靠近最上面的2DEG提供端子,以控制最上面的2DEG在源极触点和源极插头之间是否连续。源极插头将最上面的2DEG与下一个2DEG连接,并且漏极插头也将最上面的2DEG与下一个2DEG连接。因此,栅极端子可以控制电流在源极和漏极之间的子表面2DEG中的流动。技术研发人员:马可·A·祖尼加,托马斯·威廉·麦塞尔威,维内特·乌尼,克劳迪奥·安德烈斯·卡尼萨雷斯受保护的技术使用者:英飞凌科技加拿大公司技术研发日:技术公布日:2024/12/12本文地址:https://www.jishuxx.com/zhuanli/20241216/348288.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。