半导体封装和包括其的半导体装置的制作方法

- 国知局

- 2025-01-10 13:11:24

本公开涉及将集成堆叠电容器(isc)嵌入基板堆积层中的方法以及具有嵌入基板堆积层中的isc的装置。

背景技术:

1、目前,多层陶瓷电容器(mlcc)是电子设备中生产和使用最多的电容器。由于电容器厚度限制(例如,>100μm),基板可以在基板表面上或在基板芯层处具有大的陶瓷电容器。由于陶瓷电容器的大厚度,这些电容器设置在堆积层的外部。

2、半导体封装可以是包含一个或更多个分立半导体器件或集成电路的金属、塑料、玻璃或陶瓷壳体。各个部件可以在被切割成管芯、测试并封装为半导体封装之前在半导体晶片(例如,硅晶片)上制造。半导体封装可以具有用于半导体封装内部的器件的引线或接触。

3、本背景技术部分中公开的信息在实现本申请的实施方式的过程之前或期间已经为发明人所知或由发明人导出,或者是在实现实施方式的过程中获取的技术信息。因此,它可以包含不构成公众已知的现有技术的信息。

技术实现思路

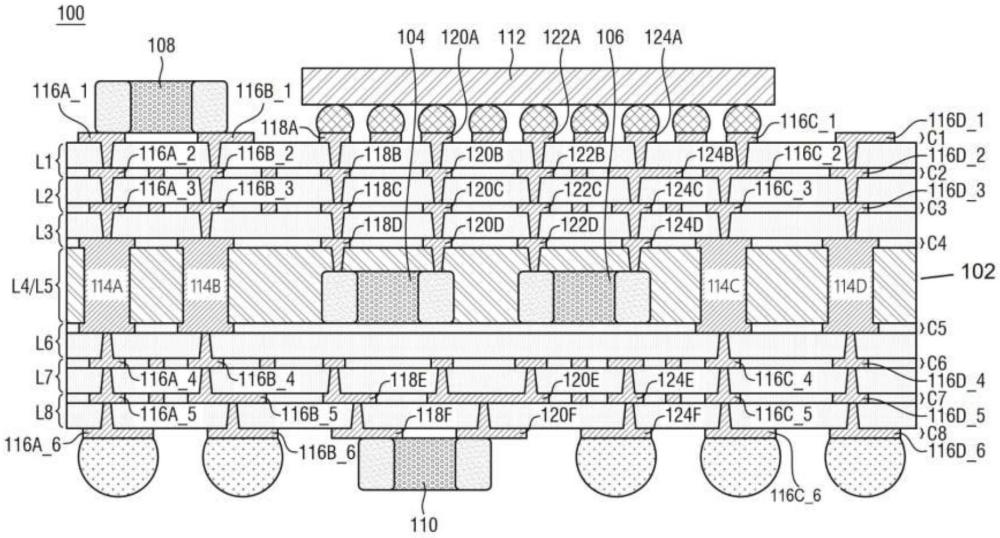

1、本公开的实施方式涉及形成半导体封装,其中集成堆叠电容器(isc)嵌入半导体封装中的基板堆积层中。半导体封装可以并入半导体装置(诸如电子设备(例如,手持式设备、计算机、平板电脑等))中。isc可以在基板制造工艺期间嵌入基板堆积层中。堆积层可以包含有源isc和无源isc两者,用于改善电介质厚度均匀性。

2、isc可以用铜布线形成在芯层上。isc可以形成在铜布线上或与铜布线相邻。可以在芯层上形成一个或更多个堆积层,使得isc和铜布线嵌入一个或更多个堆积层中。

3、本公开的实施方式可以导致基板厚度减小。例如,具有陶瓷电容器的常规半导体封装需要500μm厚的芯以允许电容器嵌入芯层中,而如果isc嵌入堆积层中,则本公开的实施方式具有约50μm的芯厚度。

4、本公开的实施方式为半导体封装提供了改善的电性能。例如,由于isc具有比陶瓷电容器小的厚度,因此所得的半导体封装具有高电容密度,从而导致改善的电性能。此外,半导体封装可以表现出改善的电性能,因为将isc放置在堆积层中导致isc更靠近硅。

5、本公开的实施方式提供了改善的电介质厚度均匀性。例如,堆积层中的isc的厚度可以匹配嵌入相同堆积层中的铜布线图案的厚度,从而使得isc能够用作半导体封装的不可能形成或放置铜的区域中的填充物(例如,虚设硅)。因此,本公开的实施方式改善了半导体封装电介质厚度均匀性的机械强度。

6、根据一个或更多个实施方式,一种形成半导体封装的方法包括形成芯层。该方法还包括在芯层上形成集成堆叠电容器(isc)。该方法还包括在芯层上形成一个或更多个堆积层,其中isc嵌入所述一个或更多个堆积层中。该方法还包括在芯层上形成一个或更多个金属层。

7、根据一个或更多个实施方式,一种半导体封装包括芯层。半导体封装还包括在芯层上的集成堆叠电容器(isc)。半导体封装包括在芯层上的一个或更多个堆积层,其中isc嵌入所述一个或更多个堆积层中。半导体封装包括在芯层上的一个或更多个金属层。

技术特征:1.一种半导体封装,包括:

2.根据权利要求1所述的半导体封装,其中所述一个或更多个金属层包括与所述芯层的表面接触的至少一个金属层,以及

3.根据权利要求2所述的半导体封装,其中所述一个或更多个堆积层包括覆盖所述电容器和所述至少一个金属层的至少一个堆积层。

4.根据权利要求2所述的半导体封装,其中所述电容器的厚度基本上等于所述至少一个金属层的厚度。

5.根据权利要求3所述的半导体封装,其中所述至少一个堆积层的厚度大于所述电容器的厚度。

6.根据权利要求4所述的半导体封装,其中所述至少一个堆积层的厚度大于所述电容器的所述厚度与所述至少一个金属层的所述厚度的组合。

7.根据权利要求1所述的半导体封装,还包括:

8.根据权利要求1所述的半导体封装,其中所述一个或更多个堆积层包括与所述芯层接触的第一堆积层和在所述第一堆积层上的第二堆积层,

9.根据权利要求1所述的半导体封装,其中所述电容器是有源电容器,以及其中所述半导体封装还包括:

10.根据权利要求1所述的半导体封装,其中所述一个或更多个金属层包括从由铜(cu)、铝(al)、钨(w)、钴(co)、钛(ti)、钽(ta)、钼(mo)和钌(ru)组成的组中选择的金属。

11.一种半导体封装,包括:

12.根据权利要求11所述的半导体封装,其中所述一个或更多个金属层包括与所述芯层的所述表面接触的至少一个金属层。

13.根据权利要求12所述的半导体封装,其中所述一个或更多个堆积层包括覆盖所述电容器和所述至少一个金属层的至少一个堆积层。

14.根据权利要求13所述的半导体封装,其中所述电容器的厚度基本上等于所述至少一个金属层的厚度,以及

15.根据权利要求11所述的半导体封装,还包括:

16.根据权利要求11所述的半导体封装,其中所述一个或更多个堆积层包括与所述芯层接触的第一堆积层和在所述第一堆积层上的第二堆积层,

17.根据权利要求11所述的半导体封装,其中所述电容器是有源电容器,以及其中所述半导体封装还包括:

18.根据权利要求11所述的半导体封装,其中所述一个或更多个金属层包括从由铜(cu)、铝(al)、钨(w)、钴(co)、钛(ti)、钽(ta)、钼(mo)和钌(ru)组成的组中选择的金属。

19.一种半导体装置,包括:

20.根据权利要求19所述的半导体器件,其中所述电容器是集成堆叠电容器(isc)。

技术总结本公开涉及半导体封装和包括其的半导体装置。该半导体封装包括芯层、在芯层上的集成堆叠电容器(ISC)、在芯层上的其中嵌入ISC的一个或更多个堆积层、以及在芯层上的一个或更多个金属层。技术研发人员:张睿,金炅洙,金又坪受保护的技术使用者:三星电子株式会社技术研发日:技术公布日:2025/1/6本文地址:https://www.jishuxx.com/zhuanli/20250110/351517.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。