异构集成数控延时器芯片及其制备方法与流程

- 国知局

- 2024-07-27 12:54:08

本申请属于集成电路,尤其涉及异构集成数控延时器芯片及其制备方法。

背景技术:

1、传统的数控延时器芯片为砷化镓工艺设计的二维平面拓扑结构。芯片内部由lc延时单元、开关网络等构成。因砷化镓工艺中lc的q值问题,当延时量大、位数多时,延时器芯片体现出插损大、面积大的特点。在射频前端中,砷化镓该特点制约系统使用。接收链路中,会制约系统噪声;发射链路中,会引起功耗增加。

技术实现思路

1、为克服相关技术中存在的数控延时器芯片尺寸大、功耗大的技术问题,本申请实施例提供了异构集成数控延时器芯片及其制备方法。

2、本申请是通过如下技术方案实现的:

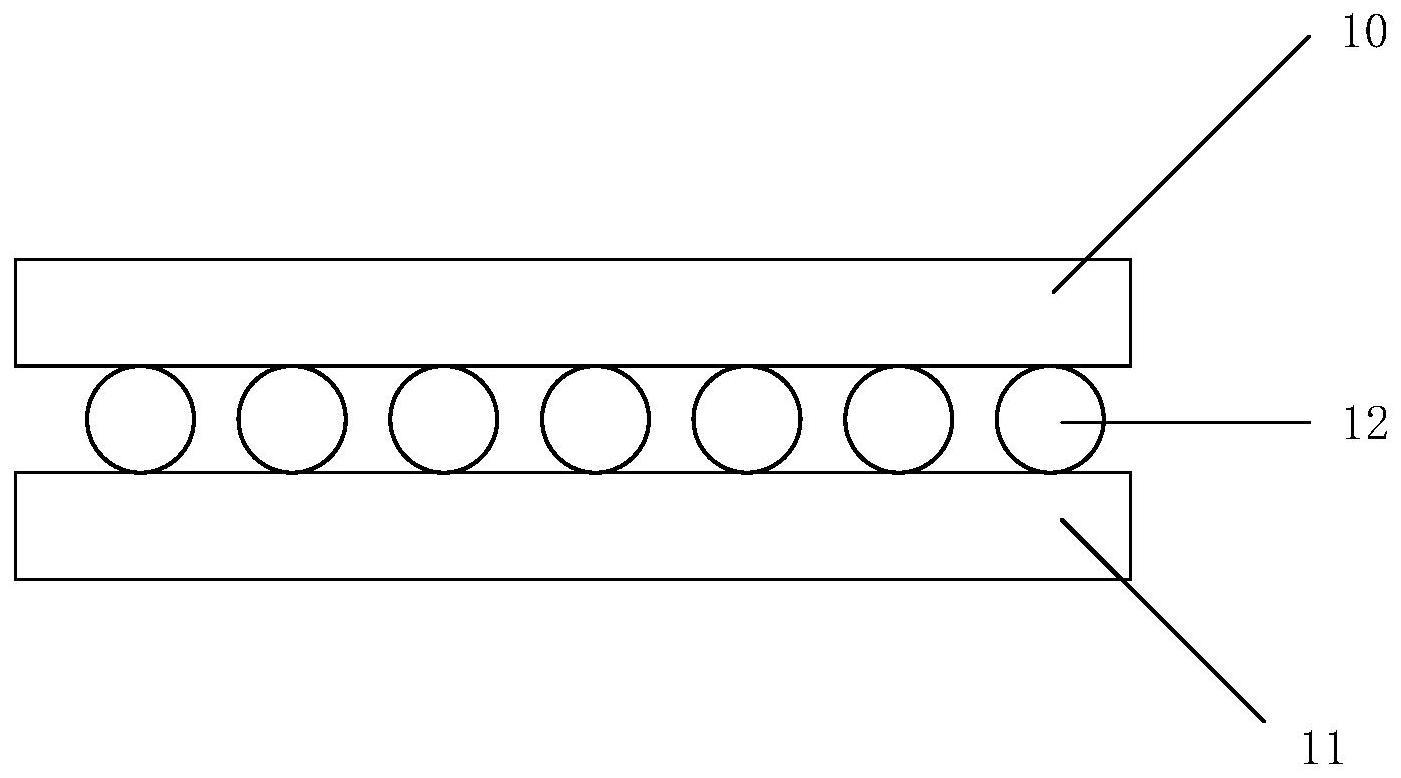

3、第一方面,本申请实施例提供了一种异构集成数控延时器芯片,包括:上层芯片和下层芯片;

4、上层芯片为硅基mems芯片,上层芯片中设置有延时电路和参考电路;

5、下层芯片为gaas芯片,下层芯片中设置有开关电路和驱动电路;

6、上层芯片和下层芯片连接,上层芯片位于下层芯片的正上方。

7、结合第一方面,在一些可能的实现方式中,上层芯片为单层硅基mems芯片或者双层硅基mems芯片,双层硅基mems芯片设置有双层硅基衬底,单层硅基mems芯片设置有一层硅基衬底。

8、结合第一方面,在一些可能的实现方式中,单层硅基mems芯片的硅基衬底厚度为390-410um,双层硅基mems芯片的硅基衬底厚度为780-820um。

9、结合第一方面,在一些可能的实现方式中,gaas芯片的砷化镓衬底厚度为70um。

10、结合第一方面,在一些可能的实现方式中,驱动电路为正压驱动电路或者ttl电平转换电路。

11、结合第一方面,在一些可能的实现方式中,上层芯片和下层芯片通过金金键合或者热压键合或者引线键合的方式连接。

12、结合第一方面,在一些可能的实现方式中,上层芯片和下层芯片通过通孔的方式连接。

13、第二方面,本申请实施例提供了一种异构集成数控延时器芯片制备方法,包括:

14、制备具有延时电路和参考电路的上层芯片,上层芯片为硅基mems芯片;

15、制备具有开关电路和驱动电路的下层芯片,下层芯片为gaas芯片;

16、将上层芯片和下层芯片进行连接,得到异构集成数控延时器芯片,上层芯片的上表面为异构集成数控延时器芯片的上表面,下层芯片的下表面为异构集成数控延时器芯片的下表面。结合第二方面,在一些可能的实现方式中,将上层芯片和下层芯片进行连接,得到异构集成数控延时器芯片,包括:上层芯片和下层芯片通过金金键合或者热压键合或者引线键合的方式连接。

17、结合第二方面,在一些可能的实现方式中,将上层芯片和下层芯片进行连接,得到异构集成数控延时器芯片,还包括:上层芯片和下层芯片通过通孔的方式连接。

18、可以理解的是,上述第二方面的有益效果可以参见上述第一方面中的相关描述,在此不再赘述。

19、本申请实施例与现有技术相比存在的有益效果是:

20、本申请通过将数控延时器芯片中的延时电路和参考电路设置于上层芯片、将数控延时器芯片中的开关电路和驱动电路设置于下层芯片的方式将占据空间的电路分散排布,缩小了各电路所占的平面面积,减小了数控延时器芯片的尺寸,即将传统的数控延时器芯片中设置于同一平面的四个电路根据其功能划分为两组,将两组电路放置于两个平面中,这两个平面在异构集成数控延时器芯片垂直的方向上平行,从俯视视角来看异构集成数控延时器芯片的尺寸比传统的数控延时器芯片的尺寸更小;下层芯片采用gaas芯片、上层芯片采用硅基mems芯片提高了数控延时器芯片的q值、减小了损耗、降低了功耗。

21、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本说明书。

技术特征:1.一种异构集成数控延时器芯片,其特征在于,包括:上层芯片和下层芯片;

2.如权利要求1所述的异构集成数控延时器芯片,其特征在于,所述上层芯片为单层硅基mems芯片或者双层硅基mems芯片,所述双层硅基mems芯片设置有双层硅基衬底,所述单层硅基mems芯片设置有一层硅基衬底。

3.如权利要求2所述的异构集成数控延时器芯片,其特征在于,所述单层硅基mems芯片的硅基衬底厚度为390-410um,所述双层硅基mems芯片的硅基衬底厚度为780-820um。

4.如权利要求1所述的异构集成数控延时器芯片,其特征在于,所述gaas芯片的砷化镓衬底厚度为70um。

5.如权利要求1所述的异构集成数控延时器芯片,其特征在于,所述驱动电路为正压驱动电路或者ttl电平转换电路。

6.如权利要求1所述的异构集成数控延时器芯片,其特征在于,所述上层芯片和所述下层芯片通过金金键合或者热压键合或者引线键合的方式连接。

7.如权利要求1所述的异构集成数控延时器芯片,其特征在于,所述上层芯片和所述下层芯片通过通孔的方式连接。

8.一种异构集成数控延时器芯片的制备方法,其特征在于,包括:

9.如权利要求8所述的异构集成数控延时器芯片的制备方法,其特征在于,所述将所述上层芯片和下层芯片进行连接,得到异构集成数控延时器芯片,包括:

10.如权利要求8所述的异构集成数控延时器芯片的制备方法,其特征在于,所述将所述上层芯片和下层芯片进行连接,得到异构集成数控延时器芯片,还包括:

技术总结本申请适用于集成电路技术领域,提供了异构集成数控延时器芯片及其制备方法,该异构集成数控延时器芯片包括:上层芯片和下层芯片;上层芯片为硅基MEMS芯片,上层芯片中设置有延时电路和参考电路;下层芯片为GaAs芯片,下层芯片中设置有开关电路和驱动电路;上层芯片和下层芯片连接,上层芯片位于下层芯片的正上方。本申请缩小了数控延时器芯片的尺寸的同时减小了功耗。技术研发人员:常萌,郭跃伟,段磊,卢啸,黎荣林,孔令旭受保护的技术使用者:河北博威集成电路有限公司技术研发日:技术公布日:2024/1/12本文地址:https://www.jishuxx.com/zhuanli/20240726/124044.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表