一种MEMS器件的封装方法及MEMS器件与流程

- 国知局

- 2024-07-27 13:05:45

本申请涉及微机电,具体涉及一种mems器件的封装方法及mems器件。

背景技术:

1、mems(micro electro mechanical system,微机电系统)器件通常由mems芯片(又称器件芯片)和asic(application specific integrated circuit,专用集成电路)芯片(又称控制芯片)组成,例如,mems器件可以包括振荡器、陀螺仪、加速度计等类型。

2、目前的mems器件主要通过引线键合等封装方式实现器件芯片和控制芯片之间的电互连,由于引线键合通常需要留有用于引线的空间,而且通常利用塑料或陶瓷对整体进行包装,导致封装尺寸相比控制芯片大得多,难以实现封装尺寸的小型化,并且由于整体包装,导致mems器件的散热性能也较差。

技术实现思路

1、针对上述技术问题,本申请提供一种mems振荡器,可以改善现有mems振荡器温度补偿不够精确的问题。

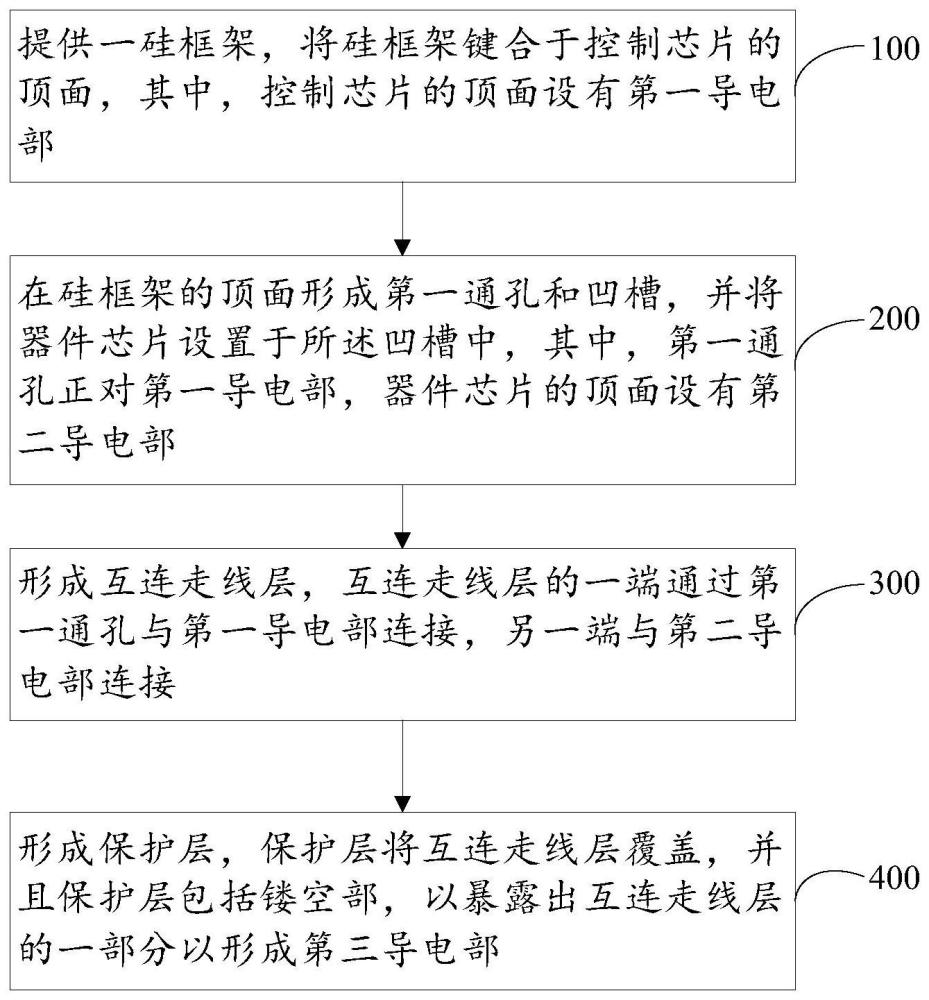

2、为解决上述技术问题,第一方面,本申请实施例提供一种mems器件的封装方法,包括:

3、提供一硅框架,将所述硅框架键合于控制芯片的顶面,其中,所述控制芯片的顶面设有第一导电部;

4、在所述硅框架的顶面形成第一通孔和凹槽,并将器件芯片设置于所述凹槽中,其中,所述第一通孔正对所述第一导电部,所述器件芯片背离所述控制芯片的顶面设有第二导电部;

5、形成互连走线层,所述互连走线层的一端通过所述第一通孔与所述第一导电部连接,另一端与所述第二导电部连接;

6、形成保护层,所述保护层将所述互连走线层覆盖,并且所述保护层包括镂空部,以暴露出所述互连走线层的一部分以形成第三导电部。

7、可选地,所述形成互连走线层,具体包括:

8、形成第一绝缘层,所述第一绝缘层覆盖所述第一通孔的侧壁、所述硅框架的顶面以及所述器件芯片的顶面;

9、填充所述第一通孔,以形成与所述第一导电部连接的第一导电线;

10、在所述第一绝缘层的顶部形成第二导电线,所述第二导电线一端与所述第一导电线连接,另一端贯穿所述第一绝缘层与所述第二导电部连接。

11、可选地,所述在所述第一通孔中形成与所述第一导电部连接的第一导电线之后,还包括:

12、形成第二绝缘层,所述第二绝缘层覆盖所述第一绝缘层和所述第一导电线的顶部;

13、所述在所述第一绝缘层的顶部形成第二导电线,具体包括:

14、由所述第二绝缘层向下进行刻蚀形成第二通孔和第三通孔,其中,所述第二通孔暴露出所述第一导电线的顶部,所述第三通孔暴露出所述第二导电部;

15、在所述第二绝缘层的顶面形成所述第二导电线,所述第二导电线的一端通过所述第二通孔与所述第一导电线的顶部连接,另一端通过所述第三通孔与所述第二导电部连接。

16、可选地,所述器件芯片与所述凹槽的侧壁之间设有间隙;

17、所述第一绝缘层还填充所述间隙。

18、可选地,所述形成保护层之后,还包括:

19、在所述镂空部形成与所述第三导电部连接的基底金属层;以及,

20、在所述基底金属层上形成焊球。

21、可选地,所述硅框架的顶面形成有至少两个所述凹槽,以及多个与所述凹槽对应的所述第一通孔;

22、所述器件芯片设置有至少两个,并且与所述凹槽一一对应。

23、第二方面,本申请还提供一种mems器件,包括:

24、控制芯片,其顶面设有第一导电部;

25、硅框架,键合于所述控制芯片的顶面,所述硅框架的顶面设有第一通孔和凹槽,并且所述第一通孔正对所述第一导电部;

26、器件芯片,设置于所述凹槽中,所述器件芯片的顶面设有第二导电部;

27、互连走线层,由所述第一通孔延伸至所述硅框架的顶部,将所述第一导电部和所述第二导电部连接导通;

28、保护层,覆盖所述互连走线层,并且所述保护层包括镂空部,以暴露出所述互连走线层的一部分以形成第三导电部。

29、可选地,所述mems器件还包括第一绝缘层,所述第一绝缘层覆盖所述第一通孔的侧壁、所述硅框架的顶面以及所述器件芯片的顶面;

30、所述互连走线层包括填充所述第一通孔并与所述第一导电部连接的第一导电线,以及设置在所述第一绝缘层的顶部的第二导电线,所述第二导电线一端与所述第一导电线连接,另一端贯穿所述第一绝缘层与所述第二导电部连接,其中,所述第一导电线配合所述第一绝缘层完全填充所述第一通孔。

31、可选地,所述mems器件还包括第二绝缘层,所述第二绝缘层覆盖所述第一绝缘层和所述第一导电线的顶部;

32、所述第二绝缘层上设有第二通孔和第三通孔,其中,所述第二通孔暴露出所述第一导电线的顶部,所述第三通孔同时贯穿所述第一绝缘层以暴露出所述第二导电部;

33、所述第二导电线设置于所述第二绝缘层的顶面,所述第二导电线的一端通过所述第二通孔与所述第一导电线的顶部连接,另一端通过所述第三通孔与所述第二导电部连接。

34、可选地,所述硅框架的顶面形成有至少两个所述凹槽,以及多个与所述凹槽对应的所述第一通孔;

35、所述器件芯片设置有至少两个,并且与所述凹槽一一对应。

36、如上所述,本申请的mems器件,控制芯片的顶面键合硅框架,硅框架上设有第一通孔和凹槽,器件芯片设置于硅框架的凹槽中,互连走线层一端通过第一通孔与控制芯片的第一导电部连接,另一端与器件芯片的第二导电部连接,从而实现控制芯片和器件芯片的电连接。本申请的mems器件的整体结构是以控制芯片为基底向上堆叠,整体封装结构的尺寸可以与控制芯片的尺寸大致一致,从而实现了封装结构的小型化;而且控制芯片运行产生的热能可以经由硅框架快速散发,从而可以改善mems器件的散热性能。本申请的mems器件的封装结构为晶圆级封装,能够有效降低封装成本。

技术特征:1.一种mems器件的封装方法,其特征在于,包括:

2.根据权利要求1所述的封装方法,其特征在于,所述形成互连走线层,具体包括:

3.根据权利要求2所述的封装方法,其特征在于,所述在所述第一通孔中形成与所述第一导电部连接的第一导电线之后,还包括:

4.根据权利要求2所述的封装方法,其特征在于,所述器件芯片与所述凹槽的侧壁之间设有间隙;

5.根据权利要求1所述的封装方法,其特征在于,所述形成保护层之后,还包括:

6.根据权利要求1-5任一项所述的封装方法,其特征在于,所述硅框架的顶面形成有至少两个所述凹槽,以及多个与所述凹槽对应的所述第一通孔;

7.一种mems器件,其特征在于,包括:

8.根据权利要求7所述的mems器件,其特征在于,还包括第一绝缘层,所述第一绝缘层覆盖所述第一通孔的侧壁、所述硅框架的顶面以及所述器件芯片的顶面;

9.根据权利要求8所述的mems器件,其特征在于,还包括第二绝缘层,所述第二绝缘层覆盖所述第一绝缘层和所述第一导电线的顶部;

10.根据权利要求7-9任一项所述的mems器件,其特征在于,所述硅框架的顶面形成有至少两个所述凹槽,以及多个与所述凹槽对应的所述第一通孔;

技术总结本申请公开了一种MEMS器件的封装方法及MEMS器件,封装方法包括:提供一硅框架,将硅框架键合于控制芯片的顶面,其中,控制芯片的顶面设有第一导电部;在硅框架的顶面形成第一通孔和凹槽,并将器件芯片设置于凹槽中,其中,第一通孔正对第一导电部,器件芯片的顶面设有第二导电部;形成互连走线层,互连走线层的一端通过第一通孔与第一导电部连接,另一端与第二导电部连接;形成保护层,保护层将互连走线层覆盖,并且保护层包括镂空部,以暴露出互连走线层的一部分以形成第三导电部。本申请以控制芯片为基底向上堆叠,器件的尺寸可以与控制芯片大致一致,实现了封装结构的小型化;而且热能可以经由硅框架快速散发,从而可以改善散热性能。技术研发人员:朱怀远,高建章,林友玲,郭姝受保护的技术使用者:麦斯塔微电子(上海)有限公司技术研发日:技术公布日:2024/6/2本文地址:https://www.jishuxx.com/zhuanli/20240726/124878.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。