半导体器件的制作方法与流程

- 国知局

- 2024-07-27 13:05:46

本申请涉及半导体,具体涉及一种半导体器件的制作方法。

背景技术:

1、惯性传感器是用于主要检测和测量加速度、倾斜、冲击、振动、旋转和多自由度(degrees offreedom,dof)运动的器件,是解决导航、定向和运动载体控制的重要部件。

2、在惯性传感器的制作工艺过程中,需要在半导体膜层上进行刻蚀以形成宽度不同的间隙,从而形成支撑梁和梳齿结构等。然而,由于间隙的宽度大小不同,在蚀刻工艺过程中,容易出现负载效应,相较于宽度较小的间隙,宽度较大的间隙可以更早地蚀刻到目标位置。为了使得宽度较小的间隙能够蚀刻到目标位置,还需继续进行蚀刻,这会导致宽度较大的间隙的侧壁底部受到间隙底部反溅的影响而出现弧形侧壁,也即对宽度较大的间隙造成了过蚀刻,导致宽度较大的间隙与宽度较小的间隙之间的结构两侧蚀刻程度不一致,容易造成该结构的倾斜,影响器件性能。

3、因此,需要一种新的制作方法,以解决上述技术问题。

技术实现思路

1、在技术实现要素:部分中引入了一系列简化形式的概念,这将在具体实施方式部分中进一步详细说明。本申请的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

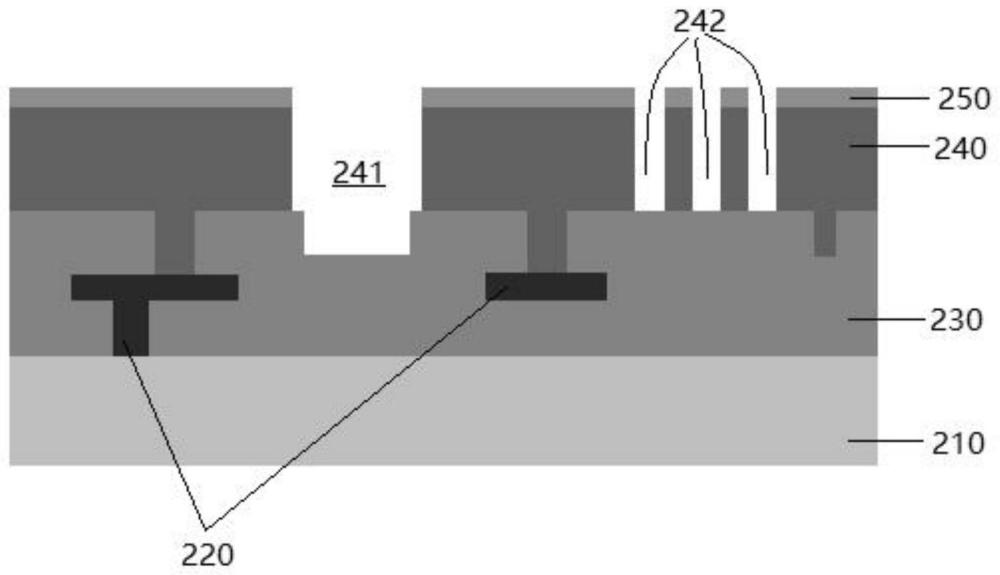

2、针对目前存在的问题,本申请提供一种半导体器件的制作方法,包括:提供一衬底;在所述衬底上形成布线层和牺牲层,所述牺牲层覆盖所述衬底和所述布线层;在所述牺牲层中形成第一沟槽,所述第一沟槽在所述衬底上的正投影与所述布线层在所述衬底上的正投影不重叠;在所述牺牲层上形成功能层,所述功能层填满所述第一沟槽且覆盖所述牺牲层的上表面;在所述功能层中形成第二沟槽,所述第二沟槽贯穿所述功能层且所述第二沟槽露出至少部分所述第一沟槽。

3、在一实施例中,所述第二沟槽在所述衬底上的正投影覆盖所述第一沟槽在所述衬底上的正投影。

4、在一实施例中,所述第二沟槽在所述衬底上的正投影与所述第一沟槽在所述衬底上的正投影完全重叠。

5、在一实施例中,所述第二沟槽的宽度不小于所述第一沟槽的宽度。

6、在一实施例中,还包括:在所述牺牲层中形成第三沟槽,所述第三沟槽在所述衬底上的正投影与所述布线层在所述衬底上的正投影至少部分重叠;所述功能层还填满所述第三沟槽。

7、在一实施例中,所述第三沟槽的底部暴露至少部分的所述布线层。

8、在一实施例中,所述第一沟槽的深度小于所述第三沟槽的深度。

9、在一实施例中,还包括:执行一蚀刻工艺,在所述功能层上同时形成所述第二沟槽和第四沟槽,所述第四沟槽的宽度小于所述第二沟槽的宽度。

10、在一实施例中,还包括:在所述衬底上形成所述牺牲层之后且在形成所述第一沟槽之前,对所述牺牲层的上表面执行一抛光工艺。

11、在一实施例中,还包括:在所述功能层上形成所述第二沟槽之后,移除部分所述牺牲层。

12、通过优化牺牲层的图案,在牺牲层上与间隙对应的位置蚀刻出第一沟槽,并在第一沟槽中填满功能层的材料,在间隙的位置补偿一定深度的功能层材料,可以在功能层形成间隙的工艺过程中,也即在对第二沟槽进行过蚀刻时,有效避免底部反溅对第二沟槽的侧壁的过蚀刻,也即避免反溅对间隙的侧壁的过蚀刻,能够得到平直的间隙侧壁,从而获得优良的器件性能。

技术特征:1.一种半导体器件的制作方法,其特征在于,包括:

2.根据权利要求1所述的半导体器件的制作方法,其特征在于,所述第二沟槽在所述衬底上的正投影覆盖所述第一沟槽在所述衬底上的正投影。

3.根据权利要求1所述的半导体器件的制作方法,其特征在于,所述第二沟槽在所述衬底上的正投影与所述第一沟槽在所述衬底上的正投影完全重叠。

4.根据权利要求1所述的半导体器件的制作方法,其特征在于,所述第二沟槽的宽度不小于所述第一沟槽的宽度。

5.根据权利要求1所述的半导体器件的制作方法,其特征在于,还包括:

6.根据权利要求5所述的半导体器件的制作方法,其特征在于,所述第三沟槽的底部暴露至少部分的所述布线层。

7.根据权利要求5所述的半导体器件的制作方法,其特征在于,所述第一沟槽的深度小于所述第三沟槽的深度。

8.根据权利要求1所述的半导体器件的制作方法,其特征在于,还包括:

9.根据权利要求1所述的半导体器件的制作方法,其特征在于,还包括:

10.根据权利要求1所述的半导体器件的制作方法,其特征在于,还包括:

技术总结本申请提供一种半导体器件的制作方法,包括:提供一衬底;在所述衬底上形成布线层和牺牲层,所述牺牲层覆盖所述衬底和所述布线层;在所述牺牲层中形成第一沟槽,所述第一沟槽在所述衬底上的正投影与所述布线层在所述衬底上的正投影不重叠;在所述牺牲层上形成功能层,所述功能层填满所述第一沟槽且覆盖所述牺牲层的上表面;在所述功能层中形成第二沟槽,所述第二沟槽贯穿所述功能层且所述第二沟槽露出至少部分所述第一沟槽。利用本申请的制作方法,能够得到具有平直的间隙侧壁的半导体器件,该半导体器件具有优良的性能。技术研发人员:任杨波,杨帆,徐达武受保护的技术使用者:芯联集成电路制造股份有限公司技术研发日:技术公布日:2024/6/2本文地址:https://www.jishuxx.com/zhuanli/20240726/124879.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表