一种自启动并提高PSRR的LDO电路的制作方法

- 国知局

- 2024-07-30 09:25:39

本发明属于电源管理芯片,涉及一种自启动并提高电源抑制比(powersupply rejection ratio,称psrr)的ldo电路。

背景技术:

1、请参阅图1,图1所示为一种传统的带隙基准电路的示意图。如图1所示,该电路可以包含启动电路模块、第一级基准模块、预稳压低压差线性稳压器和第二级基准模块。启动电路模块用于基于输入电压和使能信号,输出第一启动电压vstart1;第一级基准模块用于基于所述输入电压vin、所述第一启动电压vstart1、所述使能信号en和第一电压信号vh,输出第一级基准电压vbgef和第二启动电压vstart2;预稳压低压差线性稳压器用于基于所述输入电压lvdd、所述第一级基准电压和所述使能信号en,输出第二电压信号lvdd;第二级基准模块用于基于所述第二电压信号lvdd、所述第二启动电压vstart2和所述使能信号en,输出所述第一电压信号和第二级基准电压vbg;其中,第一级基准电压vbgef的精度psrr小于第二级基准电压的精度vbg的psrr。

2、上述带隙基准电路控制方法,其可以包括:

3、首先,基于使能信号en和所述输入电源电压vin,启动启动电路模块,启动电路模块对第一级基准模块注入初始电流,使得第一级基准模块摆脱零状态;

4、然后,通过所述第一级基准模块产生第一级基准电压,作为预稳压低压差线性稳压器的输入参考电压,通过所述第一级基准模块为第二级基准模块提供摆脱零状态的第二启动电压;

5、最后,预稳压低压差线性稳压器基于第一级基准电压,产生能够抑制电源噪声的第二电压信号,通过所述第二电压信号为所述第二级基准模块供电,使得所述第二级基准模块产生第二级基准电压;其中,所述第一级基准电压的psrr小于所述第二级基准电压的psrr。

6、然而,上述带隙基准电路及其控制方法具有如下不足:

7、①、所述第二电压信号lvdd的抑制电源噪声的能力有限,受制于第一级基准电压的psrr,导致所述第二电压信号lvdd的psrr不高;

8、②、由于第二电压信号lvdd的psrr不高,所以导致最后的基准电压vbg的psrr受到限制,缺乏提升空间;

9、③、所述整个电路包括启动电路,两级基准电路,和一个预稳压低压差线性稳压器,电路多且复杂,版图面积大。

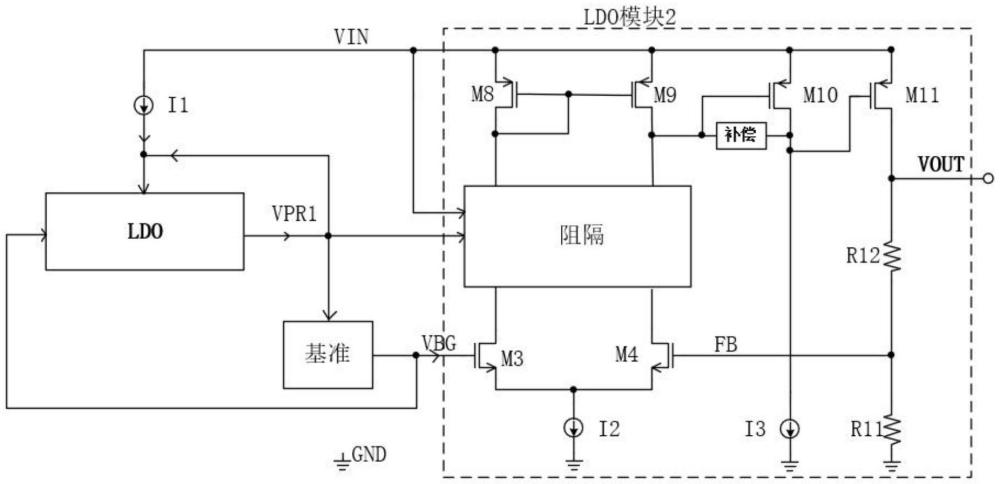

10、请参阅图2,图2所为现有技术中ldo架构示意图。如图2所示,该电路包括五管运算放大器(第一级放大器)、第二级放大器、第三级放大器、补偿单元和分压电阻构成;五管运算放大器(第一级放大器)由晶体管m3、晶体管m4、晶体管m8、晶体管m9和电流镜i1构成,第二级放大器为晶体管m10,第三级放大器为晶体管m11。该ldo架构内部的环路是负反馈环路,能够维持vout处于稳定状态;基于输入基准电压vbg和分压电阻,输出vout;vout=vbg*(r1+r2)/r1。

11、上述ldo架构的缺点:

12、①、所述基准模块基于vin供电,输出基准电压vbg;则基准电压vbg与vin相关,易受vin噪声干扰,则所述vbg的psrr不高;

13、②、vin较高时,差分对管m3和m4的vds很大,会导致差分对管m3和m4因为热载流子注入效应而漏电。对于低压工艺器件,vin越大,热载流子注入效应越大;热载流子注入效应导致所述运算放大器的工作状态受到影响,进而影响整个环路的工作状态,从而导致输出vout的psrr随vin增大而降低。

14、③、差分对管m3和m4的vd=vin-vgsm8;vin扰动时,vin的噪声可以轻易通过晶体管m8到达差分对管m3和m4的漏极,再通过差分对管m3和m4的栅漏寄生电容耦合至vbg和fb,从而降低vbg和fb的psrr,最终导致输出vout的psrr降低。

15、如果将上述现有技术1中的基准模块代替现有技术2中的基准模块,有利于提高最后的输出vout的psrr,但是由于,现有技术1的基准的psrr受到限制,以及传统ldo架构内部的问题,最终输出vout的psrr还是不高;即两个现有技术结合之后,结构的缺点为:

16、①、由于现有技术1中第二电压信号lvdd的psrr不高,导致基准电压vbg的psrr受到限制,最终的vout的psrr也会受到限制。

17、②、在上述ldo架构中,差分对管m3和m4的栅漏寄生电容耦合vin噪声至基准和fb,导致基准的psrr进一步降低,最终vout的psrr进一步降低。

18、③、由于低压工艺,热载流子注入效应影响所述负反馈环路的工作状态,也降低vout的psrr。

19、④、此外,所述现有技术1中使用较多电路模块,电路面积较大。

技术实现思路

1、为解决的上述技术问题,本发明提出一种自启动并具有高psrr的ldo电路,具有对电源呈现高噪声抑制能力的技术方案。

2、为实现上述目的,本发明的技术方案如下:

3、一种自启动并具有高psrr的ldo电路,其包括输入电源vin、电路输出端vout和基准电压vbg;其特征在于,还包括第一ldo模块、输出基准电压vbg的基准模块、电流源i1和第二ldo模块;

4、所述输入电源vin给第二ldo模块供电并提供第一偏置电压,并通过所述电流源i1为第一ldo模块和基准模块工作提供基础电流;

5、所述第一ldo模块基于输入信号vbg,产生供电电源vpr1;所述供电电源vpr1作为第一ldo模块、所述基准模块的输入供电电源,维持所述第一ldo模块正常工作;所述供电电压vpr1又作为第二ldo模块的第二偏置电压;所述基准模块输出所述基准电压vbg到所述第一ldo模块和第二ldo模块;

6、所述第一ldo的供电电源vpr1、第一ldo模块和输入供电电源vpr1构成一个闭环系统;所述第一ldo模块和基准模块构成第二个闭环系统;

7、所述第二ldo模块包括阻隔单元、晶体管m3、晶体管m4、晶体管m8、晶体管m9、晶体管m10、晶体管m11、电阻r11、电阻r12、电流源i2和电流源i3;所述阻隔单元用于阻隔所述输入电源vin噪声耦合到基准电压vbg;

8、其中,所述晶体管m8、晶体管m9、晶体管m10、晶体管m11的源极接输入电源vin,输入电源vin给阻隔单元供电并提供第一偏置电压,所述供电电源vpr1也给所述阻隔单元提供第二偏置电压;所述晶体管m8和晶体管m9的栅极以及所述晶体管m8连接在一起输入所述阻隔单元;所述晶体管m3和所述晶体管m4的漏极分别接所述阻隔单元的两个输出端;所述晶体管m3的栅极接所述基准电压vbg;所述晶体管m4的栅极接电阻r12和电阻r11的连接点fb;所述电流源i2接在所述晶体管m3和所述晶体管m4的源极和接地端之间;所述阻隔单元与所述晶体管m9的漏极、所述晶体管m10的栅极连接在一起;所述电流源i3的输出端接地;所述晶体管m11漏极和电阻r12的另一端连接在输出端vout;所述电阻r11的另一端接地。

9、进一步地,所述输入电源vin为外部输入电源。

10、进一步地,所述阻隔单元包括晶体管m5、晶体管m51、晶体管m71和晶体管m7;

11、其中,所述晶体管m71的栅极和晶体管m7的栅极接输入电源vin;所述晶体管m8和晶体管m9的栅极以及所述晶体管m8和所述晶体管m7的漏极连接在一起;所述晶体管m7的源极接所述晶体管m5的漏极;所述晶体管m71的源极接所述晶体管m51的漏极;所述晶体管m5和所述晶体管m51的栅极接供电电源vpr1;所述晶体管m5的源极接所述晶体管m3的漏极;所述晶体管m51的源极接所述晶体管m4的漏极;所述晶体管m9和晶体管m71的漏极、所述晶体管m10的栅极连接在一起。

12、进一步地,所述阻隔单元包括晶体管m5、晶体管m51、晶体管m61、晶体管m6、晶体管m71和晶体管m7;

13、其中,所述晶体管m71的栅极和晶体管m7的栅极接输入电源vin;所述晶体管m8和晶体管m9的栅极以及所述晶体管m8和所述晶体管m7的漏极连接在一起;所述晶体管m7的源极接所述晶体管m5的漏极;所述晶体管m71的源极接所述晶体管m51的漏极;所述晶体管m5和所述晶体管m51的栅极接供电电源vpr1端;所述晶体管m5的源极接所述晶体管m6的漏极;所述晶体管m51的源极接所述晶体管m61的漏极;所述晶体管m6的源极接所述晶体管m3的漏极;所述晶体管m6和所述晶体管m61的栅极接第三偏置电压vp1;所述晶体管m51的源极接所述晶体管m4的漏极;所述晶体管m9和晶体管m71的漏极、所述晶体管m10的栅极连接在一起;其中,所述第二偏置电压vpr1大于第三偏置电压vp1。

14、进一步地,所述第一ldo模块包括运算放大器ea、源极跟随器m1、晶体管开关m2、电阻r1、电阻r2和电阻r3;所述输入电源vin通过电流源i1给所述第一ldo模块的运算放大器ea、源极跟随器m1的源极和电阻r1的一端供电;所述电阻r1、电阻r2和电阻r3串接在所述第一ldo模块的供电端和接地端之间;所述运算放大器ea的正输入端接所述基准电压vbg;所述运算放大器ea的负输入端接所述电阻r2和电阻r3连接点v1,所述晶体管开关m2的栅极接所述电阻r1和电阻r2的连接点v3;所述源极跟随器m1和晶体管开关m2漏极连接在一起;所述源极跟随器m1的栅极接所述运算放大器ea的输出端v2。

15、进一步地,所述基准模块包括晶体管m12和晶体管m13;所述晶体管m12的漏极接所述供电电源vpr1,所述晶体管m12的源极和栅极、所述晶体管m13的栅极和漏极、以及晶体管m3的栅极连接在基准电压vbg,所述晶体管m13的源极连接接地端gnd。

16、进一步地,所述基准模块包括晶体管m12、晶体管m13、晶体管m14和晶体管m15;所述晶体管m13和所述晶体管m15的源极接所述供电电源vpr1,所述晶体管m13的栅极和漏极、晶体管m12的漏极以及所述晶体管m15的栅极连接在一起,所述晶体管m12的源极和栅极接接地端gnd,所述晶体管m14的源极连接接地端gnd;所述晶体管m14的漏极和栅极源极接在所述基准电压vbg。

17、进一步地,所述的自启动并具有高psrr的ldo电路,其还包括补偿单元,其连接在所述晶体管m9的漏极和晶体管m10的漏极之间;用于对所述第二ldo模块中的三级放大器的相位裕度进行补偿。

18、从上述技术方案可以看出,本发明提出的自启动并具有高psrr的ldo电路,具有如下有益效果:

19、①、使用电流源为启动电路提高初始条件,在基础的ldo架构基础上,只增加一个nmos管,和其余器件配合做启动电路,不需要增加额外的启动支路,节省面积;

20、②、使用内部电源给ldo模块供电,与用外部输入电源vin给ldo模块供电相比,能够极大提高内部电源电压供电电源vpr1的psrr;从而提高基准的psrr;内部电源由ldo调节产生,不需要额外的预降压电路;

21、③、基准模块产生的基准电压直接作ldo的输入参考电压,不需要额外增加第一级基准模块,节省面积;

22、④、阻隔单元隔断输入电源vin噪声通过差分对管耦合到基准的通路,使得基准的psrr不受影响。

23、⑤、钳位差分对管的漏级电压,让差分对管的热载流子注入效应减弱而漏电减小,使得运算放大器工作不受vin变化影响,并维持基准的高psrr,最终能够得到高psrr的vout。

本文地址:https://www.jishuxx.com/zhuanli/20240730/149415.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

控制设备和控制方法与流程

下一篇

返回列表