用于功率半导体器件的边缘端接及相关的制造方法与流程

- 国知局

- 2024-07-31 18:54:19

本公开涉及功率半导体器件及制造此类器件的方法。

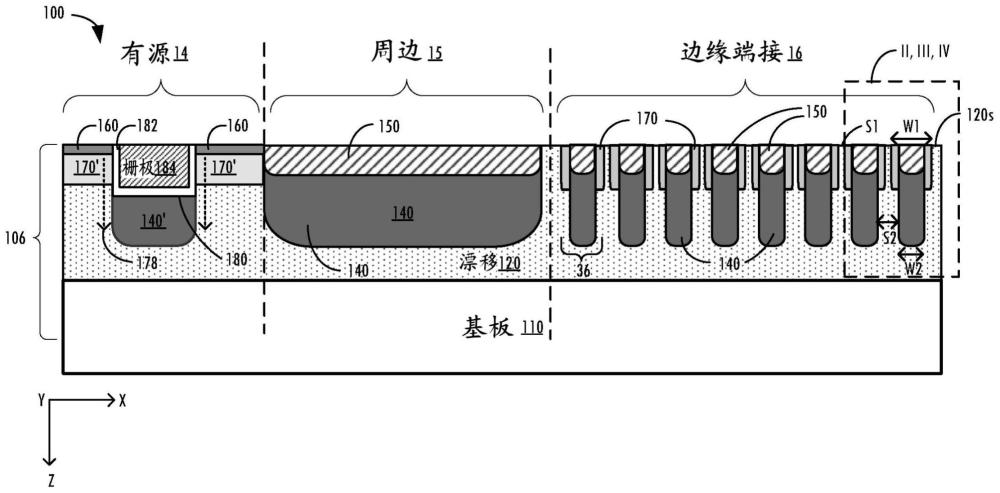

背景技术:

1、功率半导体器件被用于携带大电流并支持高电压。本领域中可以使用各种各样的功率半导体器件,包括例如功率金属氧化物半导体场效应晶体管(mosfet)、双极结型晶体管(bjt)、绝缘栅双极晶体管(igbt)、结型势垒肖特基二极管、栅极关断晶体管(gto)、mos控制的晶闸管以及各种其他器件。这些功率半导体器件一般由宽带隙半导体材料制成,诸如基于碳化硅(sic)或氮化镓(gan)的半导体材料。在本文中,宽带隙半导体材料是指带隙大于大约1.40ev(例如大于大约2ev)的半导体材料。

2、功率半导体器件可以具有横向结构或垂直结构。在具有横向结构的器件中,器件的端子(例如,用于功率mosfet器件的漏极、栅极和源极端子)位于半导体层结构的同一主表面(例如,顶部或底部)上。相比之下,在具有垂直结构的器件中,半导体层结构的每个主表面上都提供至少一个端子。例如,在垂直mosfet器件中,源极可以位于半导体层结构的顶表面上,而漏极可以位于半导体层结构的底表面上。作为另一个示例,功率肖特基二极管通常具有垂直结构,其中阳极触件在半导体层结构的第一主表面(例如,顶表面)上形成,而阴极触件在另一个主表面(例如,底表面)上形成。垂直结构通常用在非常高功率的应用中,因为垂直结构允许厚的半导体漂移层或区域,其可以支持高电流密度并阻挡高电压。半导体层结构可以包括或不包括底层基板。在本文中,术语“半导体层结构”是指包括一个或多个半导体层的结构,诸如半导体基板和/或半导体外延层。

3、包括mosfet晶体管的垂直功率半导体器件可以具有标准栅极电极设计,其中晶体管的栅极电极在半导体层结构的顶部形成,或者,可替代地,栅极电极可以埋在半导体层结构内的沟槽中。具有埋置的栅极电极的mosfet通常被称为栅极沟槽mosfet。对于标准栅极电极设计,每个单位单元晶体管的沟道区域水平部署在栅极电极下方。相比之下,在栅极沟槽mosfet设计中,沟道垂直部署。例如,由于通过在沟槽的侧壁上实现沟道区域来获得相对窄的单元节距,sic沟槽mosfet可以提供固有的较低比导通电阻。沟槽侧壁上的沟道移动性也可以显著(例如,两到四倍)大于平面si面,从而导致增强的电流密度。因此,栅极沟槽mosfet可以提供增强的性能,但通常要求更复杂的制造工艺。

4、更一般地,常规功率半导体器件通常包括具有第一导电类型的半导体基板(例如,n型基板)(诸如碳化硅基板),在该基板上形成具有第一导电类型(例如,n型)的外延层结构。这个外延层结构的一部分(其可以包括一个或多个单独的层)用作功率半导体器件的漂移区域。该器件通常包括“有源区域”,其包括一个或多个具有诸如p-n结或肖特基结之类的结的功率半导体器件结构。有源区域可以形成在漂移区域上和/或漂移区域中。有源区域充当主结,用于在反向偏置方向上阻断电压并在正向偏置方向上提供电流。功率半导体器件还可以在与有源区域相邻的端接区域中具有边缘端接(termination)。一个或多个功率半导体器件可以形成在基板上,并且每个功率半导体器件通常将具有其自己的边缘端接。在基板被完全处理之后,所得结构可以被切割以分离单独的边缘端接的功率半导体器件。功率半导体器件可以具有单位单元结构,其中每个功率半导体器件的有源区域包括多个单独的“单位单元”结构,这些结构彼此平行部署并且可以一起用作单个功率半导体器件。

5、功率半导体器件被设计为阻断(在正向或反向阻断状态下)或传递(在正向操作状态下)大电压和/或大电流。例如,在阻断状态下,功率半导体器件可以被设计为承受数百或数千伏的电位。但是,当施加的电压接近或超过器件被设计为阻断的电压水平时,不小的电流水平可以开始流过功率半导体器件。这种通常被称为“漏电流”的电流可能是非常不期望的。如果电压增加到超过器件的设计电压阻断能力,漏电流可以开始流动,这可以取决于尤其是漂移区域的掺杂和厚度等因素。漏电流也可以由于其他原因而产生,诸如器件的边缘端接和/或主结发生故障。如果施加到器件的电压超过击穿电压并达到临界水平,那么增加的电场会导致半导体器件内生成不可控制的和不期望的电荷载流子失控,从而导致称为雪崩击穿的状况。

6、功率半导体器件还可以开始允许不小的漏电流在低于器件的设计的击穿电压的电压水平下流动。特别地,漏电流可以开始在有源区域的边缘处流动,由于电场拥挤效应,高电场可以出现在那里。为了减少这种电场拥挤(以及由此产生的增加的漏电流),可以提供上面提到的边缘端接,其包围功率半导体器件的部分或全部有源区域。这些边缘端接可以将电场分散到更大的区域,从而减少电场拥挤。

技术实现思路

1、根据本公开的一些实施例,功率半导体器件包括半导体层结构,该半导体层结构包括第一导电类型的半导体漂移区域以及包括第二导电类型的多个保护环的边缘端接区域。保护环中的一个或多个延伸到半导体漂移区域的表面中至大于大约1微米(μm)的相应深度,并且横向彼此分离小于大约3μm的间距。

2、在一些实施例中,保护环中的一个或多个分别包括与表面相邻的第一部分和与表面间隔开的第二部分,其中第一部分比第二部分宽。

3、在一些实施例中,第二部分包括比第一部分更高的第二导电类型的掺杂剂浓度。

4、在一些实施例中,第一部分延伸到表面中至第一深度,并且其中第二部分延伸通过第一部分至大于第一深度的第二深度。

5、在一些实施例中,保护环中的一个或多个分别包括第三部分,该第三部分包括比第二部分更高的第二导电类型的掺杂剂浓度。

6、在一些实施例中,第三部分比第一部分窄。

7、在一些实施例中,第三部分在两个或更多个维度上被限制在第一部分内。

8、在一些实施例中,保护环中的一个或多个分别包括侧壁,该侧壁包括第一部分与第二部分之间的阶梯差。

9、在一些实施例中,阶梯差被限定在包括不同掺杂剂浓度的保护环的部分之间的界面处。

10、在一些实施例中,半导体层结构还包括有源区域,该有源区域包括半导体漂移区域中的第二导电类型的多个阱区域,其中阱区域延伸到第一深度。

11、在一些实施例中,有源区域还包括多个屏蔽图案,该多个屏蔽图案包括比阱区域更高的第二导电类型的掺杂剂浓度,其中屏蔽图案延伸到第二深度。

12、在一些实施例中,第一部分之间的相应间距基本上均匀。

13、在一些实施例中,相应的深度是大约1μm至大约3μm,并且相应的间距是大约0.5μm至大约3μm。

14、在一些实施例中,保护环中的一个或多个分别包括与表面相邻的第一宽度和与表面间隔开的第二宽度,并且第一宽度与第二宽度的比率是大约0.95至大约2。

15、根据本公开的一些实施例,功率半导体器件包括半导体层结构,该半导体层结构包括第一导电类型的半导体漂移区域以及包括延伸到半导体漂移区域的表面中的第二导电类型的多个保护环的边缘端接区域。保护环中的一个或多个分别包括与表面相邻的第一部分和与表面间隔开的第二部分,其中第一部分比第二部分宽。

16、在一些实施例中,第二部分包括比第一部分更高的第二导电类型的掺杂剂浓度。

17、在一些实施例中,第一部分延伸到表面中至第一深度,并且第二部分延伸通过第一部分至大于第一深度的第二深度。

18、在一些实施例中,保护环中的一个或多个分别包括第三部分,该第三部分包括比第二部分更高的第二导电类型的掺杂剂浓度,并且第三部分比第一部分窄。

19、在一些实施例中,保护环中的一个或多个横向彼此分离相应的间距,其中第一部分之间的相应间距基本上均匀。

20、在一些实施例中,保护环中的一个或多个分别包括侧壁,该侧壁包括第一部分与第二部分之间的阶梯差。

21、根据本公开的一些实施例,功率半导体器件包括半导体层结构,该半导体层结构包括第一导电类型的半导体漂移区域以及包括延伸到半导体漂移区域的表面中的第二导电类型的多个保护环的边缘端接区域。保护环中的一个或多个分别包括与表面相邻的第一部分、与表面间隔开的第二部分以及侧壁,其中相应保护环的侧壁包括第一部分与第二部分之间的阶梯差。

22、在一些实施例中,第二部分包括比第一部分更高的第二导电类型的掺杂剂浓度,并且阶梯差被限定在第一部分与第二部分之间的界面处。

23、在一些实施例中,第一部分比第二部分宽。

24、在一些实施例中,第一部分延伸到表面中至第一深度,并且第二部分延伸通过第一部分至大于第一深度的第二深度。

25、在一些实施例中,半导体层结构还包括有源区域,该有源区域包括半导体漂移区域中的第二导电类型的多个阱区域,其中阱区域延伸到第一深度。

26、在一些实施例中,有源区域还包括多个屏蔽图案,该多个屏蔽图案包括比阱区域更高的第二导电类型的掺杂剂浓度,其中屏蔽图案延伸到第二深度。

27、在一些实施例中,保护环中的一个或多个分别包括第三部分,该第三部分包括比第二部分更高的第二导电类型的掺杂剂浓度,其中第三部分比第一部分窄。

28、在一些实施例中,保护环中的一个或多个延伸到半导体漂移区域的表面中至大约1μm至大约3μm的相应深度,并且彼此横向分离大约0.5μm至大约3μm的相应间距。

29、在一些实施例中,第一部分之间的相应间距基本上均匀。

30、在一些实施例中,第一部分具有第一宽度并且第二部分具有第二宽度,并且第一宽度与第二宽度的比率是大约0.95至大约2。

31、根据本公开的一些实施例,功率半导体器件包括半导体层结构,该半导体层结构包括第一导电类型的半导体漂移区域以及包括延伸到半导体漂移区域的表面中的第二导电类型的多个保护环的边缘端接区域。保护环中的一个或多个分别包括与表面相邻的第一宽度和与表面间隔开的第二宽度,并且第一宽度与第二宽度的比率是大约0.95至大约2。

32、在一些实施例中,保护环中的一个或多个分别包括具有第一宽度的第一部分和具有第二宽度的第二部分,其中第一部分比第二部分宽。

33、在一些实施例中,第二部分包括比第一部分更高的第二导电类型的掺杂剂浓度。

34、在一些实施例中,第一部分延伸到表面中至第一深度,并且第二部分延伸通过第一部分至大于第一深度的第二深度。

35、在一些实施例中,保护环中的一个或多个分别包括第三部分,该第三部分包括比第二部分更高的第二导电类型的掺杂剂浓度,其中第三部分比第一部分窄。

36、在一些实施例中,保护环中的一个或多个分别包括侧壁,该侧壁包括第一部分与第二部分之间的阶梯差。

37、在一些实施例中,保护环中的一个或多个延伸到半导体漂移区域的表面中至大约1μm至大约3μm的相应深度,并且彼此横向分离大约0.5μm至大约3μm的相应间距。

38、在一些实施例中,第一部分之间的相应间距基本上均匀。

39、在一些实施例中,比率是大约0.95至大约1.05。

40、在一些实施例中,比率是大约0.99至大约1.01。

41、根据本公开的一些实施例,一种制造功率半导体器件的方法包括提供包括第一导电类型的半导体漂移区域的半导体层结构;以及在半导体漂移区域中形成第二导电类型的多个保护环以形成边缘端接区域。形成保护环包括分别使用第一和第二掩模图案在半导体漂移区域上顺序执行第一和第二离子注入过程,其中第一掩模图案包括与第二掩模图案宽度不同的开口。

42、在一些实施例中,形成保护环包括使用第一掩模图案执行第一离子注入过程以形成与半导体漂移区域的表面相邻的保护环的第一部分;以及使用第二掩模图案执行第二离子注入过程以形成与表面间隔开的保护环的第二部分。第二掩模图案中的开口比第一掩模图案中的开口窄,并且第二部分包括比第一部分更高的第二导电类型的掺杂剂浓度。

43、在一些实施例中,第二离子注入过程包括比第一离子注入过程更大的注入能量。

44、在一些实施例中,第二掩模图案包括比第一掩模图案更大的厚度。

45、在一些实施例中,在执行第二离子注入过程之前,该方法包括在第二掩模图案的侧壁上形成间隔物以在其中限定开口。

46、在一些实施例中,第二离子注入过程在第一离子注入过程之后执行,并且间隔物在一个或多个横向维度上与保护环的第一部分的边界重叠。

47、在一些实施例中,在执行第二离子注入过程之前,该方法包括在第一掩模图案的侧壁上形成间隔物以在半导体漂移区域上形成第二掩模图案。

48、在一些实施例中,使用第二掩模图案执行第二离子注入过程包括形成保护环的第三部分,其中第三部分包括比第二部分更高的第二导电类型的掺杂剂浓度。

49、在一些实施例中,第三部分在两个或更多个维度上被限制在第一部分内。

50、在一些实施例中,第一部分延伸到表面内至第一深度,并且第二部分延伸通过第一部分至大于第一深度的第二深度。

51、在一些实施例中,半导体层结构还包括有源区域,并且使用第一掩模图案执行第一离子注入过程包括形成延伸到有源区域中的半导体漂移区域的表面中至第一深度的第二导电类型的多个阱区域。

52、在一些实施例中,使用第二掩模图案执行第二离子注入过程包括形成多个屏蔽图案,该多个屏蔽图案包括比阱区域更高的第二导电类型的掺杂剂浓度,并且延伸到有源区域中的半导体漂移区域的表面中至第二深度。

53、在一些实施例中,保护环横向彼此分离相应的间距,并且第一部分之间的相应间距基本上均匀。

54、在一些实施例中,第二部分之间的相应间距是不均匀的。

55、根据一些实施例的其他器件、装置和/或方法在查看以下附图和详细描述后对于本领域技术人员将变得显而易见。除了上述实施例的任何和所有组合之外,所有此类附加实施例都旨在包括在本描述中、在本发明的范围内,并由所附权利要求保护。

本文地址:https://www.jishuxx.com/zhuanli/20240731/180977.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。