存储电路及数据的写入方法与流程

- 国知局

- 2024-07-31 19:26:41

本发明主要涉及到数据存储的,确切的说,涉及到了在数据存储中可以避免数据无法写入或写入错误的存储电路及数据的写入方法。

背景技术:

1、静态随机存储器(sram)作为存储器中的一员,具有高速度、低功耗与标准工艺相兼容等优点,广泛应用于pc、个人通信、消费电子产品、智能卡、数码相机、多媒体播放器等领域。再如工业科学的很多子系统,汽车电子等都用到sram。现代设备中很多都嵌入了数千字节的sram。实际上几乎所有实现了电子用户界面的现代设备都可能用到了sram,如玩具、数码相机、手机、音响合成器等用到几兆字节sram。实时信号处理电路往往使用双口(dual-ported)的sram。

2、和动态随机存储器dram(dynamic random access memory)相比较,静态随机存储器sram不需要刷新电路即能保存它内部存储的数据。dram每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此sram具有较高的性能,但是sram也有它的缺点,即它的集成度较低,功耗较dram大,相同容量的dram内存可以设计为较小的体积,但静态随机存储器sram却需要很大的体积。dram在同样面积的硅片可以做出更大容量的存储器并导致sram显得更贵。在实现基本存储方面的基础上,静态随机存储器要尽量压缩不必要的电路但又必须保障不能有功能缺陷。

3、现有技术的sram数据写入稳定性较差,容易在数据写入操作中出现使存储的数据跳变或者无法写入数据等情况,因此,如何提高sram数据写入的稳定性,成为本领域技术人员亟待解决的问题。存储电路读写功能仍然有待改善。数据写入对存储器而言并非是瞬间完成的,当单个存储单元通过字线和位线被选中之时,字线和位线上的电位变化存在着跳变时间及字线和位线上的电位保持也存在着持久时间。在数据操作时倘若将前述时间设置得较长以求得数据能够顺利写入,随之而来的疑虑是,在高速存储环境下失配的单次写操作时间或单次读操作时间会与数据通信协议产生失衡,结果是发生数据操作失败譬如单个存储单元过久的数据读写时间会与数据协议规定的速度不匹配。

技术实现思路

1、本技术涉及一种数据的写入方法,其特征在于,包括:

2、在对静态随机存储单元写入数据的阶段,通过第一电平的字线信号和通过第一电平的的第一位线信号选择待写的静态随机存储单元:

3、由该第一电平的第一位线信号将控制位线电位的位线开关接通、将低侧电压通过位线而锁存进第一存储节点,以及由一第二电平的第二位线信号将控制位线非电位的位线非开关关断、将高侧电压通过位线非而锁存进与第一存储节点互补的第二存储节点,藉此将预写数值替代之前保存的当前数值而写入待写的静态随机存储单元;

4、第一位线信号从该第一电平跳变至该第二电平而关断位线开关的跳变时刻,瞬时的将低于高侧电压的预置电压耦合到位线一次,防止预写数值回弹至当前数值,其中所述预置电压为一个独立的参照电压或为所述低侧电压或为一个负电压。

5、上述的方法,第一位线信号分成两个支路,其中一者耦合到第一或非门的一个输入端以及另一者通过延时单元和反相器后再耦合到第一或非门的另一输入端,第一或非门的输出控制第一开关的关断或接通、并在所述跳变时刻例如通过将第一开关接通从而将预置电压耦合到位线一次;

6、在所述预置电压与位线之间设置第一开关和一个源漏短接的第一晶体管,第一晶体管的两端对应分别连接到位线和通过第一开关连接到预置电压(如第一晶体管两端之一连到位线而余下另一端通过第一开关连接到预置电压)。

7、上述的方法,所述低侧电压为参考地电压、高侧电压为静态随机存储单元工作的电源电压,所述预置电压为负电压时则限制其低于参考地电压。

8、上述的方法,该第一电平为高电平而该第二电平为低电平,或者该第一电平为低电平而该第二电平为高电平。

9、上述的方法,静态随机存储单元完成数据写入后,字线信号和第一位线信均从该第一电平跳变至该第二电平,以退出对待写的静态随机存储单元的数据写操作。

10、上述的方法,当前数值包括数据1、预写数值包括数据0。

11、上述的方法,所述低侧电压为参考地电压、高侧电压为静态随机存储单元的电源电压以及所述预置电压为一个独立的参照电压或为所述低侧电压或为一个负电压。

12、上述的方法,在所述跳变时刻由预置电压对位线的瞬时耦合,使第一存储节点趋于接近低侧电压但还未到低侧电压的振荡、第二存储节点趋于接近高侧电压但还未到高侧电压的振荡,向着在第一与第二存储节点之间建立正反馈的趋势发展。

13、本技术涉及一种数据的写入方法,其特征在于,包括:

14、在对静态随机存储单元写入数据的阶段,通过第一电平的字线信号和通过第一电平的第二位线信号选择待写的静态随机存储单元:

15、由该第一电平的第二位线信号将控制位线非电位的位线非开关接通、将低侧电压通过位线非而锁存进第二存储节点,以及由第二电平的第一位线信号将控制位线电位的位线开关关断、将高侧电压通过位线而锁存进与第二存储节点互补的第一存储节点,藉此将预写数值替代之前保存的当前数值而写入待写的静态随机存储单元;

16、第二位线信号从该第一电平跳变至该第二电平而关断位线非开关的跳变时刻,瞬时的将低于高侧电压的预置电压耦合到位线非一次,防止预写数值回弹至当前数值,其中所述预置电压为一个独立的参照电压或为所述低侧电压或为一个负电压。

17、上述的方法,第二位线信号分成两个支路,其中一者耦合到第二或非门的一个输入端以及另一者通过延时单元和反相器后再耦合到第二或非门的另一输入端,第二或非门的输出控制第二开关的关断或接通、并在所述跳变时刻例如通过将第二开关接通从而将预置电压耦合到位线非一次;

18、在所述预置电压与位线非之间设置第二开关和一个源漏短接的第二晶体管,第二晶体管的两端对应分别连接到位线非和通过第二开关连接到预置电压(例如第二晶体管两端之一连到位线非而余下另一端通过第二开关连接到预置电压)。

19、上述的方法,在所述跳变时刻由预置电压对位线非的瞬时耦合,使第二存储节点趋于接近低侧电压但还未到低侧电压的振荡、第一存储节点趋于接近高侧电压但还未到高侧电压的振荡,向着在第一与第二存储节点之间建立正反馈的趋势发展。

20、上述的方法,该第一电平为高电平而该第二电平为低电平,或者该第一电平为低电平而该第二电平为高电平。

21、上述的方法,静态随机存储单元完成数据写入后,字线信号和第二位线信均从第一电平跳变至第二电平,以退出对待写的静态随机存储单元的数据写操作。

22、上述的方法,所述低侧电压为参考地电压、高侧电压为静态随机存储单元的电源电压以及所述预置电压为一个独立的参照电压或为所述低侧电压或为一个负电压。

23、上述的方法,当前数值包括数据0、预写数值包括数据1。

24、本技术涉及一种存储电路,其特征在于,包括:

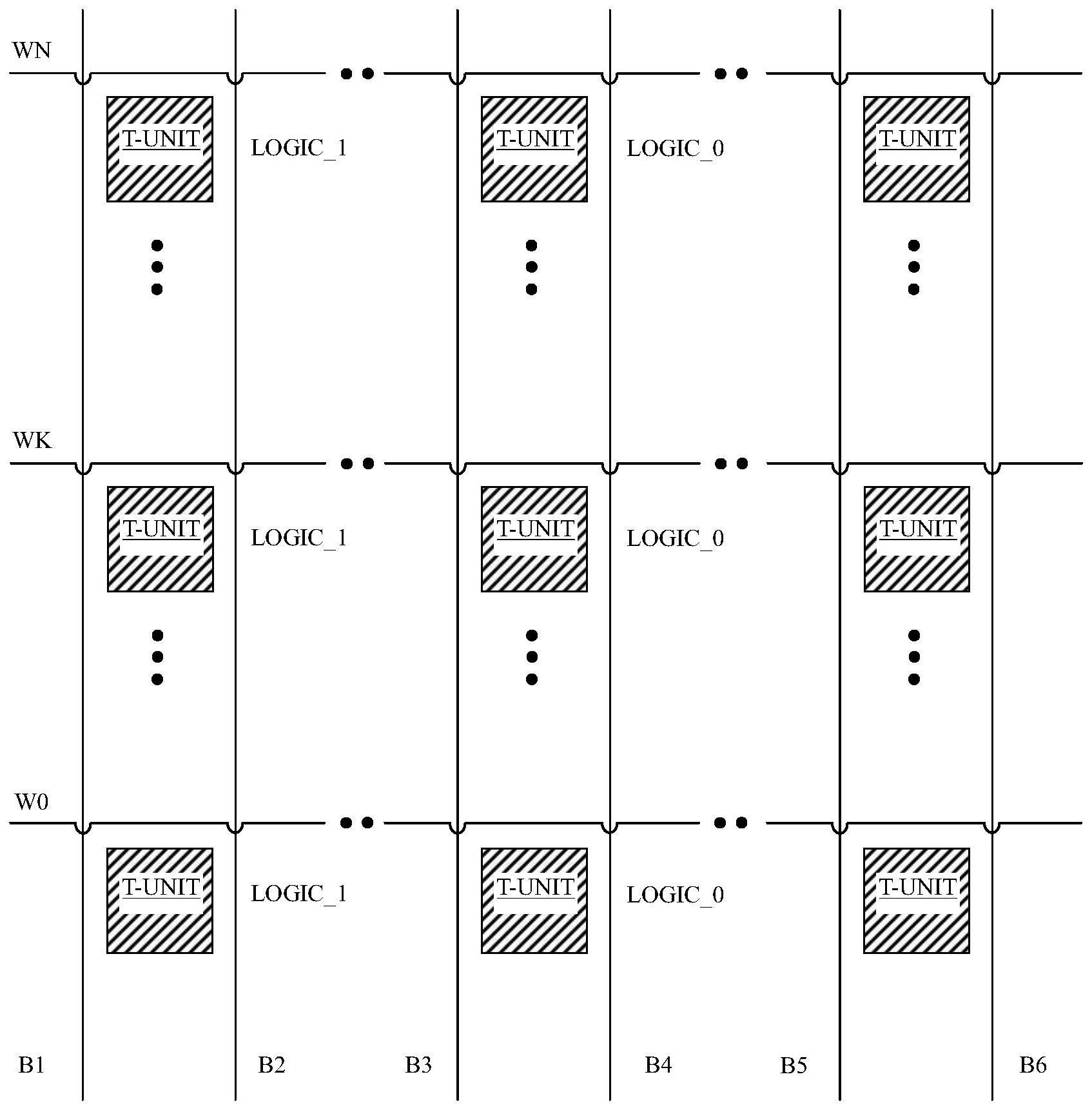

25、共用位线及位线非的多个静态随机存储单元,由第一位线信号控制位线开关的关断或接通以调节位线电位,由第二位线信号控制位线非开关的关断或接通以调节位线非的电位,由与任一静态随机存储单元匹配的字线信号来选中该任一静态随机存储单元;

26、第一位线信号分成两个支路,一者耦合到第一或非门的一个输入端,另一者通过延时单元和反相器后再耦合到第一或非门的另一输入端,第一或非门的输出控制第一开关的关断或接通,在第一位线信号从该第一电平跳变至该第二电平而关断位线开关的时刻将预置电压耦合到位线一次(将第一开关接通而将预置电压耦合到位线一次),防止写入静态随机存储单元的预写数值回弹至当前数值;

27、在预置电压与位线之间设置第一开关和一个源漏短接的第一晶体管,第一晶体管的两端对应分别连接到位线和通过第一开关连接到预置电压;和/或

28、第二位线信号分成两个支路,一者耦合到第二或非门的一个输入端,另一者通过延时单元和反相器后再耦合到第二或非门的另一输入端,第二或非门的输出控制第二开关的关断或接通、在第二位线信号从该第一电平跳变至该第二电平而关断位线非开关的时刻将预置电压耦合到位线非一次(将第二开关接通而将预置电压耦合到位线非一次),防止写入静态随机存储单元的预写数值回弹至当前数值;

29、在预置电压与位线非之间设置第二开关和一个源漏短接的第二晶体管,第二晶体管的两端对应分别连接到位线非和通过第二开关连接到预置电压。

30、本技术涉及一种数据的写入方法,其特征在于,包括:

31、在对静态随机存储单元写入数据的阶段,通过一第一电平的字线信号和第一位线信号选择待写的静态随机存储单元:

32、由该第一电平的第一位线信号将控制位线电位的位线开关接通、将低侧电压通过位线而锁存进第一存储节点,以及由一第二电平的第二位线信号将控制位线非电位的位线非开关关断、将高侧电压通过位线非而锁存进与第一存储节点互补的第二存储节点,藉此将预写数值替代之前保存的当前数值而写入待写的静态随机存储单元;

33、第一位线信号从该第一电平跳变至该第二电平而关断位线开关的跳变时刻,瞬时的将低于高侧电压的预置电压耦合到位线一次,防止预写数值回弹至当前数值;

34、在所述预置电压与位线之间设置一个开关和一个源漏短接的晶体管,晶体管的两端对应分别连接到位线和通过所述开关连接到预置电压;

35、第一位线信号分成两个支路,其中一者耦合到一个或非门的一个输入端,另一者通过延时单元和反相器后再耦合到或非门的另一输入端,或非门的输出控制所述开关的关断或接通、并在所述跳变时刻通过将所述开关接通而将预置电压耦合到位线一次。

36、本技术涉及一种数据的写入方法,其特征在于,包括:

37、在对静态随机存储单元写入数据的阶段,通过第一电平的字线信号和第二位线信号选择待写的静态随机存储单元:

38、由该第一电平的第二位线信号将控制位线非电位的位线非开关接通、将低侧电压通过位线非而锁存进第二存储节点,以及由第二电平的第一位线信号将控制位线电位的位线开关关断、将高侧电压通过位线而锁存进与第二存储节点互补的第一存储节点,藉此将预写数值替代之前保存的当前数值而写入待写的静态随机存储单元;

39、第二位线信号从该第一电平跳变至该第二电平而关断位线非开关的跳变时刻,瞬时的将低于高侧电压的预置电压耦合到位线非一次,防止预写数值回弹至当前数值;

40、在所述预置电压与位线非之间设置一个开关和一个源漏短接的晶体管,晶体管的两端对应分别连接到位线非和通过所述开关连接到预置电压;

41、第二位线信号分成两个支路,其中一者耦合到一个或非门的一个输入端,另一者通过延时单元和反相器后再耦合到或非门的另一输入端,或非门的输出控制所述开关的关断或接通、并在所述跳变时刻通过将所述开关接通而将预置电压耦合到位线非一次。

42、本技术技术方案解决了sram数据写入稳定性较差、容易在数据写入操作中出现存储数据跳变或无法写入数据等问题。考量每比特数据写入操作需要时间:单个存储单元通过字线和位线被选中之时,字线和位线上的电位变化存在着跳变时间及字线和位线上的电位保持也存在着延续时间。本技术在数据操作期间,无需过长的跳变时间和延续时间即可将数据顺利写入,字线和位线的电位变化满足高速通信的数据操作时限,数据操作的成功率得以保障并且数据写入操作可与通信协议规定的数据操作速度相匹配。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182527.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。