显示基板和显示装置的制作方法

- 国知局

- 2024-07-31 19:27:06

本发明涉及显示,尤其涉及一种显示基板和显示装置。

背景技术:

1、显示面板包括位于显示区域的阵列分布的多个像素电路和位于边缘区域的移位寄存器,所述移位寄存器包括多级驱动电路,所述驱动电路用于为对应的像素电路提供相应的扫描驱动信号。由于所述移位寄存器设置在显示面板的边缘区域,因此,所述驱动电路的排布方式决定了显示面板的边框宽度。

技术实现思路

1、本发明的主要目的在于提供一种显示基板和显示装置,解决现有技术中不能减短显示基板包括的驱动电路的沿第一方向的宽度,不利于实现窄边框的问题。

2、为了达到上述目的,本发明实施例提供了一种显示基板,包括设置于衬底基板上的移位寄存器,所述移位寄存器包括多级驱动电路,所述驱动电路包括第一输入电路、第二输入电路、第一输出电路和控制电路;所述第一输出电路配置为在第一节点的电位和第二节点的电位的控制下,向第一驱动信号输出端提供第一扫描驱动信号;所述第一输入电路配置为在时钟信号的控制下,向第三节点输入信号;所述第二输入电路配置为在所述第三节点的电位的控制下,将电源线提供的信号输入至第二节点;所述控制电路配置为控制第三节点的电位和所述第一节点的电位;

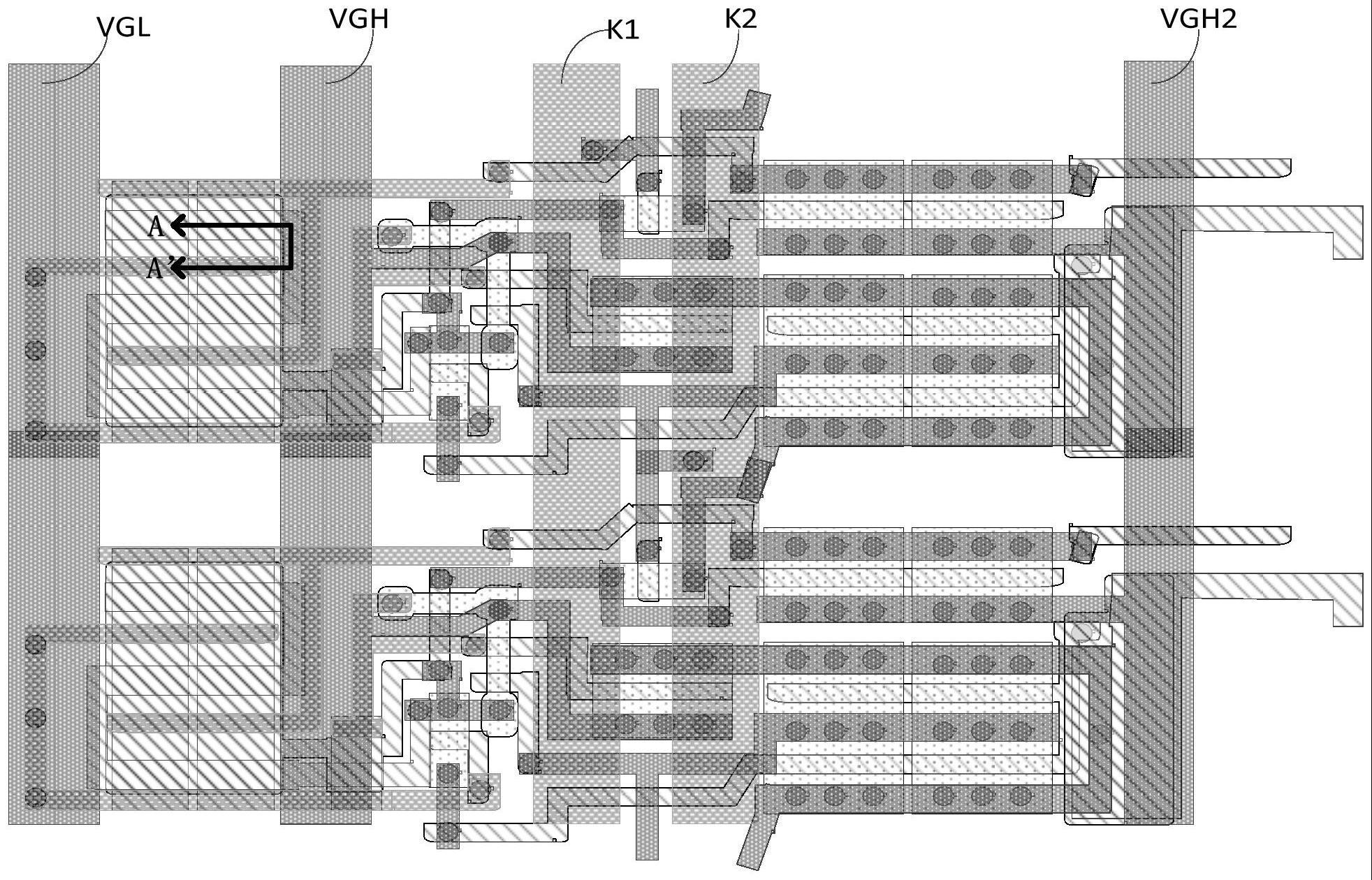

3、在所述衬底基板的驱动电路区域中设置有多级所述驱动电路;其中一级驱动电路区域包括第一区域和第二区域,在所述第一区域中设置有所述驱动电路包括的第一种类型晶体管,在所述第二区域中设置有所述驱动电路包括的第二种类型晶体管;

4、所述第一区域的一侧边为所述电源线远离所述第二区域的侧边,所述第一区域的另一侧边为靠近第二区域一侧的第一种类型晶体管的有源层靠近所述第二区域的侧边;

5、所述第二区域的一侧边是电源线远离第一区域的侧边,所述第二区域的另一侧边是靠近第二区域一侧的第一种类型晶体管的有源层靠近所述第二区域的侧边。

6、可选的,所述电源线包括第一电源线;所述第二输入电路用于在所述第三节点的电位的控制下,将所述第一电源线提供的第一电压信号输入至所述第二节点;

7、x1/x3≥0.21;

8、其中,x1为所述第一区域在第一方向上的宽度,x3为所述第二区域在所述第一方向上的宽度;

9、第一方向为与所述第一电源线的延伸方向相交的方向。

10、可选的,所述电源线包括第二电源线;所述第二输入电路用于在所述第三节点的电位的控制下,将所述第二电源线提供的第二电压信号输入至所述第二节点;

11、x1/x3≥0.52;

12、其中,x1为所述第一区域在第一方向上的宽度,x3为所述第二区域在所述第一方向上的宽度;

13、第一方向为与所述第二电源线的延伸方向相交的方向。

14、可选的,所述第一种类型晶体管为n型晶体管,所述第二种类型晶体管为p型晶体管;

15、至少一个所述n型晶体管与所述第二电源线的距离小于所述p型晶体管与所述第二电源线之间的距离。

16、可选的,所述第二输入电路包括第一晶体管;所述第一晶体管的栅极与所述第三节点电连接,所述第一晶体管的第一电极与第二电源线电连接,所述第一晶体管的第二电极与所述第二节点电连接;所述第一晶体管为第一种类型晶体管;

17、wt1/x1≥0.258;

18、其中,wt1为所述第一晶体管的有源层的沿第一方向的宽度。

19、可选的,所述驱动电路还包括第二输出电路,所述第二输出电路配置为在所述第三节点的电位的控制下,控制通过第二驱动信号输出端输出第二扫描驱动信号;所述第二输出电路包括第二晶体管;所述第二晶体管的栅极与所述第三节点电连接,所述第二晶体管的第一电极与所述第二电源线电连接,所述第二晶体管的第二电极与所述第二驱动信号输出端电连接;所述第二晶体管为第一种类型晶体管;

20、wt2/x1≥0.33;

21、wt2为所述第二晶体管的有源层的沿第一方向的宽度。

22、可选的,所述第二输入电路包括第一晶体管;所述第一晶体管的栅极与所述第三节点电连接,所述第一晶体管的第一电极与第二电源线电连接,所述第一晶体管的第二电极与所述第二节点电连接;所述驱动电路还包括第二输出电路,所述第二输出电路用于在所述第三节点的电位的控制下,控制通过第二驱动信号输出端输出第二扫描驱动信号;所述第二输出电路包括第二晶体管;所述第二晶体管的栅极与所述第三节点电连接,所述第二晶体管的第一电极与所述第二电源线电连接,所述第二晶体管的第二电极与所述第二驱动信号输出端电连接;所述第一晶体管和所述第二晶体管都为第一种类型晶体管;

23、wt2/wt1≥3.25;

24、所述第一晶体管的有源层的沿第一方向的宽度为wt1,wt2为所述第二晶体管的有源层的沿第一方向的宽度。

25、可选的,所述显示基板还包括设置于所述驱动电路区域的时钟信号线组,所述时钟信号线组被配置为提供所述时钟信号;

26、至少一个第一种类型晶体管的有源层在第一方向上位于时钟信号线组与电源线之间;

27、至少一个第一种类型晶体管的有源层在所述衬底基板上的正投影,与所述电源线在所述衬底基板上的正投影之间的交叠面积,小于等于该至少一个第一种类型晶体管的有源层的面积的六分之五。

28、可选的,至少一个第一种类型晶体管的有源层的沿第二方向的长度,与所述驱动电路的高度的比值小于等于0.75。

29、可选的,所述显示基板还包括设置于所述第二区域的第一有源层;所述第一有源层包括第一有源部、两个第二有源部和两个第三有源部;所述显示基板还包括第二输出电路;

30、所述第一有源部用作第三晶体管的有源层,所述两个第二有源部用作第四晶体管的有源层,所述两个第三有源部用作第五晶体管的有源层;

31、所述第三晶体管为所述第一输出电路包括的输出第一电压信号的晶体管,所述第五晶体管为所述第一输出电路包括的输出时钟信号的晶体管,所述第四晶体管为所述第二输出电路包括的输出第三电压信号的晶体管;

32、第n晶体管的沟道面积是arn,arn≥2(n-1)i,其中,n等于1、2或3,i为单位沟道面积。

33、可选的,第一有源部的面积p1为p,两个所述第二有源部的面积之和p2大于等于2p而小于等于3p;两个所述第三有源部的面积之和p3大于等于3p而小于等于4p。

34、可选的,所述显示基板还包括设置于所述驱动电路区域的时钟信号线;所述时钟信号线配置为提供时钟信号;所述第四晶体管的第一电极与第三电源线电连接;

35、第一距离与所述第三晶体管的有源层在第一方向上的长度之间的比值小于等于10.78;

36、所述第一距离为所述时钟信号线远离显示区域的一侧边,与第三电源线靠近显示区域的一侧边的距离。

37、可选的,所述显示基板还包括设置于所述驱动电路区域的时钟信号线;所述时钟信号线配置为提供时钟信号;所述第四晶体管的第一电极与第三电源线电连接;第一电源线的线宽与第一距离之间的比值大于等于0.060;所述第一电源线的线宽为所述第一电源线沿第一方向的长度,第一距离为所述时钟信号线远离显示区域的一侧边,与第三电源线靠近显示区域的一侧边的距离。

38、可选的,所述显示基板还包括设置于所述驱动电路区域的时钟信号线;所述时钟信号线配置为提供时钟信号;所述第四晶体管的第一电极与第三电源线电连接;

39、第三电源线的线宽与第一距离之间的比值小于等于0.045;所述第三电源线的线宽为所述第三电源线沿第一方向的长度,第一距离为所述时钟信号线远离显示区域的一侧边,与第三电源线靠近显示区域的一侧边的距离。

40、可选的,所述显示基板还包括设置于所述驱动电路区域的时钟信号线组;所述时钟信号线组包括至少一条时钟信号线,所述时钟信号线配置为提供时钟信号;所述显示基板包括至少两条电源线;

41、所述时钟信号线组位于所述至少两条电源线中的两条电源线之间;或者,所述时钟信号线组位于所述电源线远离显示区域的一侧。

42、可选的,所述显示基板包括第一电源线和第三电源线;所述显示基板还包括第二输出电路;所述第二输入电路配置为在所述第三节点的电位的控制下,将所述第一电源线提供的第一电压信号输入至所述第二节点;所述第二输出电路配置为在第三节点的电位的控制下,将第三电源线提供的第三电压信号输出至第二驱动信号输出端;

43、第二距离与第三晶体管的有源层在第一方向上的长度之比小于等于8.47;

44、所述第三晶体管为所述第一输出电路包括的输出第一电压信号的晶体管;所述第二距离为所述第一电源线远离显示区域的一侧边与所述第三电源线靠近所述显示区域的一侧边之间的距离。

45、可选的,所述显示基板包括第一电源线和第三电源线;所述显示基板还包括第二输出电路;所述第二输入电路配置为在所述第三节点的电位的控制下,将所述第一电源线提供的第一电压信号输入至所述第二节点;所述第二输出电路配置为在第三节点的电位的控制下,将第三电源线提供的第三电压信号输出至第二驱动信号输出端;

46、第一电源线的线宽与第二距离之间的比值大于等于0.077;

47、所述第一电源线的线宽为所述第一电源线在第一方向上的长度;所述第二距离为所述第一电源线远离显示区域的一侧边与所述第三电源线靠近所述显示区域的一侧边之间的距离。

48、可选的,所述显示基板包括第一电源线和第三电源线;所述显示基板还包括第二输出电路;所述第二输入电路配置为在所述第三节点的电位的控制下,将所述第一电源线提供的第一电压信号输入至所述第二节点;所述第二输出电路配置为在第三节点的电位的控制下,将第三电源线提供的第三电压信号输出至第二驱动信号输出端;

49、第三电源线的线宽与第二距离之间的比值大于等于0.058;

50、所述第三电源线的线宽为所述第三电源线在第一方向上的长度;所述第二距离为所述第一电源线远离显示区域的一侧边与所述第三电源线靠近所述显示区域的一侧边之间的距离。

51、可选的,所述显示基板包括沿着远离所述衬底基板的方向依次层叠设置的第一源漏金属层和第二源漏金属层;

52、所述时钟信号线包括设置于所述第一源漏金属层的第一时钟信号线部或者设置于所述第二源漏金属层的第二时钟信号线部。

53、可选的,所述显示基板还包括设置于所述第一源漏金属层和所述衬底基板之间的第三栅金属层;

54、所述时钟信号线还包括设置于所述第三栅金属层的第三时钟信号线部;

55、所述时钟信号线包括所述第一时钟信号线部,所述第三时钟信号线部与所述第一时钟信号线部之间直接接触或者通过过孔相互电连接;或者,所述时钟信号线包括所述第二时钟信号线部,所述第三时钟信号线部与所述第二时钟信号线部之间直接接触或者通过过孔相互电连接。

56、可选的,所述时钟信号线包括相互耦接的两个时钟信号线部,所述两个时钟信号线部分别设置于不同金属层;所述两个时钟信号线部中之一连续,所述两个时钟信号线部中另一时钟信号线部不连续。

57、可选的,所述显示基板包括第一转接电极;

58、本级驱动电路包括的第五晶体管的第一电极、本级驱动电路包括的第六晶体管的栅极和相邻级驱动电路包括的第七晶体管的栅极通过同一所述第一转接电极相互电连接;

59、所述第五晶体管为所述第一输出电路包括的输出时钟信号的晶体管,所述第六晶体管为所述控制电路包括的在时钟信号的控制下工作的晶体管,所述第七晶体管为所述第一输入电路包括的为第三节点提供输入电压的晶体管。

60、可选的,所述显示基板包括第一电源线和第二电源线;所述显示基板还包括第二输出电路;所述第一输入电路包括第七晶体管;所述第二输入电路包括第八晶体管;所述第七晶体管是为第三节点提供输入电压的晶体管,所述第八晶体管是在所述第三节点的电位的控制下,将所述第一电源线提供的第一电压信号输入至第二节点的晶体管;第四晶体管为所述第二输出电路包括的输出第三电压信号的晶体管;

61、所述第七晶体管的有源层的延伸方向与所述第八晶体管的有源层的延伸方向相同或垂直;

62、在同一级驱动电路中,所述第七晶体管的第一电极在第二方向上的位置,低于所述第四晶体管的第二电极在第二方向上的位置。

63、可选的,所述显示基板包括第一电源线,所述显示基板还包括第二转接电极,所述第二转接电极与所述第一电源线为一体结构;所述第二输入电路包括第八晶体管;所述第一输出电路包括第三晶体管;所述第八晶体管是在所述第三节点的电位的控制下,将所述第一电源线提供的第一电压信号输入至第二节点的晶体管;所述第三晶体管为所述第一输出电路包括的输出第一电压信号的晶体管;

64、所述第二转接电极包括第一电极部、第二电极部和第三电极部;

65、所述第一电极部用作所述第一电源线与所述第八晶体管的一电极之间的连接电极,所述第二电极部为所述第八晶体管的第一电极与所述第三晶体管的第一电极之间的连接电极,所述第三电极部用作所述第三晶体管的第一电极;

66、所述第一电极部与所述第二电极部之间的夹角大于等于90度而小于等于120度。

67、可选的,所述显示基板还包括第三转接电极;所述第三转接电极包括第四电极部、第五电极部和第六电极部;所述第二输入电路包括第一晶体管和第八晶体管;所述第一晶体管是在第三节点的电位的控制下,将第二电源线提供的第二电压信号输入至第二节点的晶体管;所述驱动电路还包括第二输出电路,所述第二输出电路包括第二晶体管;所述第二晶体管是在第三节点的电位的控制下,将第二电源线提供的第二电压信号输出至第二驱动信号输出端的晶体管;所述第八晶体管是在所述第三节点的电位的控制下,将第一电源线提供的第一电压信号输入至第二节点的晶体管;所述控制电路包括第六晶体管和第九晶体管,所述第六晶体管为在时钟信号的控制下工作的晶体管;

68、所述第九晶体管为在第二电源线提供的第二电压信号的控制下,控制第三节点与第一节点之间连通的晶体管;所述第一晶体管和所述第二晶体管为第一种类型晶体管,所述第八晶体管和所述第九晶体管为第二种类型晶体管;

69、所述第四电极部用于电连接第一晶体管的底栅与第八晶体管的栅极;和/或,所述第四电极部用于电连接第二晶体管的底栅与所述第八晶体管的栅极;

70、所述第五电极部用于电连接所述第四电极部、所述第九晶体管的第一电极和所述第一晶体管的顶栅;和/或,所述第五电极部用于电连接所述第四电极部、所述第九晶体管的第一电极和所述第二晶体管的顶栅;

71、所述第六电极部用于电连接所述第九晶体管的第一电极和所述第六晶体管的第二电极。

72、可选的,所述第四电极部与所述第五电极部之间的夹角大于等于90度而小于130度。

73、可选的,所述第五电极部与所述第六电极部垂直或平行。

74、可选的,所述第一输出电路还包括第一电容,所述第一电容的第一极板与第一节点电连接,所述第一电容的第二极板与第一驱动信号输出端电连接;所述显示基板还包括第一屏蔽部;

75、所述第一电容的第一极板设置于所述衬底基板与所述第一电容的第二极板之间;

76、所述第一屏蔽部设置于所述第一电容的第二极板远离所述衬底基板的一侧。

77、可选的,本发明至少一实施例所述的显示基板还包括第二屏蔽部;所述第二输入电路包括第一晶体管;

78、所述第二屏蔽部设置于所述第一晶体管的有源层远离所述衬底基板的一侧;

79、所述第二屏蔽部在所述电源线上的正投影的面积大于所述第一晶体管的有源层在电源线上的正投影的面积。

80、本发明实施例还提供一种显示基板,包括设置于衬底基板上的移位寄存器,所述移位寄存器包括多级驱动电路,所述驱动电路包括第一输入电路、第二输入电路、第一输出电路、控制电路和第二输出电路;所述第一输出电路配置为在第一节点的电位和第二节点的电位的控制下,向第一驱动信号输出端提供第一扫描驱动信号;所述第一输入电路配置为在时钟信号的控制下,向第三节点输入信号;所述第二输入电路配置为在所述第三节点的电位的控制下,将电源线提供的信号输入至第二节点;所述控制电路配置为控制第三节点的电位和所述第一节点的电位;所述第二输出电路配置为在所述第三节点的电位的控制下,控制通过第二驱动信号输出端输出第二扫描驱动信号;所述第二输入电路包括第一晶体管;所述第二输出电路包括第二晶体管;

81、所述驱动电路用于为显示区域提供扫描驱动信号;

82、第一晶体管的栅极与所述第三节点电连接,所述第一晶体管的第一电极与第二电源线电连接,所述第一晶体管的第二电极与所述第二节点电连接;第二晶体管的栅极与所述第三节点电连接,所述第二晶体管的第一电极与所述第二电源线电连接,所述第二晶体管的第二电极与所述第二驱动信号输出端电连接;所述第一晶体管和所述第二晶体管为n型晶体管;

83、所述第二晶体管的氧化物有源层的面积与所述第一晶体管的氧化物有源层的面积的比值大于等于8.74。

84、可选的,第四晶体管为所述第二输出电路包括的输出第三电压信号的晶体管;所述第四晶体管为p型晶体管;所述第四晶体管的有源层为低温多晶硅有源层;

85、所述第二晶体管的氧化物有源层的面积与所述第四晶体管的有源层的面积的比值大于等于1.4。

86、可选的,所述电源线包括第一电源线和第三电源线;所述第二输入电路用于在所述第三节点的电位的控制下,将所述第一电源线提供的第一电压信号输入至所述第二节点;所述第二输出电路与第三电源线电连接,用于在第三节点的电位的控制下,将所述第三电源线提供的第三电压信号提供至第二驱动信号输出端;

87、所述第三电压信号的电压值大于等于所述第一电压信号的电压值。

88、可选的,所述第三电压信号的电压值大于等于所述第一电压信号的电压值的1.4倍。

89、可选的,所述第一晶体管的栅极包括第一栅极和第二栅极,所述第二晶体管的栅极包括第一栅极和第二栅极,所述第一栅极为底栅,所述第二栅极为顶栅;所述显示基板包括沿着远离所述衬底基板的一侧层叠设置的第一栅金属层、第二栅金属层和第三栅金属层;

90、所述底栅包含于所述第一栅金属层,所述顶栅包含于所述第二栅金属层;或者,所述底栅包含于所述第二栅金属层,所述顶栅包含于所述第三栅金属层;或者,所述底栅包含于所述第一栅金属层,所述顶栅包含于所述第三栅金属层。

91、可选的,所述第一晶体管的第一栅极与所述第二晶体管的第一栅极为一体结构,所述第一晶体管的第二栅极与所述第二晶体管的第二栅极为一体结构;所述显示基板还包括设置于所述第三栅金属层远离所述衬底基板的一侧的第一源漏金属层和第二源漏金属层;所述第一源漏金属层设置于所述第三栅金属层与所述第二源漏金属层之间;

92、所述第一晶体管的第一栅极与所述第一晶体管的第二栅极之间通过连接电极相互电连接,所述连接电极包含于所述第一源漏金属层或所述第二源漏金属层。

93、本发明实施例还提供一种显示基板,包括设置于衬底基板上的移位寄存器,所述移位寄存器包括多级驱动电路;

94、所述驱动电路包括第一输入电路、第二输入电路、第一输出电路和控制电路;

95、所述第一输出电路配置为在第一节点的电位和第二节点的电位的控制下,向第一驱动信号输出端提供第一扫描驱动信号;

96、所述第一输入电路配置为在时钟信号的控制下,向第三节点输入信号;

97、所述第二输入电路配置为在所述第三节点的电位的控制下,将电源线提供的信号输入至第二节点;

98、所述控制电路配置为控制第三节点的电位和所述第一节点的电位。

99、可选的,所述电源线包括第一电源线和第二电源线;

100、所述第一输入电路分别与输入电压端、第一时钟信号线和第三节点电连接,配置为在所述第一时钟信号线提供的第一时钟信号的控制下,将所述输入电压端提供的输入电压写入所述第三节点;

101、所述第二输入电路分别与所述第三节点、所述第二电源线、第二节点和所述第一电源线电连接,配置为在所述第三节点的电位的控制下,将所述第一电源线提供的第一电压信号写入所述第二节点,并将所述第二电源线提供的第二电压信号写入所述第二节点;

102、所述第一输出电路分别与所述第二节点、第一节点、所述第一电源线、第二时钟信号线和第一驱动信号输出端电连接,配置为在所述第二节点的电位的控制下,将所述第一电源线提供的第一电压信号输出至所述第一驱动信号输出端,并在所述第一节点的电位的控制下,将所述第二时钟信号线提供的第二时钟信号输出至所述第一驱动信号输出端;

103、所述控制电路分别与所述第二节点、所述第一电源线、所述第二时钟信号线、所述第三节点、所述第一节点和第二电源线电连接,配置为在所述第二节点的电位和所述第二时钟信号线提供的第二时钟信号的控制下,控制将所述第一电源线提供的第一电压信号写入所述第三节点,并在所述第二电源线提供的第二电压信号的控制下,控制所述第三节点与所述第一节点之间连通。

104、可选的,本发明至少一实施例所述的显示基板还包括第二输出电路;

105、所述第二输出电路分别与所述第三节点、第二驱动信号输出端、第三电源线和第二电源线电连接,配置为在所述第三节点的电位的控制下,将所述第三电源线提供的第三电压信号输出至所述第二驱动信号输出端,并将所述第二电源线提供的第二电压信号输出至所述第二驱动信号输出端。

106、可选的,所述第二输出电路还与第一控制端电连接,所述第二输出电路的输出端与第二驱动信号输出端电连接;

107、所述第二输出电路还配置为在所述第一控制端提供的第一控制信号的控制下,控制将所述第三电压信号输出至所述第二驱动信号输出端,并用于在所述第三节点的电位和所述第一控制信号的控制下,将所述第二电压信号输出至所述第二驱动信号输出端。

108、可选的,本发明至少一实施例所述的显示基板还包括稳压电路;所述第二输出电路的输出端通过所述稳压电路与所述第二驱动信号输出端电连接;

109、所述稳压电路的输入端与所述第二输出电路的输出端电连接,所述稳压电路的输出端与所述第二驱动信号输出端电连接,所述稳压电路用于对所述第二输出电路输出的信号进行稳压,得到并通过所述第二驱动信号输出端输出第二扫描驱动信号。

110、可选的,本发明至少一实施例所述的显示基板还包括第一储能电路和第二储能电路;

111、所述第一储能电路的第一端与所述第二输出电路的输出端电连接,所述第一储能电路的第二端与所述第二驱动信号输出端电连接;

112、所述第二储能电路的第一端与所述第二输出电路的输出端电连接,所述第二储能电路的第二端与所述第二驱动信号输出端电连接;

113、所述第一储能电路和所述第二储能电路用于储存电能。

114、可选的,所述第一输入电路包括第七晶体管;所述第二输入电路包括第一晶体管和第八晶体管;所述第一输出电路包括第三晶体管、第五晶体管和第一电容;所述控制电路包括第六晶体管、第九晶体管和第十晶体管;

115、所述第一晶体管的栅极与所述第三节点电连接,所述第一晶体管的第一电极与第二电源线电连接,所述第一晶体管的第二电极与所述第二节点电连接;

116、所述第八晶体管的栅极与所述第三节点电连接,所述第八晶体管的第一电极与所述第一电源线电连接,所述第八晶体管的第二电极与所述第二节点电连接;

117、所述第七晶体管的栅极与所述第一时钟信号线电连接,所述第七晶体管的第一电极与所述输入电压端电连接,所述第七晶体管的第二电极与所述第三节点电连接;

118、所述第三晶体管的栅极与所述第二节点电连接,所述第三晶体管的第一电极与所述第一电源线电连接,所述第三晶体管的第二电极与所述第一驱动信号输出端电连接;

119、所述第五晶体管的栅极与所述第一节点电连接,所述第五晶体管的第一电极与所述第一驱动信号输出端电连接,所述第五晶体管的第二电极与所述第二时钟信号线电连接;

120、所述第一电容的第一极板与所述第一节点电连接,所述第一电容的第二极板与所述第一驱动信号输出端电连接;

121、所述第六晶体管的栅极与所述第二时钟信号线电连接,所述第六晶体管的第一电极与所述第十晶体管的第二电极电连接,所述第六晶体管的第二电极与所述第三节点电连接;

122、所述第十晶体管的栅极与所述第二节点电连接,所述第十晶体管的第一电极与所述第一电源线电连接;

123、所述第九晶体管的栅极与所述第二电源线电连接,所述第九晶体管的第一电极与所述第三节点电连接,所述第九晶体管的第二电极与所述第一节点电连接。

124、可选的,所述第二输出电路包括第二晶体管和第四晶体管;

125、所述第二晶体管的栅极与所述第三节点电连接,所述第二晶体管的第一电极与所述第二电源线电连接,所述第二晶体管的第二电极与所述第二驱动信号输出端电连接;

126、所述第四晶体管的栅极与所述第三节点电连接,所述第四晶体管的第一电极与所述第三电源线电连接,所述第四晶体管的第二电极与所述第二驱动信号输出端电连接。

127、可选的,所述第二输出电路包括第二晶体管、第四晶体管、第十一晶体管和第十二晶体管;

128、所述第二晶体管的栅极与所述第三节点电连接,所述第二晶体管的第一电极与所述第十二晶体管的第二电极电连接,所述第二晶体管的第二电极与所述第二驱动信号输出端电连接;

129、所述第四晶体管的栅极与所述第三节点电连接,所述第四晶体管的第一电极与所述第三电源线电连接,所述第四晶体管的第二电极与所述第二驱动信号输出端电连接;

130、所述第十一晶体管的栅极与所述第一控制端电连接,所述第十一晶体管的第一电极与所述第三电源线电连接,所述第十一晶体管的第二电极与所述第二驱动信号输出端电连接;

131、所述第十二晶体管的栅极与所述第一控制端电连接,所述第十二晶体管的第一电极与所述第二电源线电连接。

132、可选的,所述稳压电路包括第十三晶体管和第十四晶体管;

133、所述第十三晶体管的栅极与所述第二输出电路的输出端电连接,所述第十三晶体管的第一电极与第二电源线电连接,所述第十三晶体管的第二电极与第二驱动信号输出端电连接;

134、所述第十四晶体管的栅极与所述第二输出电路的输出端电连接,所述第十四晶体管的第一电极与所述第三电源线电连接,所述第十四晶体管的第二电极与所述第二驱动信号输出端电连接。

135、可选的,所述第一储能电路包括第二电容,所述第二储能电路包括第三电容;所述第二电容的第一端与所述第二输出电路的输出端电连接,所述第二电容的第二端与所述第二驱动信号输出端电连接;

136、所述第三电容的第一端与所述第二输出电路的输出端电连接,所述第三电容的第二端与所述第二驱动信号输出端电连接。

137、本发明实施例还提供一种显示装置,包括上述的显示基板。

138、可选的,本发明至少一实施例所述的显示装置还包括时序控制器、扫描驱动器和数据驱动器;

139、所述时序控制器分别与所述扫描驱动器和所述数据驱动器电连接,用于分别为所述扫描驱动器和所述数据驱动器提供相应的控制信号;

140、所述扫描驱动器分别与多行扫描线电连接,用于将相应的扫描信号分别提供至所述多行扫描线;

141、所述数据驱动器分别与多列数据线电连接,用于分别为所述多列数据线提供相应的数据信号。

142、本发明所述的显示基板和显示装置能减短显示基板包括的驱动电路的沿第一方向的宽度,利于实现窄边框。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182554.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表