具有隔离壁的位单元的制作方法

- 国知局

- 2024-07-31 19:28:29

本发明涉及用于布置在半导体基板上的静态随机存取存储器(sram)的位单元,以及用于形成此类位单元的方法。

背景技术:

1、集成电路的设计通常涉及组合大量的功能单元,每个单元包括互连的多个晶体管以提供所需功能。存储器电路包括被配置成存储一个或多个位的多个存储器位单元。存储器电路的一个显著示例是静态随机存取存储器(sram)。在常规sram技术中,位单元占据总管芯表面积的相对较大部分。

2、尽管晶体管小型化的持续进步似乎允许更小的单元设计并从而允许更密集的电路,但尺寸减小的晶体管的开发本身可能不足以实现面积高效的电路系统。的确,晶体管的层和互连也需要考虑。

技术实现思路

1、本发明的目的是提供一种用于sram的位单元,该位单元使得能够进行面积高效的电路设计。可从下文中理解其他目的或另外一些目的。

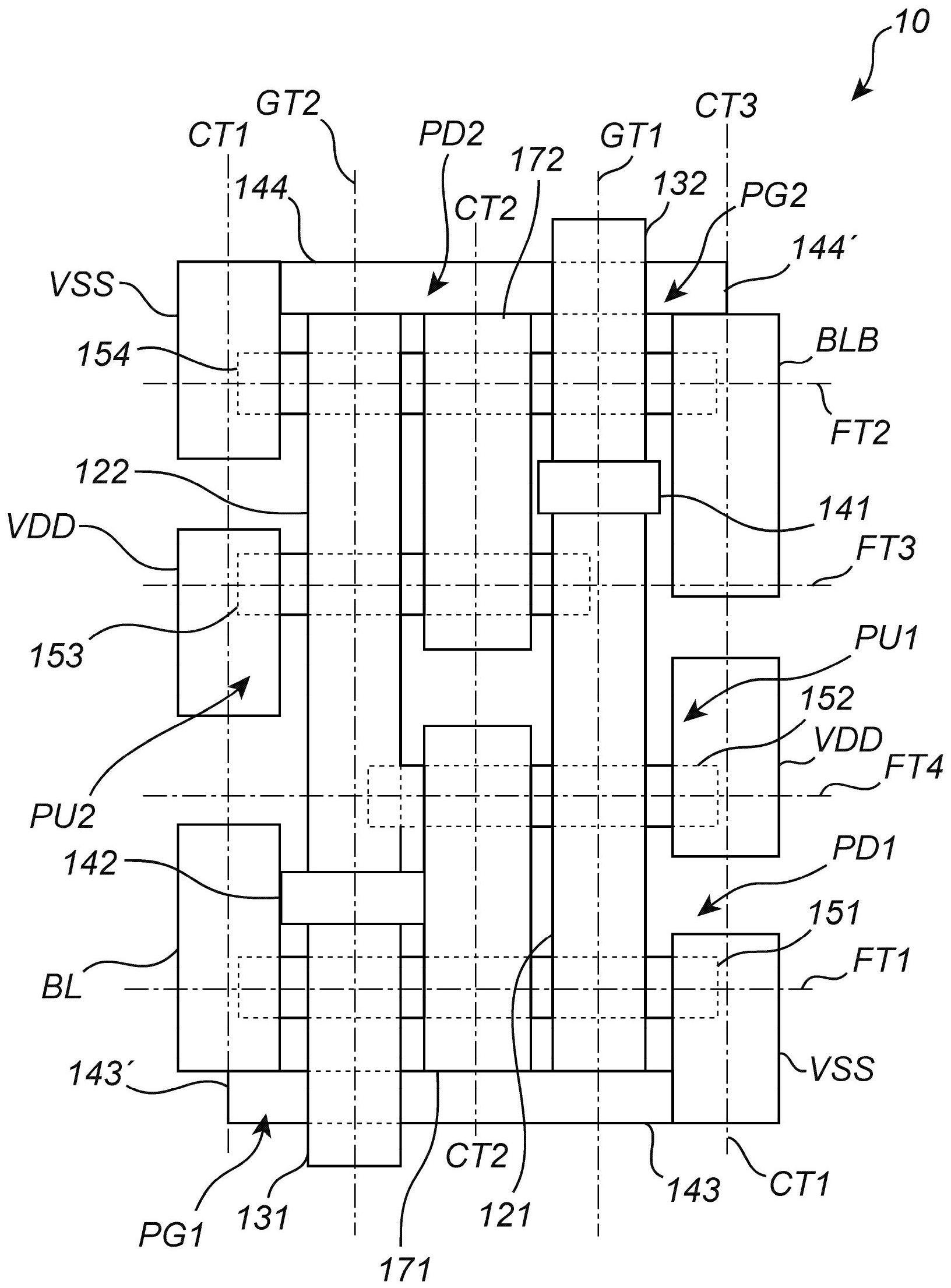

2、根据第一方面,提供了一种用于布置在半导体基板上的sram的位单元,该位单元包括:

3、第一对互补晶体管,包括第一上拉晶体管和第一下拉晶体管;

4、第二对互补晶体管,包括第二上拉晶体管和第二下拉晶体管;

5、第一传输门晶体管(pass-gate transistor);以及

6、第二传输门晶体管;

7、其中每一晶体管包括半导体沟道,所述半导体沟道沿着相应的水平沟道轨迹在相应的源极区和漏极区之间延伸;

8、其中所述位单元还包括:

9、形成用于所述第一对互补晶体管的半导体沟道的公共栅极电极的第一反相器栅极电极和形成用于所述第二对互补晶体管的半导体沟道的公共栅极电极的第二反相器栅极电极,其中所述第一反相器栅极电极和所述第二反相器栅极电极在横向于所述沟道轨迹的相应水平栅极轨迹中延伸:

10、形成所述第一传输门晶体管的栅极并与所述第一反相器栅极电极对准的第一传输栅极电极;

11、形成所述第二传输门晶体管的栅极并与所述第二反相器栅极电极对准的第二传输栅极电极;

12、形成在将所述第一传输栅极电极与所述第一反相器栅极电极分隔开的沟槽中的第一介电壁;以及

13、形成在将所述第二传输栅极电极与所述第二反相器栅极电极分隔开的沟槽中的第二介电壁。

14、一种用于形成静态随机存取存储器sram的位单元的方法,包括在半导体基板上形成:

15、第一对互补晶体管,包括第一上拉晶体管和第一下拉晶体管;

16、第二对互补晶体管,包括第二上拉晶体管和第二下拉晶体管;

17、第一传输门晶体管;以及

18、第二传输门晶体管;

19、其中每一晶体管包括半导体沟道,所述半导体沟道沿着相应的水平沟道轨迹在相应的源极区和漏极区之间延伸;

20、其中形成所述第一对互补晶体管包括在所述第一对互补晶体管的相应半导体沟道处形成第一反相器栅极电极,从而向所述第一对互补晶体管提供公共栅极电极;

21、其中形成所述第二对互补晶体管包括在所述第二对互补晶体管的相应半导体沟道处形成第二反相器栅极电极,从而向所述第二对互补晶体管提供公共栅极电极;

22、其中形成所述第一传输门晶体管和所述第二传输门晶体管包括形成第一传输栅极电极和形成第二传输栅极电极,所述第一传输栅极电极形成所述第一传输门晶体管的与所述第一反相器栅极电极对准的栅极,所述第二传输栅极电极形成第二传输门晶体管的与所述第二反相器栅极电极对准的栅极;

23、其中,所述方法还包括:

24、形成将所述第一传输栅极电极与所述第一反相器栅极电极分隔开的沟槽,并用介电材料填充所述沟槽,从而形成将所述第一传输栅极与所述第一反相器栅极电极分隔开的第一介电壁;

25、形成将所述第二传输栅极电极与所述第二反相器栅极电极分隔开的沟槽,并用介电材料填充所述沟槽,从而形成将所述第二传输栅极与所述第二反相器栅极电极分隔开的第二介电壁。

26、本发明的位单元设计通过采用第一和第二介电壁来将第一传输栅极电极与第一反相器栅极电极分隔开并将第二传输栅极电极与第二反相器栅极电极分隔开,来启用器件面积和电路密度的缩放。与通过栅极切割形成栅极电极的常规技术相比,这是特别有益的,在常规技术中,连续的栅极电极被蚀刻并拆分成彼此分隔开的两个分开的电极。当减小沟道轨迹之间的间距时,可以执行栅极切割的精度有可能成为决定沟道轨迹之间的最小可能间距的限制因素。栅极切割的精度尤其取决于可用图案化技术的精度和所使用的蚀刻工艺的选择性。光刻图案化工艺中的重叠和对准误差需要如下尺寸裕度:该尺寸裕度有阻碍沟道轨迹之间的间距减小到更小的尺寸的风险。发明人已经认识到,通过用可在栅极电极之前形成的介电壁代替栅极切割,两个对准的栅极电极的端部可以以更紧密的间距分隔开,这本来是可能的。

27、互补晶体管对可以包括具有相反沟道类型的一对晶体管,即n型晶体管和p型晶体管。第一和第二互补晶体管对可以被配置成相应的反相器对。双反相器对通过交叉耦合触点一起形成一对交叉耦合的反相器。

28、如已提及的,每个互补晶体管对的晶体管中的一者可以被配置成上拉晶体管,并且该对中的另一晶体管可以被配置成下拉晶体管。晶体管的名称“上拉”、“下拉”或“传输”在本文中应解释为所述晶体管被适配成在(cmos)反相器或sram位单元的传统理解的上下文中作为上拉、下拉或传输晶体管来起作用或工作。

29、晶体管可以是场效应晶体管(fet)。第一互补晶体管对可以相应地包括第一cmos对,即第一nfet(即,n型fet)和第一pfet(即,p型fet)。相应地,第二互补晶体管对可以包括第二cmos对。第一和第二传输晶体管可以各自是nfet或pfet。

30、每个晶体管包括沿着沟道轨迹(或者在晶体管是诸如鳍式fet之类的基于鳍的晶体管的情况下是鳍轨迹)延伸的半导体沟道。取决于位单元的特定布局,晶体管中的两者或更多者可以具有沿着同一轨迹延伸的沟道。因此,轨迹或沟道轨迹可以被定义成水平几何线,晶体管的沟道沿着该水平几何线形成并与其平行。

31、类似地,栅极电极中的两者或更多者(例如,反相器栅极电极和传输门电极)可以沿着同一栅极轨迹延伸。因此,栅极轨迹可被定义成水平几何线,栅极电极沿着该水平几何线延伸并平行于该水平几何线。优选地,栅极轨迹与沟道轨迹正交。

32、由于第一反相器栅极电极形成用于第一对互补晶体管的半导体沟道的公共栅极电极,所以第一反相器栅极电极可以被配置成控制第一对互补晶体管的两个半导体沟道的导电性。第一反相器栅极电极可以部分地或完全地包围第一对互补晶体管的半导体沟道。

33、由于第二反相器栅极电极形成用于第二对互补晶体管的半导体沟道的公共栅极电极,所以第二反相器栅极电极可以被配置成控制第二对互补晶体管的两个半导体沟道的导电性。第二反相器栅极电极可以部分地或完全地包围第二对互补晶体管的半导体沟道。

34、由于第一传输栅极电极形成用于第一传输门晶体管的半导体沟道的栅极,所以第一传输栅极电极可以被配置成控制第一传输门晶体管的半导体沟道的导电性。第一传输栅极电极可以部分地或完全地包围第一传输门晶体管沟道。

35、由于第二传输栅极电极形成用于第二传输门晶体管的半导体沟道的栅极,所以第二传输栅极电极可以被配置成控制第二传输门晶体管的半导体沟道的导电性。第二传输栅极电极可以部分地或完全地包围第二传输门晶体管沟道。

36、相对空间术语,诸如“垂直”、“上部”、“下部”、“堆叠在……顶部”,在本文中被理解为表示相对于基板的法线方向的位置或方向,或者等效地相对于器件层堆叠的自下而上的方向。相应地,诸如“横向”和“水平”等术语应理解成平行于基板的位置或方向,即平行于基板的上表面或主延伸平面。

37、在一些实施例中,每一晶体管的半导体沟道可以被布置在公共水平平面中。所得的位单元因此可以被称为平面位单元。可以意识到,取决于由第一和第二对互补晶体管形成的反相器的所选布局,在本公开的范围内可以设想到各种单元拓扑结构。例如,第一下拉晶体管和第一传输门晶体管的半导体沟道可以在公共沟道轨迹中对准,而第二下拉晶体管和第二传输门晶体管的半导体沟沟道可以在公共第二沟道轨迹中对准。将结合附图的详细描述来讨论进一步的示例。

38、在一些实施例中,第一和第二对互补晶体管可以布置在相应的垂直堆叠中,其中第一和第二反相器栅极电极中的每一者在相应晶体管对的上拉晶体管和下拉晶体管之间垂直延伸。换言之,当沿着垂直方向观察时,相应晶体管对被布置成垂直布置,其中该对的晶体管中的第一晶体管处于下部第一层级处,而晶体管中的另一晶体管处于上部第二层级处,或者处于与基板相距不同的距离处。在这一布局中,第一上拉晶体管和第一传输门晶体管的半导体沟道可以在公共沟道轨迹中对准,而第二上拉晶体管和第二传输门晶体管的半导体沟沟道可以在公共第二沟道轨迹中对准。第一沟道轨迹和第二沟道轨迹可以被布置在基板上方的第一垂直层级处,从而允许第一和第二下拉晶体管被布置在高于或低于第一层级的第二垂直层级处。

39、上述布局,其中每个晶体管对被布置在垂直堆叠中,即从基板看在彼此之上,可以被称为垂直布局,并且晶体管对被称为垂直堆叠的互补fet或cfet。这是降低位单元面积的高效方式,并且特别是降低相邻沟道轨迹之间的横向间距。

40、在一些实施例中,第一介电壁和第二介电壁可以在第一层级和第二层级之间垂直延伸,并且在互补晶体管的垂直堆叠之间水平延伸。绝缘壁的存在也在垂直布局中提供了传输栅极电极和反相器栅极电极之间的电分离,从而允许相邻沟道轨迹之间的间距进一步减小。归因于位单元的垂直布局,第一和第二介电壁可以形成公共壁,即形成同一壁结构的一部分。

41、位单元的本发明配置允许具有10纳米(nm)或更小,诸如8nm或更小的厚度的介电壁。

42、在一些示例中,每个晶体管的半导体沟道可以由相应的鳍部分形成。此类结构也可以被称为细长层堆叠,其纵向尺寸在沟道轨迹中沿着基板定向并从基板垂直突出。此外,一个或多个晶体管的半导体沟道可以有利地形成在一个或多个水平半导体纳米线中。栅极电极可以相应地被配置成完全包围/包裹相应的一个或多个纳米线的沟道区的全环绕栅极电极。水平半导体纳米线在此可以指沿着基板水平延伸并悬置在基板上方的半导体结构。纳米线可以形成具有闭合的周向延伸的边界表面的半导体主体。各种稍后的纵横比是可能的,诸如接近一的宽高比,或者大于一(诸如水平取向的纳米片半导体结构)或小于一(诸如垂直取向的纳米片)的宽高比。晶体管的源极区和漏极区也可以形成在纳米线的相对端。晶体管的源极和漏极触点可以完全包围/包裹相应的一个或多个纳米线的源极区和漏极区。

43、介电壁可以通过在由布置在相邻鳍部或细长层堆叠上的侧壁间隔物限定的间隙中沉积介电材料来形成,如将参考附图进一步详细讨论的。这允许介电壁的厚度由侧壁间隔物的厚度限定,并且侧壁在鳍之间自对准。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182648.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。