一次性可编程存储器控制器、相关处理系统、集成电路和方法与流程

- 国知局

- 2024-07-31 19:28:34

本公开涉及用于管理otp存储器的解决方案。

背景技术:

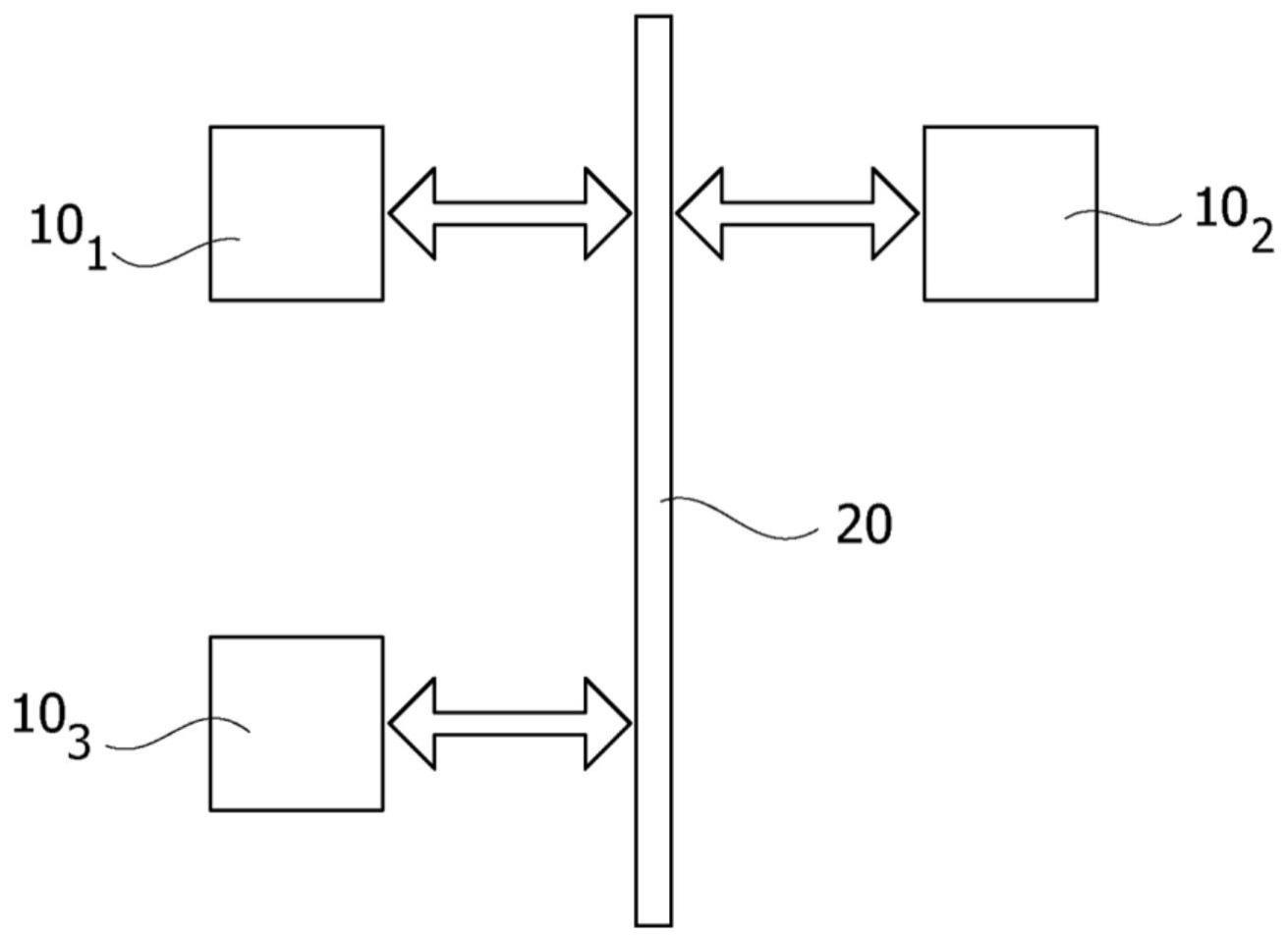

1、图1示出了典型的电子系统,诸如车辆的电子系统。该电子系统包括多个处理系统10,诸如嵌入式系统或集成电路,例如现场可编程门阵列(fpga)、数字信号处理器(dsp)或微控制器(例如,专用于汽车市场)。

2、例如,在图1中,示出了通过合适的通信系统20连接的三个处理系统101、102和103。例如,通信系统可以包括车辆控制总线(诸如控制器局域网(can)总线)和经由网关连接到车辆控制总线的可能的多媒体总线(诸如媒体导向系统传输(most)总线)。通常,处理系统10位于车辆的不同位置,并且可以包括例如引擎控制单元、变速器控制单元(tcu)、防抱死制动系统(abs)、车身控制模块(bcm)和/或导航和/或多媒体音频系统。因此,处理系统10中的一个或多个也可以实现实时控制和调节功能。这些处理系统通常被标识为电子控制单元。

3、在这方面,预计未来几代的该种处理系统10(例如,适用于汽车应用的微控制器)将表现出复杂性的增加,这主要是由于所请求的功能(新协议、新特征等)的数目不断增加、以及执行条件的严格限制(例如,更低的功耗、增加的计算能力和速度等)。例如,最近提出了更复杂的多核处理系统10。例如,这样的多核处理系统可以用于执行(并行)图1所示的处理系统10中的若干处理系统10,诸如车辆的若干ecu。

4、图2示出了处理系统10的示例,诸如多核处理系统。具体地,在所考虑的示例中,处理系统10包括连接到(片上)通信系统114的一个或多个处理核心102,诸如n个处理核心1021……102n。例如,在实时控制系统的上下文中,处理核心1021……102n可以是arm-r52核心。通常,通信系统114可以包括一个或多个总线系统,例如,基于高级可扩展接口(axi)总线架构和/或片上网络(noc)。

5、例如,如处理核心1021的示例所示,每个处理核心102可以包括微处理器1020和通信接口1022,该通信接口1022被配置为管理微处理器1020与通信系统114之间的通信。通常,接口1022是主接口,该主接口被配置为将给定(读取或写入)请求从微处理器1020转发到通信系统114,并且将可选的响应从通信系统114转发到微处理器1020。然而,通信接口1022还可以包括从接口。例如,以这种方式,第一微处理器1020可以(经由第一微处理器的通信接口1022、通信系统114和第二微处理器的通信接口1022)向第二微处理器1020发送请求。通常,每个处理核心1021……102n还可以包括另外的本地资源,诸如一个或多个本地存储器1026,通常被标识为紧密耦合存储器(tcm)。

6、通常,处理核心102被布置为与一个或多个非易失性存储器104和/或一个或多个易失性存储器104b交换数据。通常,存储器104和/或104b可以与处理核心102集成在单个集成电路中,或者存储器104和/或104b可以是单独的集成电路的形式,并且例如经由印刷电路板的迹线连接到处理核心102。

7、具体地,在多核处理系统10中,这些存储器通常是系统存储器,即对处理核心1021……102n共享。例如,为此,与存储器104和/或104b的通信可以经由连接到通信系统114的一个或多个存储器控制器100来执行。然而,如前所述,每个处理核心102可以包括一个或多个附加本地存储器1026。

8、例如,由(多个)微处理器1020执行的软件通常存储在非易失性程序存储器104中,诸如闪存或eeprom,即,存储器104被配置为存储处理单元102的固件,其中固件包括要由微处理器102执行的软件指令。相反,诸如随机存取存储器(ram)等易失性存储器104b可以用于存储临时数据。

9、通常,处理系统10还包括例如选自以下各项中的一项或多项(硬件)资源/外围设备106:

10、-一个或多个通信接口,例如,用于经由通信系统20来交换数据,诸如通用异步接收器/传输器(uart)、串行外围接口总线(spi)、集成电路间(i2c)、控制器局域网(can)总线和/或以太网接口、和/或调试接口;和/或

11、-一个或多个模数转换器和/或数模转换器;和/或

12、-一个或多个专用数字组件,诸如硬件定时器和/或计数器、或密码协处理器;和/或

13、-一个或多个模拟组件,诸如比较器、传感器,诸如温度传感器等;和/或

14、-一个或多个混合信号组件,诸如pwm(脉宽调制)驱动器。

15、资源106通常经由相应通信接口1062连接到通信系统114。例如,接口1062中的一个或多个可以经由外围桥接器107连接到通信系统114。例如,为此目的,通信系统实际上可以包括高级微控制器总线架构(amba)高性能总线(ahb)114、以及用于经由外围桥接器107将资源/外围设备106连接到amba ahb总线114的高级外围总线(apb)114b。通常,通信接口1062至少包括从接口。例如,这样处理核心102可以向资源106发送请求,并且资源返回给定数据。通常,通信接口1062中的一个或多个还可以包括相应主接口。例如,在资源必须开始通信以便经由(读取和/或写入)请求与连接到通信系统114的另一电路(诸如资源106或处理核心102)交换数据的情况下,这种通常被标识为集成直接存储器访问(dma)控制器的主接口可以是有用的。

16、如图2所示,通常,这样的处理系统10还包括例如用保险丝实现的一次性可编程(otp)存储器120。例如,这种otp存储器120可以用于存储处理系统的配置数据。通常,存储到otp存储器120的配置数据经由以下方式来读取:

17、-由微处理器1020执行的软件指令;和/或

18、-被配置为至少部分读取otp存储器120的内容的硬件配置电路108。

19、例如,存储到otp存储器120的配置数据可以包括第一组配置数据,该第一组配置数据包括以下中的一项或多项:

20、-校准数据,

21、-引导信息;

22、-一个或多个资源106的配置数据,诸如以太网通信接口106的媒体访问控制(mac)地址;

23、-处理系统10的生命周期数据;

24、-安全配置数据,例如,用于启用或禁用存储器104、104b和/或120中的存储器位置、和/或处理系统的调试接口;和/或

25、-由密码协处理器使用的密码数据,诸如一个或多个密码密钥和/或公共和私有证书。

26、第一组配置数据中的这样的配置数据通常存储到otp存储器120内的专用存储器位置,并且在处理系统10接通时经由硬件配置电路108来读取。然而,otp存储器120通常也可以用于存储第二组配置数据,该第二组配置数据可以用于存储用户和/或产品特定数据。通常,第二组配置数据不是经由硬件配置电路108读取的,而是可以经由由微处理器1020执行的软件指令来读取。

27、因此,通常,otp存储器120以某种方式连接到通信系统114,例如经由存储器控制器100和/或外围桥接器107和/或直接连接。因此,以这种方式,微处理器1020可以通过向通信系统114发送读取请求来从otp存储器120中读取数据,其中读取请求分别包括:

28、-由存储器控制器100管理的地址;

29、-由外围桥接器107管理的地址;

30、-直接是与otp存储器120的接口相关联的地址。

31、类似地,硬件配置电路108可以经由通信系统114与otp存储器120通信,或者直接经由存储器控制器100与外围桥接器107或otp存储器120通信。

32、因此,如图3所示,otp存储器120包括otp存储器区域1200,otp存储器区域1200包括多个存储器插槽otp1、otp2、……、otpn,其中每个存储器插槽具有给定比特数目的给定字大小,诸如8、16、32或64个比特。此外,otp存储器120包括通信接口1202,通信接口1202例如用于将otp存储器120连接到通信系统114,诸如用于将otp存储器120连接到外围总线114b的外围总线接口1202。

33、因此,在所考虑的示例中,otp存储器120可以经由接口1202接收读取请求,其中读取请求包括指示存储器插槽otp1、otp2、……、otpn中的给定存储器插槽的数据,诸如地址。因此,控制电路1204可以从存储器区域1200中读取相应数据,将所读取的数据存储到寄存器1206,并且通信接口1202可以将所存储的数据返回到寄存器1206。

34、如图3所示,这种otp存储器120通常包括一个或多个影子寄存器1208。在这种情况下,otp存储器120通常接收指示处理系统10已经接通的信号pok。响应于该信号pok,控制电路1204从otp存储器区域1200中读取数据,并且将所读取的数据存储到影子寄存器1206。通常,一旦完成读取操作,控制电路1204就断言信号otp_done,例如,该信号可以用于启动硬件配置电路108。因此,在这种情况下,当接收到读取请求时,通信接口1202可以从影子寄存器1208中读取数据,从而加速对被存储到otp存储器120的数据的访问。通常,如图3示意性地所示,当存储到影子寄存器1208中的一个或多个的数据被直接提供给处理系统10的一个或多个其它电路时,也可以使用这样的影子寄存器1208,即,不经过通信系统114和/或114b。例如,这可以应用于安全和/或密码配置数据,这些数据优选地不经由通信通道114和/或114b来传输。

35、通常,在一些otp存储器120中,并非所有存储器位置都确实具有相关联的相应影子寄存器1208,而是仅存储器位置otp1、otp2、……、otpn的一部分/子集被传输到相应影子寄存器1208,诸如被配置为由硬件配置电路108读取的存储器位置,而其它存储器位置otp1、otp2、……、otpn可以要求控制电路1204首先从相应存储器位置1200中读取数据,并且将数据存储到(共享)寄存器1206。

36、如图3所示,这种otp存储器120通常还包括一个或多个另外的通信接口,诸如:

37、-用于与另一电路进行认证的通信接口1210,诸如coresight认证接口;和/或

38、-用于处理系统10的调试接口的通信接口1212,诸如jtag接口,其例如可以用于将数据编程到存储器区域1200。

39、例如,这种otp存储器120在stm32mp1引导和安全控制器(bsec)的上下文中是已知的。

40、发明人已经观察到,经由影子寄存器1208的这样的预加载机制可能相当低效,特别是在处理系统10使用低功率模式的情况下,其中处理系统10在执行给定任务之后关断,并且响应于给定事件而再次接通。事实上,在这种情况下,处理系统10、特别是硬件配置电路108和/或期望从otp存储器120接收数据的其它电路在信号otp_done被断言之前不能被启动。在这点上,典型的otp存储器120可能需要例如每字10微秒的读取时间。因此,当使用更大的otp存储器(诸如具有超过1000个比特的otp存储器)时,处理系统10的引导时间显著增加。此外,在每次引导时加载密码数据也可能使处理系统10面临安全风险。

技术实现思路

1、实施例提供了用于更高效地管理otp存储器的解决方案。

2、如前所述,本公开的各种实施例涉及一种被配置为管理otp存储器区域的otp存储器控制器,例如,其为集成电路的形式。具体地,在各种实施例中,otp存储器区域包括给定数目n个存储器插槽。在各种实施例中,otp存储器控制器包括数据寄存器和给定数目k个影子寄存器,其中数目k小于数目n。通信接口被配置为至少接收请求给定存储器插槽的数据的读取请求。

3、具体地,在各种实施例中,otp存储器控制器包括被配置为接收预加载开始信号和影子寄存器预加载使能信号的控制电路。例如,影子寄存器预加载使能信号可以具有给定数目的n个比特,其中每个比特指示相应存储器插槽是否应当被预加载。备选地,影子寄存器预加载使能信号可以具有给定数目k个比特,其中每个比特指示相应影子寄存器是否应当被预加载。然而,其它编码方案也可以用于影子寄存器预加载使能信号。

4、在各种实施例中,控制电路被配置为管理预加载阶段和数据读取阶段。具体地,响应于预加载开始信号,控制电路被配置为开启预加载阶段。在各种实施例中,在预加载阶段期间,控制电路确定影子寄存器与存储器插槽之间的映射。例如,出于这个目的,控制电路可以接收影子寄存器映射信号,并且根据影子寄存器映射信号来确定给定数目k个影子寄存器与给定数目n个存储器插槽之间的映射。类似的影子寄存器映射信号也可以仅在控制电路的合成过程中使用,由此相应映射例如经由组合逻辑电路来实现。

5、接下来,控制电路根据影子寄存器预加载使能信号来为每个影子寄存器确定相应影子寄存器是否应当被预加载。例如,响应于确定影子寄存器应当被预加载,控制电路可以从映射到影子寄存器的存储器插槽向相应影子寄存器传输数据。最后,一旦基于影子寄存器预加载使能信号预加载影子寄存器,控制电路就断言预加载结束信号并且开启数据读取阶段。

6、在各种实施例中,在数据读取阶段,控制电路被配置为经由通信接口接收读取请求,并且选择在读取请求中指示的相应存储器位置。接下来,控制电路确定所选择的存储器位置是否被映射到影子寄存器。具体地,响应于确定所选择的存储器位置被映射到影子寄存器,控制电路选择映射到所选择的存储器位置的影子寄存器,并且确定所选择的影子寄存器是否已经被预加载。在各种实施例中,响应于确定所选择的影子寄存器已经被预加载,控制电路经由通信接口直接传输存储到所选择的影子寄存器的数据,即,不访问otp存储器区域。相反,响应于确定所选择的影子寄存器尚未被预加载,控制电路从所选择的存储器插槽向所选择的影子寄存器传输数据,并且然后经由通信接口传输存储到所选择的影子寄存器的数据。相反,响应于确定所选择的存储器位置未被映射到影子寄存器,控制电路可以从所选择的存储器插槽向数据寄存器传输数据,并且然后经由通信接口传输存储到数据寄存器的数据。

7、在各种实施例中,控制电路还可以管理数据写入/编程阶段。在这种情况下,控制电路可以被配置为经由通信接口接收写入请求,并且选择在写入请求中指示的相应存储器位置,其中写入请求包括要存储到所选择的存储器位置的相应数据。例如,在各种实施例中,控制电路可以确定所选择的存储器位置是否被映射到影子寄存器。响应于确定所选择的存储器位置被映射到影子寄存器,控制电路可以选择映射到所选择的存储器单元的影子寄存器,将数据存储到所选择的影子寄存器,并且将存储到所选择的影子寄存器的数据编程到所选择的存储器位置。相反,响应于确定所选择的存储器位置没有映射到影子寄存器,控制电路可以将数据存储到数据寄存器,并且将存储到数据寄存器的数据编程到所选择的存储器位置。

8、例如,这样的otp存储器控制器可以用于具有多个电源域的处理系统中。例如,在各种实施例中,这样的处理系统包括电源电路,该电源电路被配置为接收输入电压并且提供第一电源电压和第二电源电压,其中电源电路被配置为当低功率控制信号被解除断言时,选择性地启用第一电源电压并且当低功率控制信号被断言时禁用第一电源电压。

9、在各种实施例中,处理系统的第一子电路被配置为由第一电源电压供电。具体地,第一子电路包括otp存储器区域和otp存储器控制器。在各种实施例中,第一子电路还包括电源监测电路、数字处理电路和至少第一资源,电源监测电路被配置为当第一电源电压超过给定阈值电压时断言预加载开始信号,至少第一资源连接到数字处理电路并且被布置为从otp存储器接收第一配置数据。例如,为此目的,处理系统可以包括硬件配置电路,和/或配置数据可以经由数字处理电路来读取。在各种实施例中,第一子电路还包括被配置为响应于预加载结束信号而启动数字处理电路的复位管理电路。

10、在各种实施例中,处理系统还包括被配置为由第二电源电压供电的第二子电路。在各种实施例中,第二子电路包括被配置为生成低功率控制信号的电源管理电路,其中电源管理电路被配置为响应于从数字处理电路接收的请求而断言低功率控制信号,并且响应于事件信号而解除断言低功率控制信号。在各种实施例中,第二子电路还包括连接到数字处理电路并且被布置为接收第二配置数据的至少一个第二资源。

11、具体地,在各种实施例中,otp存储器控制器被配置为将otp存储器的被配置为存储第一配置数据的第一存储器插槽映射到第一影子寄存器并且将otp存储器的被配置为存储第二配置数据的第二存储器插槽映射到第二影子寄存器。具体地,在这种情况下,响应于处理系统的接通,处理系统经由电源监测电路断言预加载开始信号和设置预加载使能信号,以便将第一配置数据从第一存储器插槽预加载到第一影子寄存器。接下来,响应于预加载结束信号,处理系统从第一影子寄存器向第一资源传输第一配置数据并且从第二影子寄存器向第二资源传输第二配置数据。

12、在各种实施例中,数字处理电路然后向电源管理电路发送请求以便断言低功率控制信号,从而禁用第一电源电压并且关断第一子电路。响应于事件信号,电源管理电路再次解除断言低功率控制信号,从而启用第一电源电压并且接通第一子电路。

13、在各种实施例中,响应于接通第一子电路,处理系统经由电源监测电路再次断言预加载开始信号。然而,这一次,处理系统设置预加载使能信号,以便将第一配置数据从第一存储器插槽预加载到第一影子寄存器并且禁用第二配置数据从第二存储器插槽到第二影子寄存器的预加载。接下来,响应于预加载结束信号,处理系统从第一影子寄存器向第一资源传输第一配置数据并且禁止第二配置数据从第二影子寄存器到第二资源的传输。

14、因此,当从低功率模式返回时,仅由第一子电路使用的配置数据可以由otp存储器控制器预加载,并且处理系统可以仅传输第一子电路的配置数据。

15、例如,在各种实施例中,处理系统(例如,第二子电路)出于这个目的而包括被配置为生成预加载使能信号的电路。例如,该电路可以根据从第一资源接收的第一信号和/或从第二资源接收的第二信号来生成预加载使能信号。例如,第一信号可以指示第一资源是否已经存储第一配置数据,并且第二信号可以指示第二资源是否已经存储第二配置数据。

16、另外地或备选地,该电路可以从可选配置电路接收第三信号,该可选配置电路被配置为从第一影子寄存器向第一资源传输第一配置数据并且从第二影子寄存器向第二资源传输第二配置数据。例如,第三信号可以指示第一配置数据是否已经从第一影子寄存器传输到第一资源和/或第二配置数据是否已经从第二影子寄存器传输到第二资源。

17、另外地或备选地,该电路可以从数字处理电路接收第四信号,其中第四信号指示是否需要预加载第一配置数据和/或是否需要预加载第二配置数据。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182655.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表