阻变式存储器的数据写入操作方法及装置与流程

- 国知局

- 2024-07-31 19:40:26

本发明涉及半导体,特别涉及一种阻变式存储器的数据写入操作方法和一种阻变式存储器的数据写入操作装置。

背景技术:

1、相关技术中,如图1所示,针对存储应用的阻变式存储器(resistive randomaccess memory,rram)阵列操作,一般的,当字线wl接入恒定电压、位线bl接入驱动信号、源线sl接地时,阻变式存储器的状态由高阻态变为低阻态,写入1;当字线wl接入恒定电压、位线bl接地、源线sl接入驱动信号,阻变式存储器的状态由低阻态变为高阻态,写入0;对应的写入操作如图2所示,通过等电压脉冲激励的方式,当施加激励后需确认存储器单元的阻值是否符合设定要求,如不符合则继续施加脉冲直至符合设定或者达到脉冲次数上限。

2、但是,现有的写入操作由于电路实际存在的ir drop及存储阵列中存储单元的物理结构差异(来自于制程),不可避免地存在一定比例的存储单元在限定的脉冲次数内仍没有达到设定阻值,称为tailing bit;其中,图3表明没有“操作到位”的存储单元发生退化(即被写入的阻态随着时间变化发生漂移)的概率较高,易引起误码;另外,如图4所示,采用现有的写入操作,花费在操作tailing bit的时间远大于正常存储单元的操作,从而导致效率较低。

技术实现思路

1、本发明旨在至少在一定程度上解决上述技术中的技术问题之一。为此,本发明的一个目的在于提出一种阻变式存储器的数据写入操作方法,通过判断累计的脉冲次数筛选出tailing bit,并采用长脉冲和放开限流的方式进一步处理,从而在提高数据保持特性的同时节省操作时间,进而提高写入效率。

2、本发明的第二个目的在于提出一种计算机可读存储介质。

3、本发明的第三个目的在于提出一种芯片。

4、本发明的第四个目的在于提出一种计算机程序产品。

5、本发明的第五个目的在于提出一种阻变式存储器的数据写入操作装置。

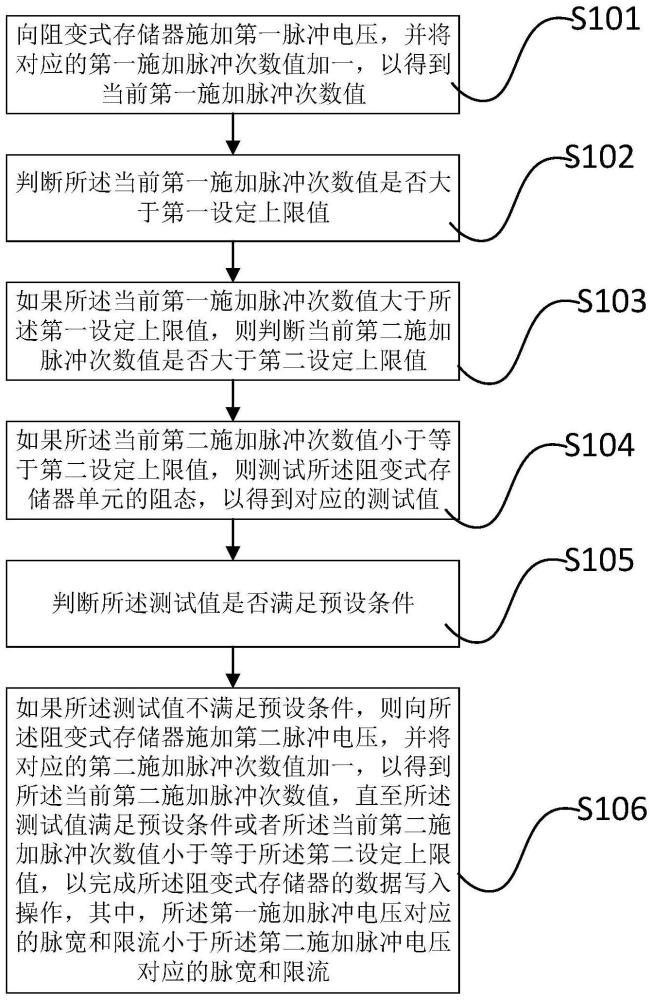

6、为达到上述目的,本发明第一方面实施例提出了一种阻变式存储器的数据写入操作方法,包括以下步骤:向阻变式存储器施加第一脉冲电压,并将对应的第一施加脉冲次数值加一,以得到当前第一施加脉冲次数值;判断所述当前第一施加脉冲次数值是否大于第一设定上限值;如果所述当前第一施加脉冲次数值大于所述第一设定上限值,则判断当前第二施加脉冲次数值是否大于第二设定上限值;如果所述当前第二施加脉冲次数值小于等于第二设定上限值,则测试所述阻变式存储器单元的阻态,以得到对应的测试值;判断所述测试值是否满足预设条件;如果所述测试值不满足预设条件,则向所述阻变式存储器施加第二脉冲电压,并将对应的第二施加脉冲次数值加一,以得到所述当前第二施加脉冲次数值,直至所述测试值满足预设条件或者所述当前第二施加脉冲次数值小于等于所述第二设定上限值,以完成所述阻变式存储器的数据写入操作,其中,所述第一施加脉冲电压对应的脉宽和限流小于所述第二施加脉冲电压对应的脉宽和限流。

7、根据本发明实施例的阻变式存储器的数据写入操作方法,首先,向阻变式存储器施加第一脉冲电压,并将对应的第一施加脉冲次数值加一,以得到当前第一施加脉冲次数值;接着,判断当前第一施加脉冲次数值是否大于第一设定上限值;如果当前第一施加脉冲次数值大于第一设定上限值,则判断当前第二施加脉冲次数值是否大于第二设定上限值;如果当前第二施加脉冲次数值小于等于第二设定上限值,则测试阻变式存储器单元的阻态,以得到对应的测试值;然后,判断测试值是否满足预设条件;如果测试值不满足预设条件,则向阻变式存储器施加第二脉冲电压,并将对应的第二施加脉冲次数值加一,以得到当前第二施加脉冲次数值,直至测试值满足预设条件或者当前第二施加脉冲次数值小于等于第二设定上限值,以完成阻变式存储器的数据写入操作,其中,第一施加脉冲电压对应的脉宽和限流小于第二施加脉冲电压对应的脉宽和限流;由此,通过判断累计的脉冲次数筛选出tailing bit,并采用长脉冲和放开限流的方式进一步处理,从而在提高数据保持特性的同时节省操作时间,进而提高写入效率。

8、另外,根据本发明上述实施例提出的阻变式存储器的数据写入操作方法还可以具有如下附加的技术特征:

9、可选地,如果所述当前第一施加脉冲次数值小于等于所述第一设定上限值,则测试所述阻变式存储器单元的阻态,以得到对应的测试值,并判断所述测试值是否满足预设条件,如果所述测试值满足预设条件,则完成所述阻变式存储器的数据写入操作,如果所述测试值不满足预设条件,则继续向所述阻变式存储器施加第一脉冲电压,直至所述测试值满足预设条件。

10、可选地,如果所述当前第二施加脉冲次数值大于所述第二设定上限值,则完成所述阻变式存储器的数据写入操作,并判断写入失败。

11、可选地,如果所述测试值满足预设条件,则完成所述阻变式存储器的数据写入操作,并判断写入成功。

12、可选地,判断所述测试值是否满足预设条件,包括:判断所述测试值是否大于等于第一设定阻值且小于等于第二设定阻值,其中,所述第一设定阻值小于所述第二设定阻值。

13、可选地,所述第一施加脉冲次数值和所述第二施加脉冲次数值的初始值均设定为零。

14、为达到上述目的,本发明第二方面实施例提出的一种计算机可读存储介质,其上存储有阻变式存储器的数据写入操作程序,该阻变式存储器的数据写入操作程序被处理器执行时实现如上述的阻变式存储器的数据写入操作方法。

15、根据本发明实施例的计算机可读存储介质,通过存储阻变式存储器的数据写入操作程序,以便处理器在执行该阻变式存储器的数据写入操作程序时实现如上述的阻变式存储器的数据写入操作方法,从而在提高数据保持特性的同时节省操作时间,进而提高写入效率。

16、为达到上述目的,本发明第三方面实施例提出的一种芯片,包括存储器、处理器及存储在存储器上并可在处理器上运行的阻变式存储器的数据写入操作程序,所述处理器执行所述程序时,实现如上述的阻变式存储器的数据写入操作方法。

17、根据本发明实施例的芯片,通过存储器存储可在处理器上运行的阻变式存储器的数据写入操作程序,以便处理器在执行该程序时,实现如上述的阻变式存储器的数据写入操作方法,从而在提高数据保持特性的同时节省操作时间,进而提高写入效率。

18、为达到上述目的,本发明第四方面实施例提出的一种计算机程序产品,包括计算机程序,该计算机程序在被处理器执行时实现如上述的阻变式存储器的数据写入操作方法。

19、根据本发明实施例的计算机程序产品,在被处理器执行时实现如上述的阻变式存储器的数据写入操作方法,从而在提高数据保持特性的同时节省操作时间,进而提高写入效率。

20、为达到上述目的,本发明第五方面实施例提出的一种阻变式存储器的数据写入操作装置,包括第一激励模块,用于向阻变式存储器施加第一脉冲电压,并将对应的第一施加脉冲次数值加一,以得到当前第一施加脉冲次数值;第一判断模块,用于判断所述当前第一施加脉冲次数值是否大于第一设定上限值;第二判断模块,用于如果所述当前第一施加脉冲次数值大于所述第一设定上限值,则判断当前第二施加脉冲次数值是否大于第二设定上限值;测试模块,用于如果所述当前第二施加脉冲次数值小于等于第二设定上限值,则测试所述阻变式存储器单元的阻态,以得到对应的测试值;第三判断模块,用于判断所述测试值是否满足预设条件;第二激励模块,用于如果所述测试值不满足预设条件,则向所述阻变式存储器施加第二脉冲电压,并将对应的第二施加脉冲次数值加一,以得到所述当前第二施加脉冲次数值,直至所述测试值满足预设条件或者所述当前第二施加脉冲次数值小于等于所述第二设定上限值,以完成所述阻变式存储器的数据写入操作,其中,所述第一施加脉冲电压对应的脉宽和限流小于所述第二施加脉冲电压对应的脉宽和限流。

21、根据本发明实施例的一种阻变式存储器的数据写入操作装置,通过判断累计的脉冲次数筛选出tailing bit,并采用长脉冲和放开限流的方式进一步处理,从而在提高数据保持特性的同时节省操作时间,进而提高写入效率。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183527.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表