高带宽DDR双列直插式存储模块、存储系统及其操作方法与流程

- 国知局

- 2024-07-31 19:42:11

本发明属于存储器,更具体地,涉及一种高带宽ddr双列直插式存储模块、存储系统及其操作方法。

背景技术:

1、目前广泛使用的双数据速率(double data rate,ddr)同步动态随机存取存储器(synchronous dynamic random access memory,sdram)(也称为dram)标准适用于ddr4和ddr5存储器,并提供了一个可支持双列直插式存储模块(dual-in-line memory module,dimm)设备的通道,其可以在时钟的上升沿和下降沿记录数据。

2、由于dram技术的不断发展,dram和主机/控制器之间的io速度差距正在逐步增大。但由于封装、dimm和pcb上的路由资源有限,添加更多ddr通道以增加dimm带宽并不是一个有效的解决方案。

3、在标准lrdimm系统中,输入命令和地址(dca)接口(即主机与时钟锁存驱动器(rcd)之间的接口)的频率等于输出命令和地址(qca)接口(即rcd与dram之间的接口)的频率。数据缓冲器(db)直接在dram和主机接口之间转发数据。

4、业界提出了一种高带宽dimm(hbdimm),将dca接口的数据速率提高一倍,同时将qca接口的频率相对于dca接口频率降低一半。将hbdimm的同一通道划分为a侧和b侧,称为伪通道(pcs),两个伪通道的qca接口由dca进行逻辑控制,使qca宽度为dca的2倍,从而平衡了dca/qca的带宽。qca的半频使得现有dram系统带宽加倍成为可能。但由于dram的io速度仍受限于现有dram的发展进程,导致dram和主机/控制器之间的io速度差距难以进一步缩小。

技术实现思路

1、针对现有技术的以上缺陷或改进需求,本发明提供了一种高带宽ddr双列直插式存储模块,能够有效提升数据的传输效率,从而有效解决dram和主机/控制器之间的io速度差距的问题。

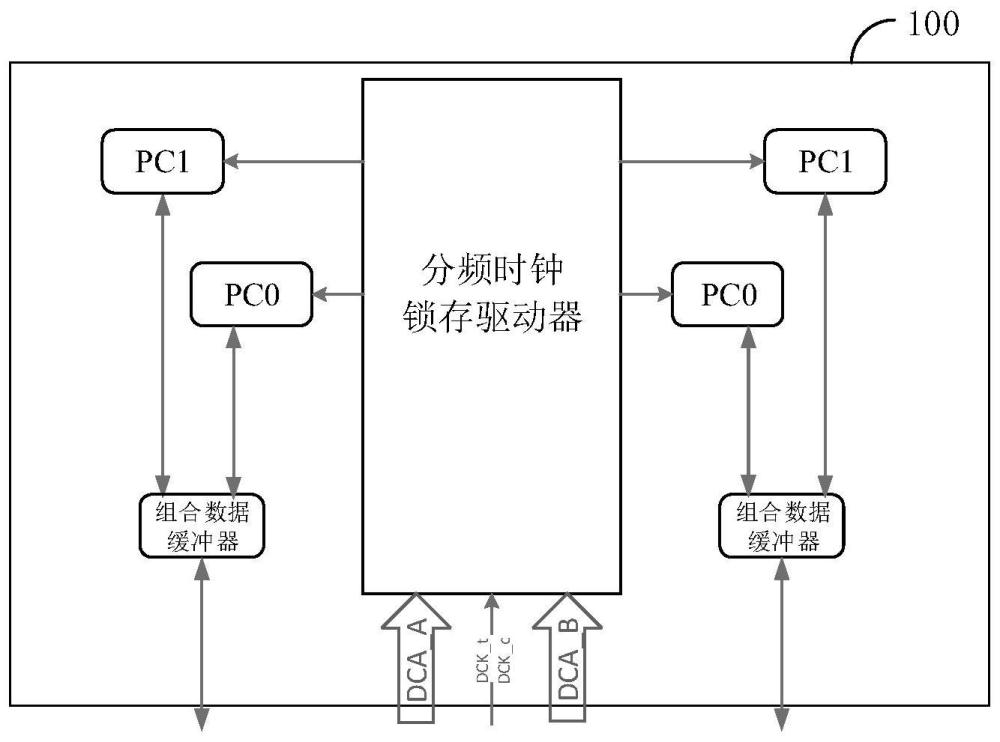

2、为实现上述目的,按照本发明的一个方面,提供了一种高带宽ddr双列直插式存储模块,包括:第一子通道、第二子通道、分频时钟锁存驱动器和组合数据缓冲器,其中,每个所述子通道包括第一伪通道和第二伪通道,每个伪通道包括多个dram芯片颗粒;所述分频时钟锁存驱动器用于响应于主机发送的指令确定指令模式,并根据所述指令模式将所述指令发送至所述第一伪通道和/或所述第二伪通道;所述组合数据缓冲器用于将所述第一伪通道和所述第二伪通道的数据进行交织。

3、在一些实施方式中,所述分频时钟锁存驱动器还用于响应于其输入时钟周期,与所述主机进行奇偶相位同步,其中,所述分频时钟锁存驱动器的第奇数个输入时钟周期对应所述主机的第奇数个相位,所述分频时钟锁存驱动器的第偶数个输入时钟周期对应所述主机的第偶数个相位。

4、在一些实施方式中,当所述主机发送的是双周期指令时,所述分频时钟锁存驱动器还用于根据所述双周期指令中的至少一个标志位从多个不同指令模式中选择一种指令模式;当所述主机发送的是单周期指令时,所述分频时钟锁存驱动器还用于根据所述单周期指令所处的奇偶相位将所述指令发送至所述第一伪通道和/或所述第二伪通道。

5、在一些实施方式中,所述指令模式包括广播模式,所述分频时钟锁存驱动器还用于在所述广播模式下,将所述指令同时发送到所述第一伪通道和所述第二伪通道。

6、在一些实施方式中,在所述广播模式下,所述第一伪通道和所述第二伪通道用于响应于所述指令,同时将数据发送至所述组合数据缓冲器。

7、在一些实施方式中,在所述广播模式下,所述组合数据缓冲器用于直接将所述第一伪通道和所述第二伪通道的数据进行交织。

8、在一些实施方式中,所述指令模式包括定向模式,所述分频时钟锁存驱动器还用于在所述定向模式下,将所述指令分别发送到所述第一伪通道或所述第二伪通道。

9、在一些实施方式中,在所述定向模式下,所述第一伪通道和所述第二伪通道用于响应于所述指令,分别将数据发送至所述组合数据缓冲器。

10、在一些实施方式中,在所述定向模式下,所述组合数据缓冲器用于在其中一个伪通道的数据未到时,将另一伪通道的数据与空数据进行交织。

11、在一些实施方式中,在所述定向模式下,所述分频时钟锁存驱动器还用于根据所述指令所处的奇偶相位和/或至少一个标志位来确定将所述指令发送到所述第一伪通道或所述第二伪通道。

12、在一些实施方式中,所述指令模式包括动态模式,所述分频时钟锁存驱动器还用于在所述动态模式下,将所述指令同时或分别发送到所述第一伪通道和所述第二伪通道。

13、在一些实施方式中,在所述动态模式下,所述分频时钟锁存驱动器还用于根据奇偶相位确定将所述指令发送到所述第一伪通道或所述第二伪通道。

14、在一些实施方式中,所述分频时钟锁存驱动器具有标志位寄存器,用于当其他设备需要向所述分频时钟锁存驱动器发送指令时,通过所述标志位寄存器与所述分频时钟锁存驱动器进行奇偶相位同步。

15、按照本发明的另一个方面,提供了一种存储系统,包括cpu和上述高带宽ddr双列直插式存储模块。

16、按照本发明的又一个方面,提供了一种存储系统的操作方法,所述存储系统包括主机和高带宽ddr双列直插式存储模块,该操作方法包括:

17、所述主机与所述高带宽ddr双列直插式存储模块的分频时钟锁存驱动器进行奇偶相位同步;

18、所述主机向所述分频时钟锁存驱动器发送指令;

19、所述分频时钟锁存驱动器根据所述指令确定指令模式,并根据所述指令模式或所述指令所处的奇偶相位将所述指令发送至所述高带宽ddr双列直插式存储模块的第一伪通道和/或第二伪通道,其中,每个伪通道包括多个dram芯片颗粒。

20、在一些实施方式中,当所述分频时钟锁存驱动器工作于广播模式时,所述主机在偶相位向所述分频时钟锁存驱动器发送指令,且在等待与所述指令等长的输入时钟周期后,继续在偶相位向所述分频时钟锁存驱动器发送指令;所述分频时钟锁存驱动器将接收到的所述指令同时发送到所述第一伪通道和所述第二伪通道,其中,所述分频时钟锁存驱动器的第偶数个输入时钟周期对应所述主机的第偶数个相位。

21、在一些实施方式中,当所述分频时钟锁存驱动器工作于定向模式或动态模式时,所述分频时钟锁存驱动器根据单周期指令所处的奇偶相位确定将所述单周期指令发送到所述第一伪通道或所述第二伪通道。

22、在一些实施方式中,所述主机将双周期指令中的至少一个预留位配置为所述标志位,用于指示所述分频时钟锁存驱动器的指令模式,和/或指示所述分频时钟锁存驱动器将所述指令发送到所述第一伪通道或所述第二伪通道。

23、在一些实施方式中,当所述分频时钟锁存驱动器工作于动态模式时,所述主机对所述第一伪通道和所述第二伪通道的数据进行交织/解交织。

24、在一些实施方式中,在所述高带宽ddr双列直插式存储模块的初始化阶段,或时钟关闭的自刷新阶段,所述主机与所述分频时钟锁存驱动器进行奇偶相位同步。

25、总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:通过分频时钟锁存驱动器根据不同的指令模式和/或指令所处的奇偶相位,对应将指令同时或分别发送至多个伪通道,实现数据更快速有效地读取;通过与主机进行奇偶相位同步,根据接收到指令的奇偶相位实现对指令的准确响应,且可根据指令的奇偶相位或标志位将指令发送至对应的伪通道,整体提升信号读取和传输的性能;无需改变原有的指令格式和发送方式,适用于更多的应用场景,具有很好的兼容性。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183589.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表