一种SRAM存储单元电路及其组成的静态存储器的工作模式的制作方法

- 国知局

- 2024-07-31 19:42:43

本发明涉及一种静态存储器的存储单元电路,属于集成电路领域,具体地说,涉及一种sram存储单元电路及其组成的静态存储器的工作模式。

背景技术:

1、sram存储单元电路通常采用一对反相器进行闭环连接,以存储信息需要多个晶体管,比如包含6个晶体管的sram存储单元电路和包含8个晶体管的sram存储单元电路等。然而,传统的sram存储单元电路存在一些问题,比如组成较大,占用空间较多,导致器件体积相对庞大;其次,成本较高,制造和维护费用相对昂贵;此外,功耗较大,不利于能源效率;同时,传统sram存储单元电路在写入数据时速度较慢,且稳定性不足,容易受到外部因素的影响,这些问题与晶体管数量和连接方式密切相关,制约了传统静态随机存储器在性能和可靠性方面的进一步提升。

2、《高稳定性低静态功耗11管sram存储单元设计》,发表于2022年,该文献公开了一种十一管sram静态存储单元,该存储单元相对于传统六管sram存储单元优化了稳定性,降低了功耗,但是受存储单元面积的影响,器件尺寸和该存储单元的读写速度、电路的稳定性等均受到限制。

技术实现思路

1、针对上述存在的问题和现有技术的不足,本发明的目的在于提供一种sram存储单元电路及其组成的静态存储器的工作模式。

2、本发明的技术方案是:一种sram存储单元电路。

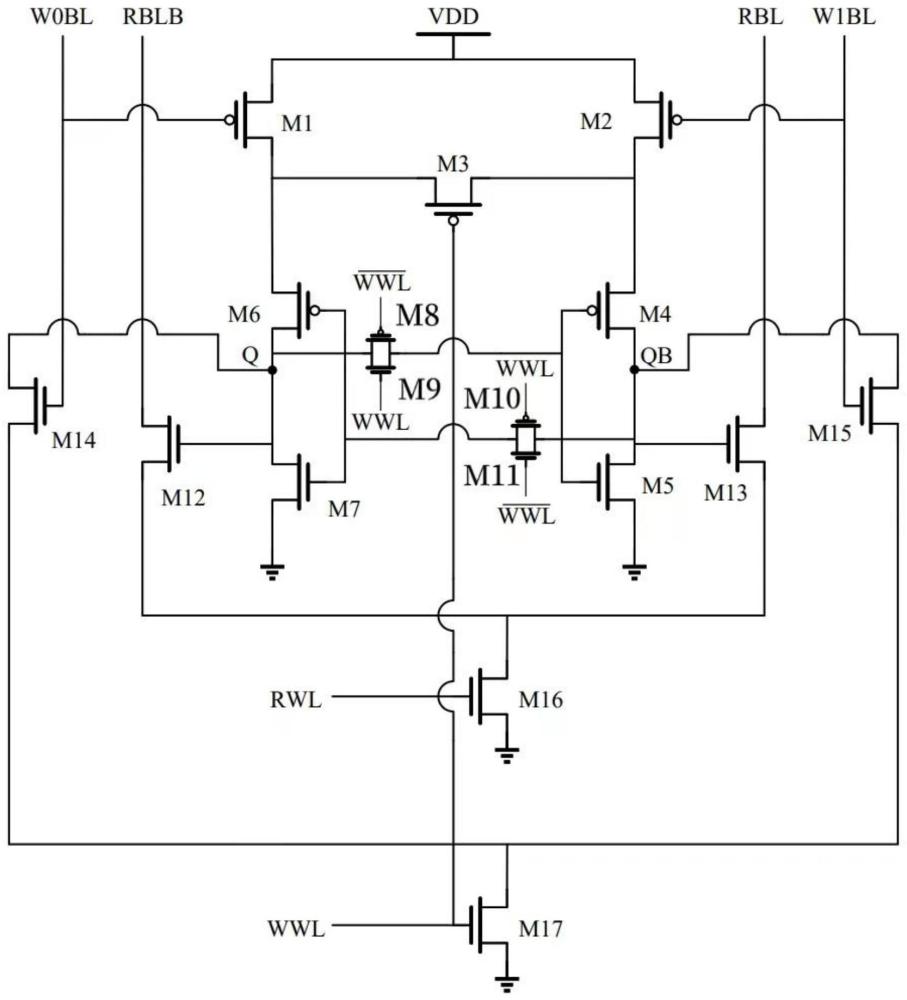

3、所述的存储单元电路包括:场效应晶体管m1,场效应晶体管m2,场效应晶体管m3,场效应晶体管m4,场效应晶体管m5,场效应晶体管m6,场效应晶体管m7,场效应晶体管m8,场效应晶体管m9,场效应晶体管m10,场效应晶体管m11,场效应晶体管m12,场效应晶体管m13,场效应晶体管m14,场效应晶体管m15,场效应晶体管m116和场效应晶体管m17;场效应晶体管m1的源极、漏极和场效应晶体管m2的源极、漏极连接在一起,场效应晶体管m1和场效应晶体管m2的栅极分别由甲列选择信号线w0bl与乙列选择信号线w1bl控制,衬底与电源正极vdd连接,构成能够切断电源通路与存储节点的开关;场效应晶体管m3的源极、漏极分别与场效应晶体管m1和场效应晶体管m2相连,场效应晶体管m3的衬底与电源正极vdd连接,场效应晶体管m3的栅极由甲行选择信号线wwl控制;场效应晶体管m4的漏极与场效应晶体管m5的源极相连,两个场效应晶体管的栅极互相连接,场效应晶体管m4的源极与场效应晶体管m2的漏极连接,场效应晶体管m4的衬底与电源正极vdd连接,场效应晶体管m5的漏极与衬底相连并接地,构成一组反相器;场效应晶体管m6的漏极与场效应晶体管m7的源极相连,场效应晶体管m6的栅极与场效应晶体管m7的栅极互相连接,场效应晶体管m6的源极与场效应晶体管m1的漏极连接,场效应晶体管m6的衬底与电源正极vdd连接,场效应晶体管m7的漏极与衬底相连并接地,构成另一组反相器;两组反相器完全对称,首尾相连,交叉耦合;场效应晶体管m8和场效应晶体管m9的源极、漏极互相连接,场效应晶体管m8的衬底接地,场效应晶体管m9的衬底接电源正极vdd,构成由甲行选择信号线wwl控制的传输门;场效应晶体管m10和场效应晶体管m11的源极、漏极互相连接,构成由甲行选择信号线wwl控制的传输门;场效应晶体管m12和场效应晶体管m13的栅极分别与两组反相器的输出连接,源极分别由丙列选择信号线rblb和丁列选择信号线rbl控制,场效应晶体管m12的漏极和场效应晶体管m13的漏极与场效应晶体管m16的源极连接,衬底接地;场效应晶体管m14的栅极和场效应晶体管m15的栅极分别由甲列选择信号线w0bl与乙列选择信号线w1bl控制,场效应晶体管m14的源极和场效应晶体管m15的源极分别与两组反相器的输出连接,场效应晶体管m14的漏极和场效应晶体管m15的漏极与场效应晶体管m17的源极连接,衬底接地;场效应晶体管m16的栅极由信号线乙行选择信号线rwl控制,场效应晶体管m16的漏极与衬底连接并接地;场效应晶体管m17的栅极由甲行选择信号线wwl控制,场效应晶体管m17的漏极与衬底连接并接地。

4、所述的sram存储单元电路中所述甲行选择信号线wwl和所述乙行选择信号线rwl为行选择信号线,同一行上的信号值相同;所述甲列选择信号线w0bl和所述乙列选择信号线w1bl和所述丁列选择信号线rbl为列选择信号线,同一列上的存储单元的信号赋值相同。

5、一种由sram存储单元电路组成的静态存储器的工作模式,包括如下模式:

6、(1)保持模式:在此模式下,乙行选择信号线rwl、甲行选择信号线wwl、甲列选择信号线w0bl以及乙列选择信号线w1bl均置为0,位线丁列选择信号线rbl和丙列选择信号线rblb预充至电源电压vdd;与经典包含8个场效应晶体管的存储器的读结构相似,采用了双nmos场效应晶体管串联的堆叠结构,以在保持状态时降低泄漏电流;在存储节点与gnd之间存在两个堆叠的nmos场效应晶体管,提高了保持状态时的保持静态噪声容限;

7、(2)读操作模式:在此模式下,乙行选择信号线rwl连接至电源正极vdd,丁列选择信号线rbl和丙列选择信号线rblb预充至电源电压vdd然后放电,甲列选择信号线w0bl与乙列选择信号线w1bl和甲行选择信号线wwl相连均置为0;在读取期间,写部分处于一种类似于传统包含6个场效应晶体管的存储器的保持状态,通过隔离存储节点与位线之间的联系,提升了存储单元的读静态噪声容限;若此时q存储节点存“1”,qb存储节点存“0”,则丁列选择信号线rbl保持高电平不变,丙列选择信号线rblb经过场效应晶体管m12与场效应晶体管m16串联形成的放电通路放电,位线末端的灵敏放大器接将丁列选择信号线rbl与丙列选择信号线rblb上的电压差放大后输出“1”;反之q存储节点存“0”,qb存储节点存“1”,则输出“0”;采用了双位线读结构,降低了灵敏放大器需要放大的电压差,减少了存储单元读取数据所需的功耗,同时对共模噪声有较好的抑制作用;单根位线上的包含15个场效应晶体管的存储单元数目设置为32,以保证在低电源电压环境下更容易区分位线上的读电流与漏电流;

8、(3)写操作模式:在此模式下,乙行选择信号线rwl关闭,丁列选择信号线rbl和丙列选择信号线rblb仍预充至电源电压vdd;甲行选择信号线wwl打开,甲列选择信号线w0bl与乙列选择信号线w1bl则根据所写入的数据开启或断开来决定存储节点q上的数据,写“1”时由乙列选择信号线w1bl控制的场效应晶体管m15打开,甲列选择信号线w0bl控制场效应晶体管m14关断,甲行选择信号线wwl有效,场效应晶体管m17打开,存储节点qb上的电压通过场效应晶体管m15,场效应晶体管m17串联的mos管被gnd下拉,当qb存储节点电压下降至场效应晶体管m6与场效应晶体管m7构成的反相器的阈值电压时,存储节点q的电压值慢慢上升,场效应晶体管m5逐渐被打开继续下拉qb存储节点电压,最终qb存储节点为“0”,q存储节点为“1”,存储单元完成写“1”操作;同理,当写“0”时,甲列选择信号线w0bl控制的场效应晶体管m14打开,乙列选择信号线w1bl场效应晶体管m15关断,甲行选择信号线wwl有效写入控制场效应晶体管m17打开,假设q存储节点存储数据的初始化为“1”,该点电压通过场效应晶体管m14,场效应晶体管m17串联的mos管被gnd下拉,当存储节点q电压下降至场效应晶体管m4与场效应晶体管m5组成的反相器的阈值电压时,存储节点qb电压值缓慢上升,场效应晶体管m7逐渐打开继续下拉q存储节点电压,最后q存储节点为“0”,qb存储节点为“1”;与传统包含6个晶体管的存储器写操作相比,包含15个场效应晶体管的存储单元在写入时增加了能够切断存储节点与电源通路的场效应晶体管m1与场效应晶体管m2,q存储节点电压被下拉时,场效应晶体管m1关断,与电源的通路被切断,场效应晶体管m6变弱,存储节点保持电压的能力大大减弱,q存储节点电压更易被下拉,qb存储节点同上;甲行选择信号线wwl控制分别由场效应晶体管m8和场效应晶体管m9组成的传输门电路及场效应晶体管m10和场效应晶体管m11组成的传输门电路,避免了存储单元在数据与保持状态下噪声容限的下降,同时两组传输门电路平衡了因添加传输门而带来的延时;当写“1”时,甲行选择信号线wwl置“1”,因为电源以及反馈环路被切断,场效应晶体管m4栅极浮空,qb存储节点很容易下拉,q存储节点更容易被上拉至“1”,写“0”时q存储节点被下拉至“0”,场效应晶体管m4与场效应晶体管m5的栅极浮空缓慢下降,qb存储节点逐渐上升至“1”;该存储单元写入时耦合反相器的正反馈被切断,首尾相连的反相器此时更像是一个缓冲器,使得存储节点上的数据写入更加容易,有助于提升数据的写入速度。

9、与现有技术相比,本发明的有益效果是:

10、1.存储节点与电线接地端gnd之间存在两个堆叠的nmos场效应晶体管,有助于保持节点电压的稳定,提升了保持状态时保持静态噪声容限。

11、2.双位线读结构减小了灵敏放大器需要放大的电压差,降低了存储单元读取数据所需的功耗,同时对共模噪声有较好的抑制作用。

12、3.没有了读约束的限制,存储单元的尺寸优化方面只需考虑位线上的电流抗波动能力以及速度即可。

13、4.单根位线上的15管存储单元数目设置为32,保证低电源电压环境下位线上的读电流与漏电流更易区分。

14、5.包含15个场效应晶体管的存储单元在写入时增加了能够切断存储节点与电源通路的开关场效应晶体管m1与开关场效应晶体管m2,提升了存储单元写入数据的稳定性。

15、6.两组传输门电路能够帮助存储单元提升写能力,同时避免了存储单元在数据与保持状态下噪声容限的下降,也可以平衡因添加传输门而带来的延时。

16、7.存储单元写入时耦合反相器的正反馈被切断,首尾相连的反相器此时更像是一个缓冲器,存储节点上的数据写入会更加容易,有助于提升数据的写入速度。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183629.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。