计数控制电路、计数控制方法以及半导体存储器与流程

- 国知局

- 2024-07-31 19:51:16

本公开涉及集成电路,尤其涉及一种计数控制电路、计数控制方法以及半导体存储器。

背景技术:

1、随着半导体技术的不断发展,人们在制造和使用计算机等设备时,对数据的传输速度提出了越来越高的要求。为了获得更快的数据传输速度,应运而生了一系列数据可以双倍速率(double data rate,ddr)传输的存储器等器件。

2、在相关技术中,由于存储器的传输速度越来越快、行锤击(row hammer)等一些原因,存储器中可能会发生错误,这就需要对存储器进行错误检查并及时纠正检查到的错误。以动态随机存取存储器(dynamic random access memory,dram)为例,需要在至少每24小时对dram进行一次完整的错误检查与清除(error check and scrub,ecs)。然而,对于相关技术中的ecs来说,有可能出现24小时内无法完成整个ecs操作的情况,甚至还有可能产生额外功耗,影响了存储器的性能。

技术实现思路

1、本公开实施例提供了一种计数控制电路、计数控制方法以及半导体存储器。

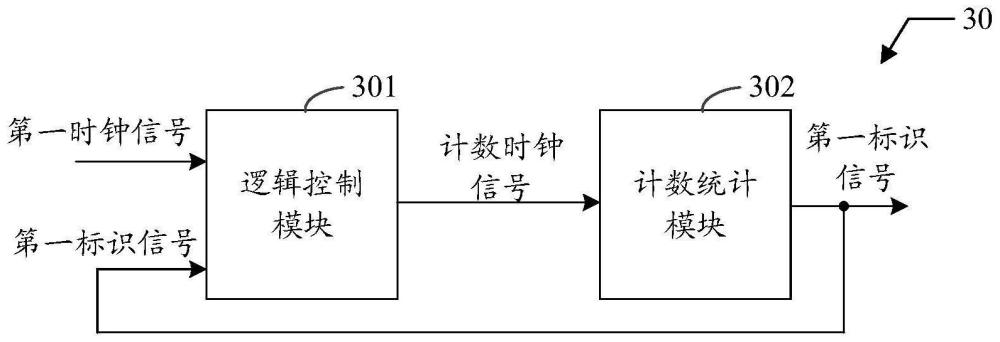

2、第一方面,本公开实施例提供了一种计数控制电路,该计数控制电路包括逻辑控制模块和计数统计模块,且逻辑控制模块的输出端与计数统计模块的时钟端连接,其中:

3、逻辑控制模块,用于接收第一时钟信号和第一标识信号,并在第一标识信号的控制下,根据第一时钟信号生成计数时钟信号;

4、计数统计模块,用于接收计数时钟信号,根据计数时钟信号进行计数,生成第一标识信号,第一标识信号用于指示生成执行第一操作的命令信号;其中,在计数值满足预设条件时,使第一标识信号处于有效状态。

5、在一些实施例中,逻辑控制模块,用于在第一标识信号处于无效状态时,根据第一时钟信号生成计数时钟信号,使计数统计模块对计数时钟信号进行计数;或者,在第一标识信号处于有效状态时,屏蔽第一时钟信号以阻止计数时钟信号的生成,使计数统计模块停止计数。

6、在一些实施例中,逻辑控制模块包括第一驱动模块和第一逻辑模块,其中:

7、第一驱动模块,用于对第一时钟信号进行驱动处理,得到第一中间信号;

8、第一逻辑模块,用于对第一中间信号和第一标识信号进行逻辑运算,得到计数时钟信号。

9、在一些实施例中,所述第一驱动模块包括偶数个级联的第一非门。

10、在一些实施例中,第一逻辑模块包括第一延迟反相模块、第一与非门和第二非门,其中:

11、第一延迟反相模块,用于对第一标识信号进行延迟及反相处理,得到第二中间信号;

12、第一与非门,用于对第一中间信号和第二中间信号进行与非逻辑运算,得到第三中间信号;

13、第二非门,用于对第三中间信号进行非逻辑运算,得到计数时钟信号。

14、在一些实施例中,第一延迟反相模块包括奇数个级联的第三非门。

15、在一些实施例中,计数统计模块,还用于接收计数复位信号,根据计数复位信号进行计数清零,并使第一标识信号处于无效状态。

16、在一些实施例中,计数控制电路还包括复位逻辑模块;其中,复位逻辑模块,用于接收第一命令信号和外部复位信号,对第一命令信号和外部复位信号进行逻辑运算,生成计数复位信号,计数复位信号用于发送给计数统计模块;其中,第一标识信号处于有效状态时,用于指示生成第一命令信号。

17、在一些实施例中,复位逻辑模块包括第一或门;其中,第一或门的第一输入端用于接收外部复位信号,第一或门的第二输入端用于接收第一命令信号,第一或门的输出端用于输出计数复位信号。

18、在一些实施例中,计数统计模块包括计数模块和译码模块,且计数模块的输出端与译码模块的输入端连接,其中:

19、计数模块,用于接收计数时钟信号,根据计数时钟信号进行计数,生成计数信号,计数信号用于表征计数值;

20、译码模块,用于接收计数信号,对计数信号进行译码处理,生成第一标识信号;其中,在计数值满足预设条件时,使第一标识信号处于有效状态。

21、在一些实施例中,计数模块包括同步二进制计数器,同步二进制计数器包括若干个依次级联的计数子模块,且每个计数子模块均包括触发器,每个触发器的时钟端均与计数时钟信号连接,其中:

22、若干个计数子模块,用于接收计数时钟信号,通过各自包含的触发器进行时钟采样处理,输出计数信号;

23、其中,计数信号包括若干个比特位,且若干个计数子模块与计数信号包含的若干个比特位之间具有对应关系。

24、在一些实施例中,在若干个计数子模块中:

25、第一个计数子模块包括第一触发器,第一触发器的输入端与第一触发器的第二输出端连接,第一触发器的时钟端用于接收计数时钟信号,且第一触发器的第一输出端用于输出第一计数信号,且第一计数信号是计数信号中的第0比特位;

26、第二个计数子模块包括第二触发器和第二异或门,第二异或门的第一输入端与第一触发器的第一输出端连接,第二异或门的第二输入端与第二触发器的第一输出端连接,第二异或门的输出端与第二触发器的输入端连接,第二触发器的时钟端用于接收计数时钟信号,且第二触发器的第一输出端用于输出第二计数信号,且第二计数信号是计数信号中的第1比特位;

27、第i个计数子模块包括第i触发器、第i与非门、第i非门和第i异或门,第i与非门的第一输入端与第i-1触发器的第一输出端连接,第i与非门的第二输入端与第i-1异或门的第一输入端连接,第i与非门的输出端与第i非门的输入端连接,第i非门的输出端与第i异或门的第一输入端连接,第i异或门的第二输入端与第i触发器的第一输出端连接,第i异或门的输出端与第i触发器的输入端连接,第i触发器的时钟端用于接收计数时钟信号,且第i触发器的第一输出端用于输出第i计数信号,且第i计数信号是计数信号中的第i-1比特位;其中,i为大于或等于3且小于或等于m的整数,m为正整数。

28、在一些实施例中,计数控制电路还包括命令控制模块,其中:

29、命令控制模块,用于接收第一标识信号和刷新命令信号,以及在第一标识信号处于有效状态时,根据刷新命令信号生成第一命令信号;或者,在第一标识信号处于无效状态时,根据刷新命令信号生成第二命令信号。

30、在一些实施例中,第一命令信号为错误检查与清除ecs命令信号,用于执行ecs操作;第二命令信号为内部刷新信号,用于执行刷新操作。

31、在一些实施例中,刷新命令信号包括下述至少之一:刷新信号和自刷新信号。

32、在一些实施例中,计数控制电路还包括时钟产生电路,其中:

33、时钟产生电路,用于产生第一时钟信号。

34、在一些实施例中,时钟产生电路包括振荡模块和分频模块,其中:

35、振荡模块,用于输出预设频率的第二时钟信号;

36、分频模块,用于对第二时钟信号进行n分频处理,得到第一时钟信号;

37、其中,第一时钟信号的频率为预设频率的n分之一,n为大于零的整数。

38、第二方面,本公开实施例提供了一种计数控制方法,该方法包括:

39、接收第一时钟信号和第一标识信号,并在第一标识信号的控制下,根据第一时钟信号生成计数时钟信号;

40、根据计数时钟信号进行计数,生成第一标识信号,第一标识信号用于指示生成执行第一操作的命令信号;其中,在计数值满足预设条件时,使第一标识信号处于有效状态。

41、第三方面,本公开实施例提供了一种半导体存储器,该半导体存储器包括如第一方面所述的计数控制电路。

42、在一些实施例中,半导体存储器包括动态随机存取存储器dram。

43、本公开实施例提供了一种计数控制电路、计数控制方法以及半导体存储器,该计数控制电路包括逻辑控制模块和计数统计模块,且逻辑控制模块的输出端与计数统计模块的时钟端连接,其中,逻辑控制模块,用于接收第一时钟信号和第一标识信号,并在第一标识信号的控制下,根据第一时钟信号生成计数时钟信号;计数统计模块,用于接收计数时钟信号,根据计数时钟信号进行计数,生成第一标识信号,第一标识信号用于指示生成执行第一操作的命令信号;其中,在计数值满足预设条件时,使第一标识信号处于有效状态。这样,逻辑控制模块在接收第一时钟信号之后,结合第一标识信号进行逻辑运算可以得到用于计数的计数时钟信号,根据该计数时钟信号可以产生第一标识信号,以此产生执行第一操作的命令信号,这时候执行ecs操作的命令产生不受刷新命令的限制,解决了相关技术中只能借助ref_ab进行计数来产生ecs命令信号的技术问题,能够确保24小时完成完整的ecs操作;另外,该计数时钟信号与第一标识信号之间具有逻辑关系,根据第一标识信号的状态可以控制计数统计模块是否停止计数,从而还能够达到减小功耗的目的,最终提升存储器的性能。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184362.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表