记忆体阵列的制作方法

- 国知局

- 2024-07-31 19:53:06

本揭露是关于一种记忆体阵列,特别是关于一种包含多个记忆体单元的记忆体阵列。

背景技术:

1、归因于各种电子部件(例如,晶体管、二极管、电阻器、电容器等)的整合密度的连续改善,半导体工业已经历快速增长。在很大程度上,整合密度的此改善由最小特征尺寸的重复减小导致,如此允许将更多部件整合到给定区域中。

技术实现思路

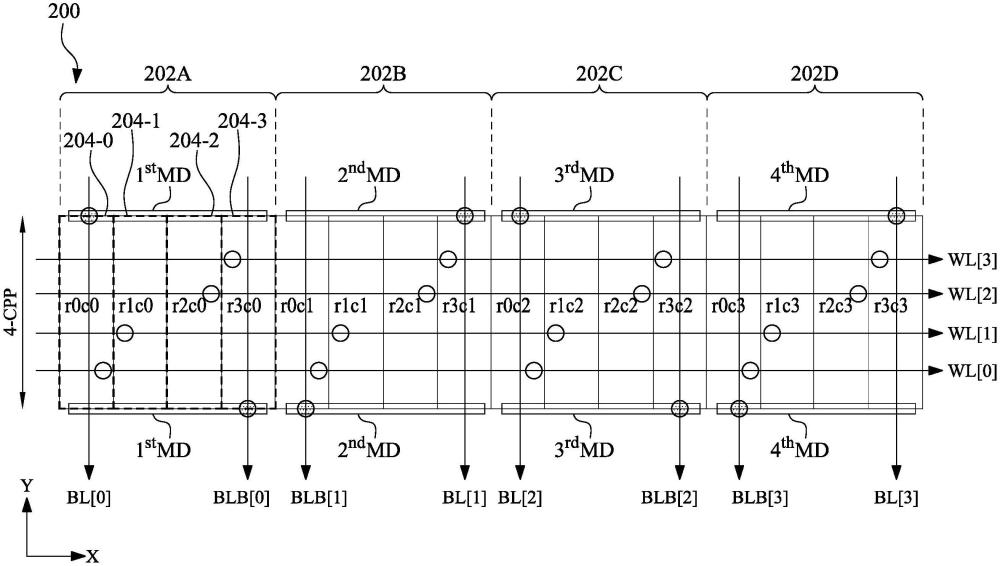

1、本揭露的一实施例提供一种记忆体阵列包含多个记忆体电路,记忆体电路设置在基板上方。记忆体电路的每一者耦接到多个字线中的对应一者及多个位元线对中的对应一者。耦接到字线的四个连续字线及位元线对的第一位元线对的记忆体电路中的前四个记忆体电路沿着单个横向方向在基板上抵靠彼此。

2、本揭露的另一实施例提供一种记忆体阵列包含第一记忆体电路、第二记忆体电路、第三记忆体电路及第四记忆体电路。第一记忆体电路、第二记忆体电路、第三记忆体电路及第四记忆体电路沿着单个横向方向抵靠彼此。第一记忆体电路至第四记忆体电路的每一者包括基于四个接触多晶硅间距晶体管架构形成的多个晶体管。第一记忆体电路至第四记忆体电路分别操作地耦接到第一字线、第二字线、第三字线及第四字线。

3、本揭露的另一实施例提供一种记忆体阵列,包含第一记忆体电路、第二记忆体电路、第三记忆体电路及第四记忆体电路。第一记忆体电路、第二记忆体电路、第三记忆体电路及第四记忆体电路沿着单个横向方向布置在基板上方。第一记忆体电路至第四记忆体电路中的每一者包括基于四个接触多晶硅间距架构形成的第一多个晶体管。第一记忆体电路至第四记忆体电路分别操作地耦接到多个字线中的四个连续字线。第一记忆体电路至第四记忆体电路中的至少两者操作地耦接到多个位元线对中的第一者。

技术特征:1.一种记忆体阵列,其特征在于,包含:

2.如权利要求1所述的记忆体阵列,其特征在于,其中所述多个记忆体电路的后四个记忆体电路亦耦接到所述四个连续字线,但耦接到所述多个位元线对的一第二位元线对。

3.一种记忆体阵列,其特征在于,包含:

4.如权利要求3所述的记忆体阵列,其特征在于,其中该第一字线至该第四字线分别对应于多行中的四个连续行。

5.如权利要求4所述的记忆体阵列,其特征在于,其中该第一记忆体电路及该第二记忆体电路操作地耦接到一第一位元线对并且该第三记忆体电路及该第四记忆体电路操作地耦接到一第二位元线对,并且其中该第一位元线对及该第二位元线对对应于多列的一者。

6.如权利要求5所述的记忆体阵列,其特征在于,进一步包含:

7.如权利要求6所述的记忆体阵列,其特征在于,其中该第一源极/漏极接触结构与该第一位元线对中的一位元线电气接触,该第二源极/漏极接触结构与该第一位元线对的另一位元线电气接触,该第三源极/漏极接触结构与该第二位元线对的一位元线电气接触,并且该第四源极/漏极接触结构与该第二位元线对的另一位元线电气接触。

8.如权利要求3所述的记忆体阵列,其特征在于,进一步包含:

9.一种记忆体阵列,其特征在于,包含:

10.如权利要求9所述的记忆体阵列,其特征在于,进一步包含:

技术总结揭示了一种记忆体阵列。记忆体阵列包括在基板上方设置的多个记忆体单元。记忆体单元的每一者耦接到多个字线的对应字线及多个位元线对的对应位元线对。耦接到字线的四个连续字线及位元线对的第一位元线对的记忆体单元的前四个沿着单个横向方向在基板上抵靠彼此。技术研发人员:粘逸昕,藤原英弘,林志宇,陈炎辉受保护的技术使用者:台湾积体电路制造股份有限公司技术研发日:20230615技术公布日:2024/5/8本文地址:https://www.jishuxx.com/zhuanli/20240731/184502.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表