单次编程记忆体电路、单次编程记忆体及其操作方法与流程

- 国知局

- 2024-07-31 20:02:00

本发明是有关于一种储存电路及其操作方法,且特别是有关于一种单次编程记忆体电路、单次编程记忆体及其操作方法。

背景技术:

1、传统一晶体管一电阻器(1t1r)的单次编程记忆体,需要较细长的弯曲金属丝及较大的焊垫,以便于熔断,因此,1t1r的单次编程记忆体的面积较大。

2、另外,一晶体管一电容器(1t1c)的单次编程记忆体,需要高电压(即,4~5v)来击穿电容器中氧化层。相似地,一控制晶体管一储存晶体管(1t1t)的单次编程记忆体,亦需要高电压(即,4~5v)来击穿储存晶体管的栅极氧化层。前述高电压远超过晶体管的操作电压,因此,1t1c或1t1t的单次编程记忆体皆需要额外的周边电路来产生高电压。然而,愈高压的周边电路,愈占用面积。

技术实现思路

1、本发明提出一种单次编程记忆体电路、单次编程记忆体及其操作方法,改善先前技术的问题。

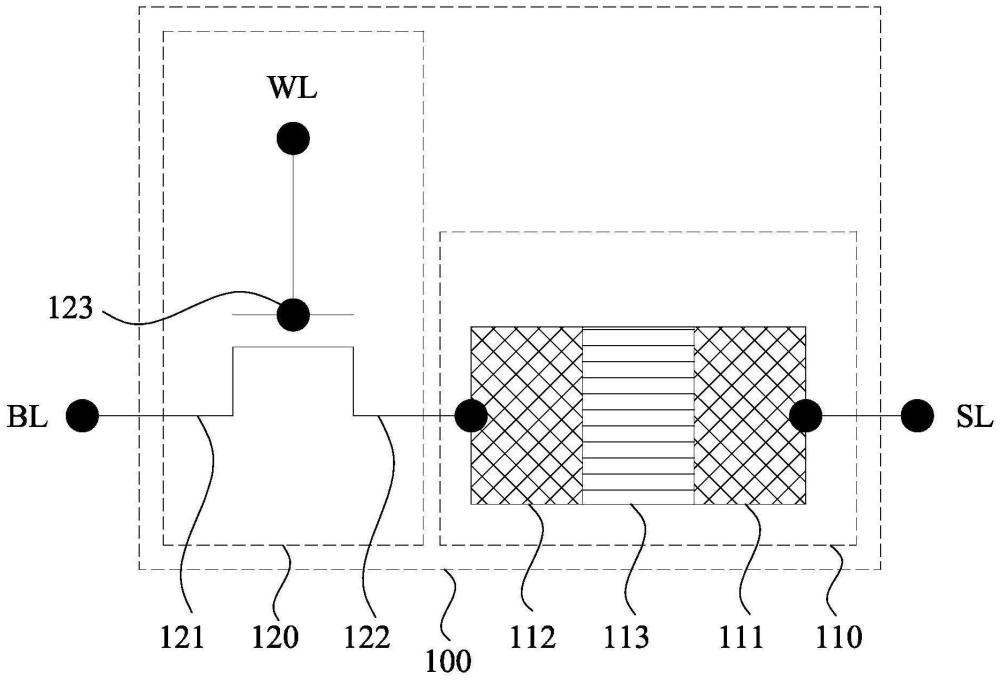

2、在本发明的一些实施例中,本发明所提出的单次编程记忆体包含单次编程二极管以及控制场效晶体管。单次编程二极管的一端电性连接源线。控制场效晶体管包含栅极、第一源极/漏极与第二源极/漏极,控制场效晶体管的栅极电性连接字元线,控制场效晶体管的第一源极/漏极电性连接位元线,控制场效晶体管的第二源极/漏极电性连接单次编程二极管的另一端。

3、在本发明的一些实施例中,控制场效晶体管为n型控制场效晶体管,单次编程二极管是由npn型晶体管所构成,npn型晶体管包含第一n型半导体、p型半导体与第二n型半导体,p型半导体介于第一n型半导体与第二n型半导体之间,第一n型半导体电性连接源线,第二n型半导体电性连接控制场效晶体管的第二源极/漏极。

4、在本发明的一些实施例中,控制场效晶体管为n型控制场效晶体管,单次编程二极管是由nin型晶体管所构成,nin型晶体管包含第一n型半导体、本征(i型)半导体与第二n型半导体,i型半导体介于第一n型半导体与第二n型半导体之间,第一n型半导体电性连接源线,第二n型半导体电性连接控制场效晶体管的第二源极/漏极。

5、在本发明的一些实施例中,控制场效晶体管为p型控制场效晶体管,单次编程二极管是由pnp型晶体管所构成,pnp型晶体管包含第一p型半导体、n型半导体与第二p型半导体,n型半导体介于第一p型半导体与第二p型半导体之间,第一p型半导体电性连接源线,第二p型半导体电性连接控制场效晶体管的第二源极/漏极。

6、在本发明的一些实施例中,控制场效晶体管为p型控制场效晶体管,单次编程二极管是由pip型晶体管所构成,pip型晶体管包含第一p型半导体、本征(i型)半导体与第二p型半导体,i型半导体介于第一p型半导体与第二p型半导体之间,第一p型半导体电性连接源线,第二p型半导体电性连接控制场效晶体管的第二源极/漏极。

7、在本发明的一些实施例中,控制场效晶体管为n型控制场效晶体管,单次编程二极管是由栅极浮接的n型场效晶体管所构成,栅极浮接的n型场效晶体管的两n型源极/漏极分别电性连接控制场效晶体管的第二源极/漏极与源线。

8、在本发明的一些实施例中,控制场效晶体管为p型控制场效晶体管,单次编程二极管是由栅极浮接的p型场效晶体管所构成,栅极浮接的p型场效晶体管的两p型源极/漏极分别电性连接控制场效晶体管的第二源极/漏极与源线。

9、在本发明的一些实施例中,当控制场效晶体管受字元线的控制电压而导通时,位元线的编程电压让单次编程二极管发生雪崩崩溃(avalanche breakdown),从而形成单次编程二极管的已编程状态。

10、在本发明的一些实施例中,本发明所提出的单次编程记忆体电路包含多个记忆体单元,排列成阵列。每一记忆体单元包含单次编程记忆体,单次编程记忆体包含单次编程二极管以及控制场效晶体管。单次编程二极管的一端电性连接源线。控制场效晶体管包含栅极、第一源极/漏极与第二源极/漏极,控制场效晶体管的栅极电性连接字元线,控制场效晶体管的第一源极/漏极电性连接位元线,控制场效晶体管的第二源极/漏极电性连接单次编程二极管的另一端。

11、在本发明的一些实施例中,每一记忆体单元包含另一单次编程记忆体,该另一单次编程记忆体包含另一控制场效晶体管以及另一单次编程二极管。所述另一单次编程二极管的一端电性连接源线。所述另一控制场效晶体管包含栅极、第一源极/漏极与第二源极/漏极,所述另一控制场效晶体管的栅极电性连接另一字元线,所述另一控制场效晶体管的第一源极/漏极电性连接位元线,所述另一控制场效晶体管的第二源极/漏极电性连接所述另一单次编程二极管的另一端。

12、在本发明的一些实施例中,本发明所提出的单次编程记忆体的操作方法,单次编程记忆体包含彼此串接的单次编程二极管与控制场效晶体管,操作方法包含以下步骤:于编程单次编程记忆体时,对字元线施予控制电压,对位元线施予编程电压,对源线施予零电压,其中单次编程二极管的一端电性连接源线,控制场效晶体管的栅极电性连接字元线,控制场效晶体管的第一源极/漏极电性连接位元线,控制场效晶体管的第二源极/漏极电性连接单次编程二极管的另一端。

13、在本发明的一些实施例中,控制电压导通控制场效晶体管,编程电压让单次编程二极管发生雪崩崩溃,从而形成单次编程二极管的已编程状态。

14、在本发明的一些实施例中,操作方法更包含:于读取单次编程记忆体时,对字元线施予工作电压,对源线施予零电压,对位元线施予读取电压。

15、在本发明的一些实施例中,读取电压的极性相反于编程电压的极性。

16、综上所述,本发明的技术方案与现有技术相比具有明显的优点和有益效果。本发明的单次编程记忆体为一晶体管一二极管(1t1d)的单次编程记忆体,其所需编程电压较低,稳定性高,且其周边电路的面积相对较小。

17、以下将以实施方式对上述的说明作详细的描述,并对本发明的技术方案提供更进一步的解释。

技术特征:1.一种单次编程记忆体,其特征在于,包含:

2.如权利要求1所述的单次编程记忆体,其特征在于,该控制场效晶体管为一n型控制场效晶体管,该单次编程二极管是由一npn型晶体管所构成,该npn型晶体管包含一第一n型半导体、一p型半导体与一第二n型半导体,该p型半导体介于该第一n型半导体与该第二n型半导体之间,该第一n型半导体电性连接该源线,该第二n型半导体电性连接该控制场效晶体管的该第二源极/漏极。

3.如权利要求1所述的单次编程记忆体,其特征在于,该控制场效晶体管为一n型控制场效晶体管,该单次编程二极管是由一nin型晶体管所构成,该nin型晶体管包含一第一n型半导体、一本征(i型)半导体与一第二n型半导体,该i型半导体介于该第一n型半导体与该第二n型半导体之间,该第一n型半导体电性连接该源线,该第二n型半导体电性连接该控制场效晶体管的该第二源极/漏极。

4.如权利要求1所述的单次编程记忆体,其特征在于,该控制场效晶体管为一p型控制场效晶体管,该单次编程二极管是由一pnp型晶体管所构成,该pnp型晶体管包含一第一p型半导体、一n型半导体与一第二p型半导体,该n型半导体介于该第一p型半导体与该第二p型半导体之间,该第一p型半导体电性连接该源线,该第二p型半导体电性连接该控制场效晶体管的该第二源极/漏极。

5.如权利要求1所述的单次编程记忆体,其特征在于,该控制场效晶体管为一p型控制场效晶体管,该单次编程二极管是由一pip型晶体管所构成,该pip型晶体管包含一第一p型半导体、一本征(i型)半导体与一第二p型半导体,该i型半导体介于该第一p型半导体与该第二p型半导体之间,该第一p型半导体电性连接该源线,该第二p型半导体电性连接该控制场效晶体管的该第二源极/漏极。

6.如权利要求1所述的单次编程记忆体,其特征在于,该控制场效晶体管为一n型控制场效晶体管,该单次编程二极管是由一栅极浮接的n型场效晶体管所构成,该栅极浮接的n型场效晶体管的两n型源极/漏极分别电性连接该控制场效晶体管的该第二源极/漏极与该源线。

7.如权利要求1所述的单次编程记忆体,其特征在于,该控制场效晶体管为一p型控制场效晶体管,该单次编程二极管是由一栅极浮接的p型场效晶体管所构成,该栅极浮接的p型场效晶体管的两p型源极/漏极分别电性连接该控制场效晶体管的该第二源极/漏极与该源线。

8.如权利要求1所述的单次编程记忆体,其特征在于,当该控制场效晶体管受该字元线的一控制电压而导通时,该位元线的一编程电压让该单次编程二极管发生一雪崩崩溃(avalanche breakdown),从而形成该单次编程二极管的已编程状态。

9.一种单次编程记忆体电路,其特征在于,包含:

10.如权利要求9所述的单次编程记忆体电路,其特征在于,每一该记忆体单元包含一另一单次编程记忆体,该另一单次编程记忆体包含:

11.一种单次编程记忆体的操作方法,该单次编程记忆体包含彼此串接的一单次编程二极管与一控制场效晶体管,其特征在于,该操作方法包含以下步骤:

12.如权利要求11所述的操作方法,其特征在于,该控制电压导通该控制场效晶体管,该编程电压让该单次编程二极管发生一雪崩崩溃,从而形成该单次编程二极管的已编程状态。

13.如权利要求11所述的操作方法,其特征在于,更包含:

14.如权利要求13所述的操作方法,其特征在于,该读取电压的极性相反于该编程电压的极性。

技术总结本发明提出一种单次编程记忆体电路、单次编程记忆体及其操作方法。单次编程记忆体包含单次编程二极管以及控制场效晶体管。单次编程二极管的一端电性连接源线。控制场效晶体管包含栅极、第一源极/漏极与第二源极/漏极,控制场效晶体管的栅极电性连接字元线,控制场效晶体管的第一源极/漏极电性连接位元线,控制场效晶体管的第二源极/漏极电性连接单次编程二极管的另一端。本发明的单次编程记忆体所需编程电压较低,稳定性高,且其周边电路的面积相对较小。技术研发人员:谢易叡受保护的技术使用者:谢易叡技术研发日:技术公布日:2024/6/20本文地址:https://www.jishuxx.com/zhuanli/20240731/185124.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。