存储器信号检错纠错装置的制作方法

- 国知局

- 2024-07-31 20:01:57

本技术涉及存储器信号校验纠错,特别涉及一种存储器信号检错纠错装置。

背景技术:

1、随着工艺的不断提升和需求的不断增加,存储器接口频率越来越高、存储器接口通道数量越来越多,存储器接口传输稳定性面临更多的挑战。基于存储器产生的信号错误率受外部和内部多重因素的影响,包括一些恶劣的环境或者物理结构上的老化,使得存储器可能发生内部信号翻转造成的信号错误问题,还包括存储单元本身相关,或者pcb的板级设计、电源完整性、信号完整性等,因此存储器信号校验与纠错具有重要意义,如何有效降低存储器信号错误率是待解决的问题之一。

技术实现思路

1、本实用新型旨在至少解决现有技术中存在的技术问题之一。为此,本实用新型提出一种存储器信号检错纠错装置,能够保证信号传输速率的前提下有效降低存储器信号的错误率。

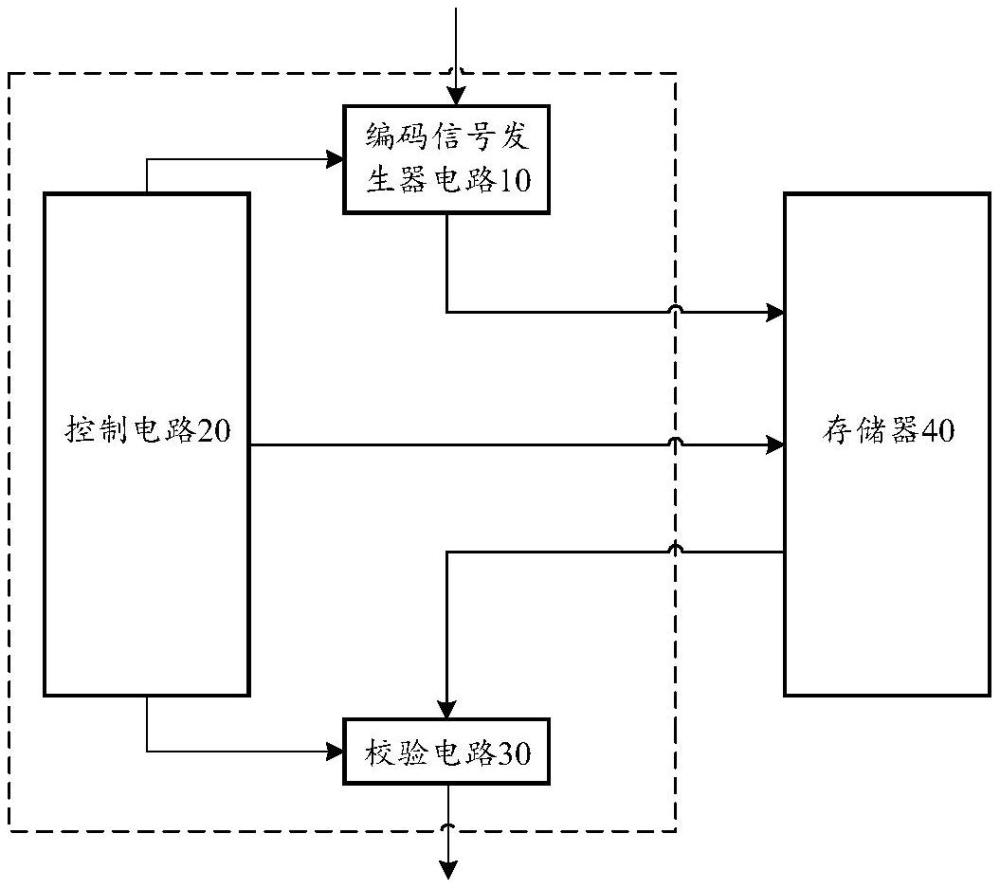

2、根据本实用新型实施例的存储器信号检错纠错装置,包括:存储器、编码信号发生器电路、校验电路、控制电路;所述存储器与所述编码信号发生器电路输出端连接;所述存储器与所述校验电路输入端连接;所述控制电路与所述存储器、所述编码信号发生器电路、所述校验电路至少一个连接。

3、根据本实用新型的一些实施例,所述控制电路包括:检错纠错寄存器、读诊断寄存器、写诊断寄存器、校验码测试寄存器。

4、根据本实用新型的一些实施例,所述检错纠错寄存器与所述校验电路的输入端连接,用于控制所述校验电路的开启、关闭。

5、根据本实用新型的一些实施例,所述编码信号发生器电路、所述写诊断寄存器与所述存储器的输入端连接,用于编码信号的存储。

6、根据本实用新型的一些实施例,所述校验码测试寄存器、所述编码信号发生器电路、所述写诊断寄存器与所述存储器的输入端连接,用于编码测试信号的存储。

7、根据本实用新型的一些实施例,还包括:系统总线接口和外围总线接口,其中,所述编码信号发生器电路的输入端与所述系统总线接口、所述外围总线接口至少一个接口连接;所述校验电路的输出端与所述系统总线接口、所述外围总线接口至少一个接口连接。

8、根据本实用新型实施例的存储器信号检错纠错装置,至少具有如下有益效果:通过校验电路对原始信号进行二次编码产生第二编码信号,通过对第二编码信号的纠错、可适当修正第一编码信号被纠错后仍然存在错误的信号位,从而进一步提高信号的纠错能力。

9、本实用新型的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本实用新型的实践了解到。

技术特征:1.一种存储器信号检错纠错装置,其特征在于,包括:存储器(40)、编码信号发生器电路(10)、控制电路(20)、校验电路(30);

2.根据权利要求1所述的存储器信号检错纠错装置,其特征在于,所述检错纠错寄存器(21)与所述校验电路(30)的输入端连接。

3.根据权利要求1所述的存储器信号检错纠错装置,其特征在于,所述编码信号发生器电路(10)、所述写诊断寄存器(24)至少一个与所述存储器(40)的输入端连接。

4.根据权利要求1所述的存储器信号检错纠错装置,其特征在于,所述校验码测试寄存器(23)、所述编码信号发生器电路(10)、所述写诊断寄存器(24)至少一个与所述存储器(40)的输入端连接。

5.根据权利要求1所述的存储器信号检错纠错装置,其特征在于,该装置还包括系统总线接口(60)和外围总线接口(70),所述编码信号发生器电路(10)的输入端与所述系统总线接口(60)、所述外围总线接口(70)至少一个接口连接;所述校验电路(30)的输出端与所述系统总线接口(60)、所述外围总线接口(70)至少一个接口连接。

技术总结本技术涉及存储器信号校验纠错技术领域,公开了一种存储器信号检错纠错装置,包括:存储器、编码信号发生器电路、校验电路、控制电路;存储器与所述编码信号发生器电路输出端连接;存储器与校验电路输入端连接;控制电路与存储器、编码信号发生器电路、校验电路至少一个连接。本技术至少具有以下有益效果:能够保证信号传输速率的前提下,有效降低存储器信号错误率。技术研发人员:颜军,赵厉,韩俊受保护的技术使用者:珠海航宇微科技股份有限公司技术研发日:20230908技术公布日:2024/6/20本文地址:https://www.jishuxx.com/zhuanli/20240731/185121.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。