控制电路、存储器的读取方法、存储器及电子设备与流程

- 国知局

- 2024-07-31 20:02:28

本技术实施例涉及存储,尤其涉及一种控制电路、存储器的读取方法、存储器及电子设备。

背景技术:

1、随着存储技术的进步,计算机闪存设备(nand)的应用越来越广,如可应用于手机、电脑等设备。

2、在nand存储器中,与一条字线耦合的存储单元为一个物理页,可以根据存储单元存储数据的比特位个数,将一个物理页划分为多个逻辑页(page),其中,划分逻辑页的数量与存储单元存储数据的比特位个数相等。例如,存储单元为三级单元(triple-level cell,tlc)闪存颗粒时,每个存储单元存储的数据有三个比特位,相应的可以将一个物理页划分为三个逻辑页,其中包括低逻辑页(lower page,lp)、中逻辑页(middle page,mp)和高逻辑页(upper page,up)。

3、其中,每个逻辑页对应有不同的读取电压,在对nand存储器的任一存储单元层进行数据读取时,可以按照各逻辑页的顺序,向存储单元层耦合的字线(word line,wl)施加各逻辑页对应的读取电压。在每次向wl施加任一逻辑页对应的读取电压后,可根据各位线(bit line,bl)在不同读取电压下的导通状态,确定存储单元存储的相应比特位的数据,并根据相应比特位的数据确定读取结果。但是,现有技术存在读取时间长的问题。

技术实现思路

1、本技术实施例提供一种控制电路、存储器的读取方法、存储器及电子设备,解决了现有技术中存储器读取时间长的问题。

2、为达到上述目的,本技术实施例采用如下技术方案:

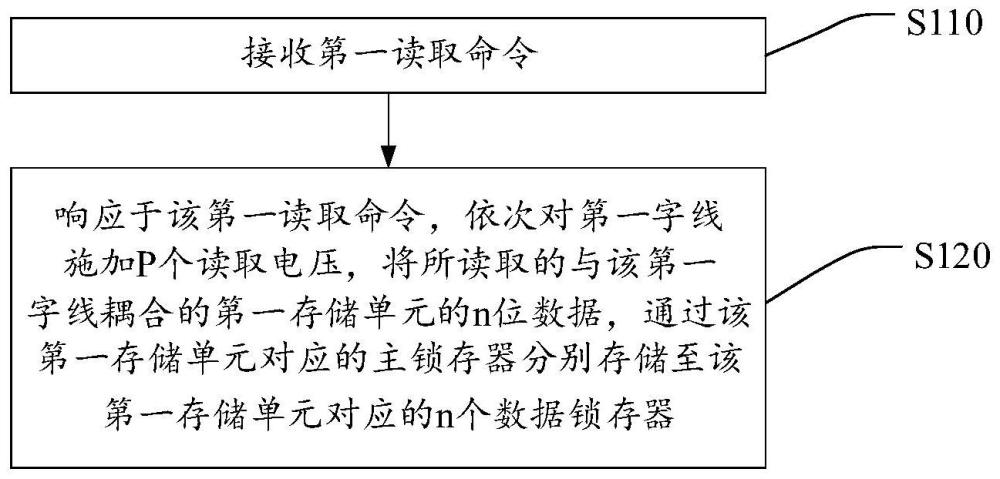

3、第一方面,提供一种控制电路,该控制电路与存储单元阵列和多个页缓冲器耦合,该存储单元阵列包括多个存储单元、以及与该存储单元耦合的字线和位线,每个该存储单元被配置为存储m位数据,m为大于1的整数,该多个页缓冲器的一个页缓冲器与一条位线耦合,该一个页缓冲器包括一个主锁存器和多个数据锁存器。该控制电路被配置为:接收第一读取命令。响应于该第一读取命令,依次对第一字线施加p个读取电压,p小于或等于2m-1,将所读取的与该第一字线耦合的第一存储单元的n位数据,通过该第一存储单元对应的主锁存器分别存储至该第一存储单元对应的n个数据锁存器,n大于或等于2,n小于或等于m。

4、上述技术方案中,通过将第一存储单元的n位数据分别存储至该第一存储单元对应的n个数据锁存器中,为响应于一次读取命令对n位数据进行读取提供基础。并且,由于该控制电路被配置为响应于一次读取命令对该第一存储单元的n位数据进行读取,并存储至n个数据锁存器,即读取多个逻辑页对应一次读取命令,相比于传统的读取方法中,读取多个逻辑页对应多次命令,本技术实施例提供的控制电路可以减少读取命令的发送次数,从而节省读取时间。

5、在第一方面的一种可能的实现方式中,p等于2m-1,n等于m。上述可能的实现方式中,控制电路,被配置为响应于一次读取命令对该第一存储单元的m位数据进行读取,并存储至m个数据锁存器。一次读取命令读取所有逻辑页,可以在最大程度上减少读取命令发送的次数,节省读取时间。

6、在第一方面的一种可能的实现方式中,该p个读取电压依次增大或依次减小。上述可能的实现方式中,对第一字线施加的读取电压是依次增大或依次减小的,相比于传统读取方法,本方案相邻两次施加的读取电压之间的电压差较小。因此,每次施加读取电压时,电压爬升或下降更快,从而节省读取时间。

7、在第一方面的一种可能的实现方式中,p小于2m-1,n小于m,该控制电路还被配置为:接收第二读取命令。响应于该第二读取命令,依次对该第一字线施加2m-1-p个读取电压,将所读取的该第一存储单元的m-n位数据,通过该第一存储单元对应的主锁存器分别存储至该第一存储单元对应的m-n个数据锁存器。上述可能的实现方式中,控制电路,被配置为响应于多次读取命令对该第一存储单元的m位数据进行读取,并存储至多个数据锁存器。一次读取命令读取部分逻辑页中的多个逻辑页,可以适应更多使用场景,并节省读取时间。

8、在第一方面的一种可能的实现方式中,同一读取命令下对应的多个读取电压是连续施加的。上述可能的实现方式中,控制电路响应于一次读取命令就可以执行对多个逻辑页的读取操作,且执行对多个逻辑页的读取操作之间无需对选中的字线施加预脉冲电压和恢复脉冲电压。因此,可以减少施加预脉冲电压和恢复脉冲电压的次数,以减少读取时间。

9、在第一方面的一种可能的实现方式中,每个读取命令对应的第一个读取电压小于第一预设值,该每个读取命令对应的最后一个读取电压小于该第一预设值,该控制电路还被配置为:在接收该读取命令后、对该第一字线施加该第一个读取电压之前,对该第一字线施加预脉冲电压,该预脉冲电压的最大值大于或等于该第一预设值。在对该第一字线施加该最后一个读取电压之后,对该第一字线施加恢复脉冲电压,该恢复脉冲电压的最大值大于或等于该第一预设值。上述可能的实现方式中,每个读取命令对应的第一个读取电压小于第一预设值,即每个读取命令对应的第一个读取电压不能起到清理沟道、解决hci问题的作用。此时,需要在接收该读取命令后、对该第一字线施加该第一个读取电压之前,对该第一字线施加预脉冲电压,以清理沟道、解决hci问题。该每个读取命令对应的最后一个读取电压小于该第一预设值,即每个读取命令对应的最后一个读取电压不能起到清理沟道、解决hci问题的作用。此时,需要在对该第一字线施加该最后一个读取电压之后,对该第一字线施加恢复脉冲电压,以清理沟道、解决hci问题。

10、在第一方面的一种可能的实现方式中,至少一个读取命令对应的第一个读取电压大于或等于第一预设值,该控制电路还被配置为:在接收该至少一个读取命令后,直接对该第一字线施加该第一个读取电压。上述可能的实现方式中,该至少一个读取命令对应的第一个读取电压大于或等于第一预设值,即该至少一个读取命令对应的第一个读取电压可以起到清理沟道、解决hci问题的作用。此时,无需在接收该至少一个读取命令后、对该第一字线施加该第一个读取电压之前,对该第一字线施加预脉冲电压。因此,可以在接收该至少一个读取命令后,直接对该第一字线施加该第一个读取电压。如此,可以进一步减少施加预脉冲电压的次数,进一步节省读取时间。

11、在第一方面的一种可能的实现方式中,至少一个读取命令对应的最后一个读取电压大于或等于第一预设值,该控制电路还被配置为:在对该第一字线施加该最后一个读取电压后,不向该第一字线施加恢复脉冲电压。上述可能的实现方式中,该至少一个读取命令对应的最后一个读取电压大于或等于第一预设值,即该至少一个读取命令对应的最后一个读取电压可以起到清理沟道、解决hci问题的作用。此时,无需在对该第一字线施加该最后一个读取电压之后,对该第一字线施加恢复脉冲电压。如此,可以进一步减少施加恢复脉冲电压的次数,进一步节省读取时间。

12、在第一方面的一种可能的实现方式中,该n个数据锁存器包括编程操作所使用的锁存器,该编程操作所使用的锁存器与读取操作所使用的锁存器耦合。或者,该n个数据锁存器包括读取操作所使用的锁存器和编程操作所使用的锁存器。该控制电路还被配置为:通过该读取操作所使用的锁存器读出该编程操作所使用的锁存器的数据。

13、上述可能的实现方式中,一方面,使用编程操作所使用的锁存器进行读取操作,复用存储器中原有的编程操作所使用的锁存器,无需增加电路面积,节约成本。另一方面,通过读取操作所使用的锁存器读出编程操作所使用的锁存器的数据,无需更改用户协议。

14、在第一方面的一种可能的实现方式中,该控制电路还被配置为:在施加每个读取电压之前,对该第一字线耦合的第二存储单元对应的位线施加预充电电压,该第二存储单元为与该第一字线耦合的部分存储单元。其中,该第一字线耦合的除该第二存储单元以外的存储单元对应的位线,不施加该预充电电压。上述可能的实现方式中,在施加每个读取电压之前,对该第一字线耦合的第二存储单元对应的位线施加预充电电压,该第一字线耦合的除该第二存储单元以外的存储单元对应的位线,不施加该预充电电压。一方面,可以使未被读出的存储单元在读取电压大于阈值电压时可以导通,并且使已被读出的存储单元不受影响。另一方面,可以使每次施加读取电压时导通的存储单元的数量减少,从而使共源线电流减小,减少共源线噪声的影响。

15、在第一方面的一种可能的实现方式中,该p个读取电压中不同大小的读取电压的施加次数为1。上述可能的实现方式中,由于本技术实施例提供的控制电路在执行读取操作时可以减少共源线噪声的影响,因此,p个读取电压中,不同大小的读取电压的施加次数为1,同样的读取电压无需施加2次,节省读取时间。

16、第二方面,提供一种存储器的读取方法,该存储器包括耦合的存储单元阵列和多个页缓冲器,该存储单元阵列包括多个存储单元、以及与该存储单元耦合的字线和位线,每个该存储单元被配置为存储m位数据,m为大于1的整数,该多个页缓冲器的一个页缓冲器与一条位线耦合,该一个页缓冲器包括一个主锁存器和多个数据锁存器;该方法包括:接收第一读取命令。响应于该第一读取命令,依次对第一字线施加p个读取电压,p小于或等于2m-1,将所读取的与该第一字线耦合的第一存储单元的n位数据,通过该第一存储单元对应的主锁存器分别存储至该第一存储单元对应的n个数据锁存器,n大于或等于2,n小于或等于m。

17、在第二方面的一种可能的实现方式中,p等于2m-1,n等于m。

18、在第二方面的一种可能的实现方式中,该p个读取电压依次增大或依次减小。

19、在第二方面的一种可能的实现方式中,p小于2m-1,n小于m,该方法还包括:接收第二读取命令。响应于该第二读取命令,依次对该第一字线施加2m-1-p个读取电压,将所读取的该第一存储单元的m-n位数据,通过该第一存储单元对应的主锁存器分别存储至该第一存储单元对应的m-n个数据锁存器。

20、在第二方面的一种可能的实现方式中,同一读取命令下对应的多个读取电压是连续施加的。

21、在第二方面的一种可能的实现方式中,每个读取命令对应的第一个读取电压小于第一预设值,该每个读取命令对应的最后一个读取电压小于该第一预设值,该方法还包括:在接收该读取命令后、对该第一字线施加该第一个读取电压之前,对该第一字线施加预脉冲电压,该预脉冲电压的最大值大于或等于该第一预设值。在对该第一字线施加该最后一个读取电压之后,对该第一字线施加恢复脉冲电压,该恢复脉冲电压的最大值大于或等于该第一预设值。

22、在第二方面的一种可能的实现方式中,至少一个读取命令对应的第一个读取电压大于或等于第一预设值,该方法还包括:在接收该至少一个读取命令后,直接对该第一字线施加该第一个读取电压。

23、在第二方面的一种可能的实现方式中,至少一个读取命令对应的最后一个读取电压大于或等于第一预设值,该方法还包括:在对该第一字线施加该最后一个读取电压后,不向该第一字线施加恢复脉冲电压。

24、在第二方面的一种可能的实现方式中,该n个数据锁存器包括编程操作所使用的锁存器,该编程操作所使用的锁存器与读取操作所使用的锁存器耦合;或者,该n个数据锁存器包括读取操作所使用的锁存器和编程操作所使用的锁存器。该方法还包括:通过该读取操作所使用的锁存器读出该编程操作所使用的锁存器的数据。

25、在第二方面的一种可能的实现方式中,该方法还包括:在施加每个读取电压之前,对该第一字线耦合的第二存储单元对应的位线施加预充电电压,该第二存储单元为与该第一字线耦合的部分存储单元。其中,该第一字线耦合的除该第二存储单元以外的存储单元对应的位线,不施加该预充电电压。

26、在第二方面的一种可能的实现方式中,该p个读取电压中不同大小的读取电压的施加次数为1。

27、第三方面,提供一种存储器,该存储器包括第一方面或者第一方面的任一种可能的实现方式所提供的控制电路。

28、第四方面,提供一种电子设备,该电子设备包括处理器和第三方面的存储器。

29、本技术的又一方面,提供一种计算机程序产品,当计算机程序产品在计算机上运行时,使得计算机执行第二方面或者第二方面的任一种可能的实现方式所提供的存储器的读取方法。

30、可以理解地,上述提供的任一种存储器的读取方法、存储器、电子设备或者计算机程序产品均应用于上述控制电路或与通过该控制电路以实现对应的功能。因此,其所能达到的有益效果可参考上文所提供的对应的控制电路中的有益效果,此处不再赘述。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185178.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表