基于ONFI协议的数据读写电路及闪存读写控制器的制作方法

- 国知局

- 2024-07-31 20:09:26

本技术涉及闪存数据读写,尤其涉及一种基于onfi协议的数据读写电路及闪存读写控制器。

背景技术:

1、目前绝大多数的数据传输协议均基于osi(open system interconnectionreference model)七层模型或osi简化模型进行各层功能/接口的定义。ssd主控架构也不例外,其前端实现sata(serial advanced technology attachment)和pcie(peripheralcomponent interconnect express)等主机接口协议栈,后端则实现颗粒的数据传输协议栈。目前主流的颗粒物理接口协议为onfi(onfi,open nand flash interface)和toggle(以ddr为基础指定的flash接口标准),二者均基于并行接口nand互操作性标准开发,所以它们具有较强的一致性。由于toggle协议是闭源的,所以目前的主要设计参考为onfi协议。

2、其中,onfi接口的时序产生难点主要在于nv-ddr(non-violate double datarate)模式下写时序的产生以及读数据时对输入数据的采样。图1所示为nv-ddr写数据传输时序,图2为nv-ddr读数据传输时序。可以看到,dqs信号(data strobe,数据选取脉冲)在ddr模式的数据读写过程中起到重要作用,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并在两个边沿可以分别采样一个数据,所以在不增加时钟频率的情况下可以提高一倍的传输速率。

3、然而,目前一般采用一个2倍频的时钟用来产生dqs和dq信号,此时在控制器内部需要增加一个二倍频的时钟,这将导致物理层模块(phy)上的时序更加严格,并且将占用一个独立的时钟域,使得后端实现需要付出更大的努力,从而使得成本增加。

技术实现思路

1、有鉴于此,本技术实施例提供一种基于onfi协议的数据读写电路及闪存读写控制器。

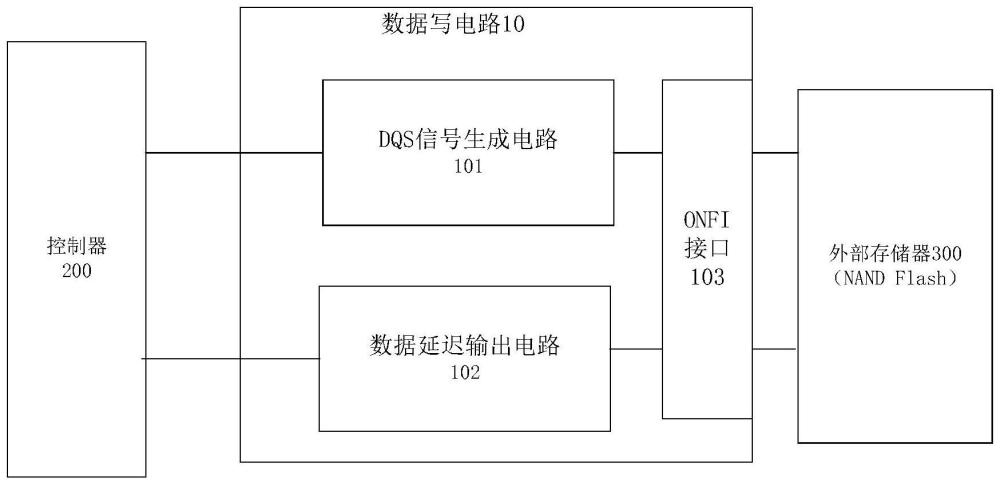

2、第一方面,本技术实施例提供一种基于onfi协议的数据写电路,包括:

3、onfi接口,用于连接外部存储器;

4、dqs信号生成电路,包括一写数据延迟锁定环和第一时钟门控单元,其中,所述写数据延迟锁定环用于对控制器输入的初始时钟信号进行预设相位延迟,以输出第一延迟时钟信号;所述第一时钟门控单元用于对所述第一延迟时钟信号进行截取,以产生符合onfi时序的dqs信号;

5、数据延迟输出电路,与所述onfi接口连接,用于接收所述控制器输入的预设位数的待写入数据,将所述待写入数据移相后并在所述dqs信号时序下依次写入所述onfi接口连接的外部存储器中。

6、在一些实施例中,所述数据延迟输出电路还包括,依次连接的第二组寄存器、多路选择器和第一延迟线;

7、所述第二组寄存器用于分别接收所述控制器输入的高八位数据和低八位数据,并在所述初始时钟信号下利用所述多路选择器进行数据选通;

8、所述第一延迟线用于对所述选通输出的数据信号进行相位延迟再传输至所述onfi接口,以使所述onfi接口在所述dqs信号的上升沿和下降沿,分别将所述数据信号中的所述低八位数据和所述高八位数据依次写入所述外部存储器中。

9、在一些实施例中,所述dqs信号生成电路还包括,依次连接的第一组寄存器和第一或门;

10、所述第一组寄存器用于在所述初始时钟信号下接收所述控制器输入的一对差分控制信号,其中一个所述控制信号作为所述第一时钟门控单元的使能信号;

11、所述第一时钟门控单元用于通过所述使能信号对所述第一延迟时钟信号进行截取,并将截取输出的信号与另一个所述控制信号输入所述第一或门进行运算,以产生符合onfi时序的dqs信号。

12、在一些实施例中,所述dqs信号生成电路还用于,当需要进行写数据时,根据所述控制器输入的复位信号对所述写数据延迟锁定环进行复位及90度相位延迟的锁定。

13、第二方面,本技术实施例提供一种基于onfi协议的数据读电路,包括:

14、onfi接口,用于连接外部存储器;

15、读数据信号产生电路,包括第二时钟门控单元,其中,所述第二时钟门控单元用于对控制器输入的初始时钟信号进行截取,以生成所述onfi接口的读数据使能信号;

16、dqs信号采样电路,包括一读数据延迟锁定环,所述读数据延迟锁定环与所述onfi接口连接,所述dqs信号采样电路用于在所述读数据使能信号有效时,通过所述onfi接口从所述外部存储器中采样初始的dqs差分信号,并通过所述读数据延迟锁定环进行相位延迟,以得到调整后的dqs信号;

17、数据输入采样电路,与所述onfi接口连接,用于通过所述onfi接口从所述外部存储器中采样需要读取的数据,并在所述dqs信号的上升沿和下降沿下,将读取到的数据按照高位和低位分别缓存到不同的数据缓存器中。

18、在一些实施例中,所述读数据信号为差分信号;所述读数据信号产生电路还包括,第三组寄存器和第二或门;

19、所述第三组寄存器用于在所述初始时钟信号下接收所述控制器输入的一对差分控制信号,其中一个所述控制信号作为所述第二时钟门控单元的使能信号;

20、所述第二时钟门控单元用于通过所述使能信号对所述初始时钟信号进行截取,并将截取输出的信号与另一个所述控制信号输入所述第二或门进行运算,以生成所述onfi接口的读数据使能信号。

21、在一些实施例中,所述数据缓存器包括高八位fifo和低八位fifo,其中,所述高八位fifo和所述低八位fifo的写时钟端均与所述读数据延迟锁定环的输出端连接;

22、所述高八位fifo用于在所述dqs信号的上升沿进行数据采样,以及所述低八位fifo用于在所述dqs信号的下降沿进行数据采样。

23、在一些实施例中,所述数据输入采样电路还包括第二延迟线,所述第二延迟线用于对通过所述onfi接口从所述外部存储器中采样到的数据信号进行移相,然后输入至所述高八位fifo或所述低八位fifo。

24、在一些实施例中,所述dqs信号采样电路还用于,当需要进行读数据时,根据所述控制器输入的复位信号对所述读数据延迟锁定环进行复位及90度相位延迟的锁定。

25、第三方面,本技术实施例提供一种闪存读写控制器,所述闪存读写控制器包括所述的基于onfi协议的数据读电路和数据写电路。

26、本技术的实施例具有如下有益效果:

27、本技术提出一种基于onfi协议的数据写电路和数据读电路,其中,通过基于写数据延迟锁定环和第一时钟门控单元来dqs信号生成数据写电路,并结合数据延迟输出电路来实现基于onfi协议的外部存储器300的数据写操作,可以实现利用单个时钟发送dqs和dq信号的电路结构,减少了系统中时钟域的需求,不使用二倍频时钟也使得phy的约束更为宽松,降低了dqs路径的电路复杂程度和约束难度等。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185362.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表